现代微处理器是世界上最复杂的系统之一,但其核心是一个非常简单的,那就是我们认为非常美丽的装置——晶体管。今天在微处理器中有数十亿个晶体管,它们几乎完全相同。因此,提高这些晶体管的性能和密度是持续制造高性能微处理器最简单的方法,它们所支持的计算器也能更好地工作。

即使现在它已经(几乎)结束了,但这就是摩尔定律背后的前提。正如前面所说,发展到今天,为微处理器制造更小、更好的晶体管变得越来越困难,且价格也越来越昂贵了。现在只有英特尔,三星和台积电这三家公司才能在继续往更小节点推进。他们目前都在制造相当于所谓的7纳米节点的集成电路。但这个冠上了摩尔定律早期遗迹的名称不再具有明确的物理意义,但它反映了集成电路上的特征和器件小型化的程度。

7纳米是目前最前沿的技术。但三星和台积电在4月宣布,他们开始转向下一个节点——5纳米。三星还有一些额外的消息:它们认为这个行业近十年来一直使用的那种晶体管已经走到了尽头。他们即正在为期2020年左右推出的下一个节点——3 nm开发一种全新设计的晶体管。

这种晶体管设计有各种各样的名称:gate-all-around、multibridge channel和nanobeam 。但在研究界我们一直称它为nanosheet。这个名字不是很重要。重要的是,这种设计不仅仅是逻辑芯片的下一代晶体管,但它也可能是最后一个。

尽管形状和材料已发生变化,但金属氧化物半导体场效应晶体管或MOSFET(微处理器中使用的晶体管类型)自1959年发明以来一直拥有相同的基本结构:栅极堆叠(gate stack)、沟道区域(channel region),源电极(source electrode)和漏电极(drain electrode)。在这些器件的原始形式中,源极,漏极和沟道基本上是掺杂有其他元素原子的硅区域,这样就以产生具有大量移动负电荷(n型)的区域或具有大量移动正电荷(p型)的区域。对于构成当今计算机芯片的CMOS技术,您需要这两种类型的晶体管。

MOSFET的栅极堆叠位于沟道区域的正上方。今天,栅极堆叠由金属(用于栅电极)制成,位于介电材料层的顶上。该组合设计用于将电场投射到晶体管沟道区域中,同时防止电荷泄漏。

向栅极(相对于源极)施加足够大的电压,就会在电介质和硅之间的界面附近产生一层移动电荷载流子。一旦该层完全桥接(bridges)从源极到漏极的跨度,电流就可以流过。将栅极电压降低到接近零,然后“挤压”导电通路关闭。

当然,为了使电流通过沟道从源极流到漏极,您首先需要一个电压。随着晶体管结构越来越小,这种电压的影响最终导致晶体管迎来了历史上最大的转变。

这是因为源极-漏极电压可以在电极之间产生其自己的导电区域。随着每个新一代晶体管产生的沟道区域变得越来越短,漏极电压的影响变得越来越大,充电的时候电荷也会泄漏。病在栅极附近区域下方“躲避”。这样引致的结果是晶体管从未完全关闭、浪费电力并产生热量。

为了阻止不需要的电荷流动,必须使沟道区域更薄,限制电荷通过的路径。并且在栅极方面需要在更多侧面环绕通道。因此,今天的晶体管FinFET就诞生了。这是一种沟道区域基本上在其侧面tilted up得设计,这样就接以在源极和漏极之间形成纤薄的Fin,为电流提供更宽的通路。然后将栅极和电介质覆盖在Fin上,在三面而不是仅一面上围绕它。

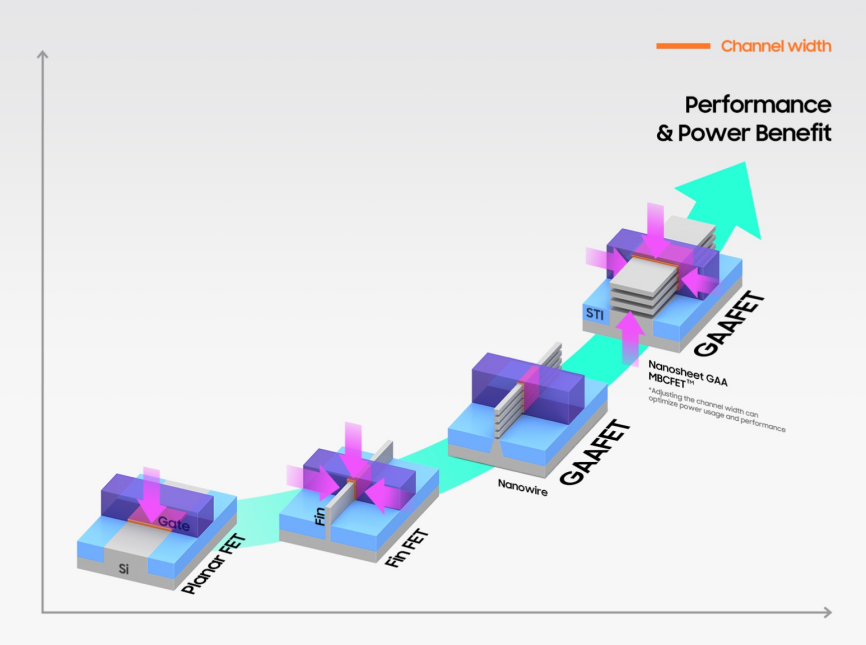

FET的演变

自1959年推出以来,场效应晶体管主要内置于硅平面中。但为了更好地控制其漏电电流,这就推动了FinFET的诞生,而现在我们即将迈入stacked sheets的时代。

毫无疑问,FinFET取得了巨大成功。虽然它是十多年前发明的,但FinFET 到2011年才首次在英特尔推出 22纳米节点上实现,后来由三星,台积电也陆续推出了相应工艺。从那以后,它一直是摩尔定律缩放最后阶段中最先进的硅逻辑的主力,但所有好事都会结束。

对于3-nm节点, FinFET无法胜任任务。我们在十多年以前就看到这种情况,其他人也是如此。

虽然很好,但FinFET有其问题。

首先,它引入了一个设计限制,而在旧“平面”晶体管上其实原本不是一个问题。要了解这个,您必须了解晶体管的速度、功耗、制造复杂性和成本之间总是存在权衡(trade-off)。这种权衡与沟道的宽度有很大关系,在设备设计圈中我们将其称为W eff。更宽的宽度意味着您可以更快地驱动更多电流并开关晶体管。但它也需要更复杂,更昂贵的制造工艺。

在平面设备中,您只需通过调整通道的几何形状即可进行权衡。但是Fin不允许那么多的灵活性。连接晶体管以形成电路的金属互连构建在晶体管自身上方的层中。因此,在不干扰互连层的情况下,晶体管鳍片的高度实际上不会变化很大——这就相当于平面设计中的宽度。今天,芯片设计人员通过制造具有多个鳍片的单个晶体管来解决这个问题。

FinFET的另一个缺点是其栅极仅在三个侧面围绕矩形硅鳍片,而底部侧面连接到硅的主体。当晶体管关闭时,这允许一些漏电流流动。许多研究人员推断,要获得对通道区域的最终控制,需要将栅极完全包围。

自1990年以来,研究人员一直将这一想把这个设想归结为合乎逻辑的结论。也就是在那一年,研究人员报告了第一个具有完全围绕沟道区域的栅极硅器件。从那时起,一代又一代的研究人员开始研究所谓的gate-all-around设备。到2003年,寻求最大程度减少泄漏的研究人员将沟道区域变成了一条狭窄的纳米线,桥接了源极和漏极,并被四周的栅极包围。

那么为什么不用gate-all-around纳米线来做最新的晶体管呢?答案其实是一样的:也与通道宽度有关。因为细线提供很少的电子逃逸机会,从而在晶体管关闭时保持晶体管关闭。但是当晶体管导通时,它也几乎没有电子流动的空间,从而限制了电流并减缓了开关。

通过将纳米线堆叠在一起,您可以获得更多的Weff,从而获得更大的电流。三星工程师在2004年推出了这种配置版本,称为多桥通道(multibridge channel)FET。但它有一些局限性。例如,与FinFET的鳍片一样,叠层不能太高或者会干扰互连层。另一方面,每个额外的纳米线都会增加器件的电容,从而降低晶体管的开关速度。最后,由于制造非常窄的纳米线的复杂性,它们经常在边缘处变得粗糙,而这种表面粗糙度会妨碍电荷载体的速度。

2006年,在法国CEA-Leti与我们一起工作的工程师(恩斯特)展示了一个更好的主意。他们使用一叠薄硅片代替使用一堆纳米线桥接源极和漏极。我们的想法是在较小的晶体管中增加通道的宽度,同时保持对泄漏电流的严格控制,从而提供性能更好,功耗更低的器件。

在我们另一个人(Khare)的指导下,IBM Research在2017年进一步采用了这一概念,表明由堆叠纳米片( stacked nanosheets)制成的晶体管实际上提供的Weff比占用相同芯片面积的FinFET 还多。

但nanosheet 设计提供了一个额外的好处:它恢复了向FinFET过渡中失去的灵活性。因为我们可以将Sheet放宽以增加电流或缩小以限制功耗。IBM Research已经制作了三个堆叠,尺寸范围从8mm到50 nm不等。

如何制作nanosheet ?

制造nanosheet 需要Sacrificial layers,选择性化学蚀刻剂和先进原子级别的精确沉积技术。

你是如何制造nanosheet 晶体管的?考虑到大多数半导体制造工艺从硅的顶部直接切割或从暴露的表面直接填充。Nanosheets 只需要在其他材料层之间去除材料并用金属和电介质填充间隙。

主要技巧是构建所谓的超晶格(superlattice)——一种由两种材料组成的周期性层状晶体。在这种情况下,它是硅和硅锗。研究人员制作了19层的超晶格,但所涉及的机械应力以及电容使得使用了许多不合理的层(ill advised)。在生长适当数量的层之后,我们使用蚀刻硅锗但不对硅做任何影响的选择性化学品去刻蚀,仅留下硅纳米片作为源极和漏极之间的桥。这实际上不是一个新想法; 法国电信和意法半导体的工程师20年前在实验性的“silicon-on-nothin”晶体管上就使用了相同的方法。他们试图通过在晶体管沟道区域下方埋设一层空气来限制短沟道效应的器件。

一旦你构建了硅nanosheet 通道区域,就需要填充间隙,首先用电介质包围通道,然后用金属形成栅极堆叠。这两个步骤都是通过称为原子层沉积(atomic layer deposition)的工艺完成的,该工艺是十多年前引入到半导体制造中的。在该过程中,气态化学物质吸附到芯片的暴露表面,甚至nanosheet的下侧,以形成单层。然后加入第二种化学物质,与第一种化学物质反应,留下所需物质的原子级层,例如电介质二氧化铪(dielectric hafnium-dioxid)。该过程非常精确,使得沉积材料的厚度可控制到单个原子层级。

关于nanosheet设计的令人震惊的事情之一是,它可能延伸摩尔定律,但它仍然要面对热的问题。

每个技术节点的晶体管密度仍在增加。但是IC可以合理地消除的热量。功率密度在过去十年内一直停留在每平方厘米约100瓦的层级。芯片制造商也竭尽全力避免超越这一基本限制。例如为了保持低温,时钟频率不超过4Gh。这也是处理器行业转向多核设计,推出几个较慢的处理器内核去完成与单个快速处理器内核相同的工作,同时产生更少的热量。如果我们希望能够再次提高时钟速度,我们就需要有比硅本身更高效的晶体管。

一种可能的解决方案是将新材料引入沟道区,例如由元素周期表第III和V列元素组成的锗或其他半导体(例如砷化镓)。在这些半导体中,电子的移动速度可以快10倍以上,从而可以更快地切换由这些材料制成的晶体管。更重要的是,由于电子移动得更快,您可以在更低的电压下操作设备,从而提高能效并减少热量产生。

Nanosheet森林:叠层Nanosheet也显示出化合物半导体的巨大前景,例如铟镓砷(gallium arsenide )[上述],以及锗等硅替代品。

2012年,受早期纳米线晶体管和超晶格结构研究的启发,我们使用铟镓砷(一种III-V半导体)构建了一些三纳米片器件。结果好于预期。该nanosheet晶体管允许每微米沟道宽度的电流为9,000微安。这比目前最好的平面InGaAs MOSFET好大约三倍。如果制造工艺得到进一步改善,器件性能仍然远远低于这种晶体管可以提供的极限。通过堆叠更多nanosheet,我们可以将性能提高10倍或更多。(位于加利福尼亚州马里布的HRL实验室的研究人员正在研究数十个nanosheet的叠层,以开发氮化镓功率器件。

并且InGaAs不是未来nanosheet晶体管的唯一选择。研究人员还在探索具有高迁移率电荷载体的其他半导体,如锗,砷化铟和锑化镓。例如,新加坡国立大学的研究人员最近使用由砷化铟制成的n型晶体管和由锑化镓制成的p型晶体管的组合构建了一个完整的CMOS IC 。另外,还有一个可能更简单的解决方案,那就是使用掺杂锗,因为电子和穿过它的正电荷载流子(空穴)的速度都非常快。然而,锗目前仍然存在一些制造工艺和可靠性问题。因此,业界可能首先采用硅锗作为通道材料。

总而言之,堆叠nanosheet似乎是构建未来晶体管的最佳方式。芯片制造商已经对该技术充满信心,可以在不久的将来将其放在路线图上。随着高迁移率半导体材料的整合,nanosheet晶体管可以很好地带给我们任何人现在可以预见的未来。

责任编辑:tzh

-

半导体

+关注

关注

334文章

27101浏览量

216870 -

微处理器

+关注

关注

11文章

2249浏览量

82353 -

晶体管

+关注

关注

77文章

9651浏览量

137919

发布评论请先 登录

相关推荐

三星3nm良率仅20%,仍不放弃Exynos 2500处理器,欲打造“十核怪兽”

三星开发全新设计的3nm工艺晶体管

三星开发全新设计的3nm工艺晶体管

评论