5.1电源优化

PCB 供电系统通常包括地面系统和一个或多个电源,电源和地面网络通常是电路中最大分布式网络, 但也为微控制器电源噪声提供了一个合适的天线,因此,必然要精心设计电源电路,第一步要完成优化电源设计,如上文所述分析任何器件的电源和地引脚失真的潜在性。PCB 的设计应该总是先从供电系统布线开始。

5.1.1地平面系统

(1)系统地

该地面系统有两大功能: 一方面是作为电源供电系统;另一方面,它为所有信号提供了参考。根据欧姆定律,地面系统的任何电流通过地面阻抗引起电压都按比例下降,由于是共用的地阻抗(比较第24页组(1) "共同阻抗耦合"),此电压将覆盖所有和地相关的信号。

为优化地面,在系统地上应该使其具有尽可能低的阻抗和较小的噪声电流

(2)地面

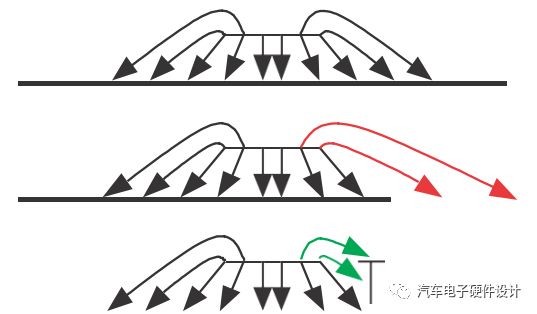

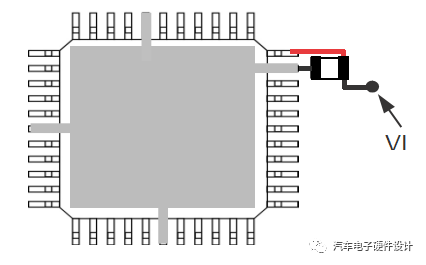

在多层PCB设计过程中,第一要求是能实现用一个完整的层作为地面层。地面层必须不接受任何信号走线或其他长于10mm的空白。地面上的任何空隙都增加其阻抗,这里介绍一下所谓的缝隙 天线,无用缝隙如图例5-1所示。

图 5-1: 缝隙天线

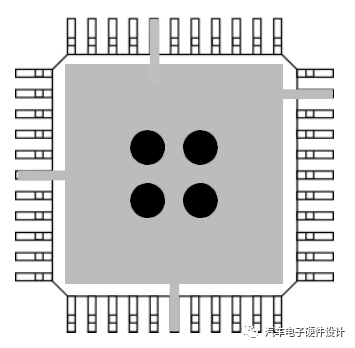

(3)本地器件地

地面系统的第二个作用可以为如下的装置提供额外的本地地,这个本地器件地应通过低阻抗连接到如图中所示的系统地,通过这一结构本地高频电流将远离地面系统,从而避免在系统地上引起相关的电压下降。如图 5-2 所示,4条路线连接到系统地上,是在低阻抗(只有一个连接阻抗的 1/4th)和最小的地间并联之间的折中方案。

图 5-2: 本地器件地

(4)铺地

通常不是每层上的每一个地方都用于布线,这些剩余的地方应充满铜,然后连接到地面。仅仅是某些地方的填充地连接到地是不够的,填充地应至少每 10毫米一格连接到地面, 这一举措进一步降低了接地阻抗,同时又降低了各层之间的串扰。

(5)PCB边缘的防护环

多层板的主要优势是具有一个能够为每个信号或电源提供地面返回路径。如图 5-3中的信号返回的PCB的场线,只有一个具有"无限" 地面的系统是可用的,靠近PCB 的边缘的导线都没有这种"无限"地面,因此可能比其他信号辐射的更多,因此关键的信号(例如时钟线)或电源线(内核电源)不应在 PCB 边缘走线,如果这是不可以避免的, 在PCB的边缘应附带着防护圈。

图 5-3: 地平面上信号的的场线

防护圈目的是高频能量会被辐射到PCB边缘,它被发射返回到板上的部分将被吸收,因此,在边界上的所有层( 包括电源层)的地线应如图 5-4 所示那样应用。由于这些走线应该具有和地面同样的(高频)的电势,他们必须至少每 10mm一格(过孔)连接到地面上。

图 5-4: 4层PCB的防护圈

5.1.2电源布局和退耦

低阻抗地面的可靠性确定之后,PCB设计的下一步是电源布线。

(1)电源面与电源走线

在多层PCB设计过程中,一个方法是完整的面作为电源面,另一个设计方法包括电源走线或者结合两种技术。下面介绍一下两种技术的优缺点。

电源平面的优点

•实现容易、时间短

•低电感电源

•与地面之间形成一个大电容

电源平面的缺点

•每个供电系统都需要一个平面

•如果不同供电面之间没有用地面隔离,则会增加它们之间的串扰

•一个低阻抗的躁声源会影响整个供电系统

•诱导PCB设计者很少考虑电源设计

布电源线的优点布

•在同一层上,可以放置多个供电系统, 因此可以减少电源面之间的串扰

•可以减少每个供电系统内部的串扰

电源线的缺点

•需要仔细地考虑电源布线

•为了保证电源的稳定,较高的供电阻抗需要一个额外的电容

•在高电流时,具有较大直流阻抗

显然,最优方案是把两者优点相结合,因此应该采用本地电源面并且通过导线连接到供电系统上,不同的供电系统应设在同一层或通过地面分离以减少这些供电系统之间的串扰,虽然本地电源面易于操作, 但当连接电源引脚和腿耦电容到平面上时,应该特别谨慎。

(a)退耦电容的连接

微控制器最关键的引脚去耦(请参照第 3章) 往往是在PCB 设计过程中最苛刻的一部分,即使是在一个多层设计中,每毫米导线都要仔细考虑。

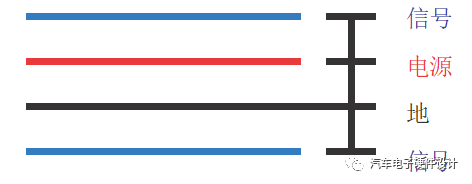

(b)拟定等效电路

当考虑到最佳位置,方向和电容的连接时,纸和铅笔仍然是有益的工具,画一个草图可能会非常有用。每一条线应拟阻抗画出,即使实际意义并不大。图 5-5清楚地暗示:2个红线标识的阻抗应尽量低,而其它 2个可以不作重点考虑。

图 5-5:退耦等效电路

器件供电

图 5-6展示了PCB的布局,连接到本地地面的线应尽可能短,电源线从本地器件通过电容焊盘再经过一个VIA (通孔连接)连接到内部电源面。

例如,把过孔放在该红色导线中心,会添加几个nH电感到电容阻抗,从而将大大地降低滤波效率。此外,其他引脚和/或装置的电源线必须不能从红色导线引出,因为它会引起很大的躁声。

图 5-6: PCB退耦布局

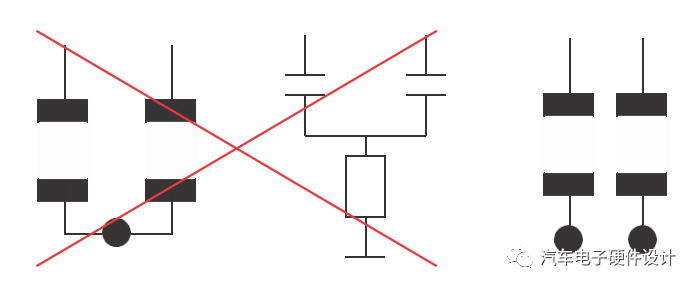

(2)过孔有相当大的阻抗

任何导线和过孔都有一个相当大的阻抗,因此关键电路的过孔如去耦电路必须是独立的,图 5-7

左边 2个图说明了一个共同原因,相关联电路之间共用一个过孔会引起串扰,最右边图展示的是正确接线。

图 5-7: 共用过孔的电路之间的串扰

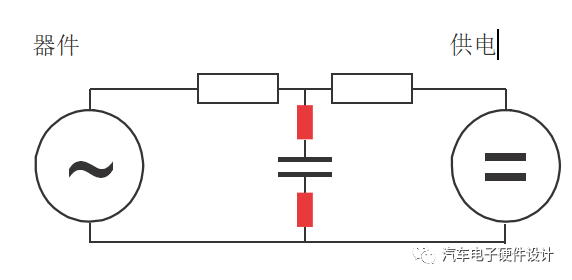

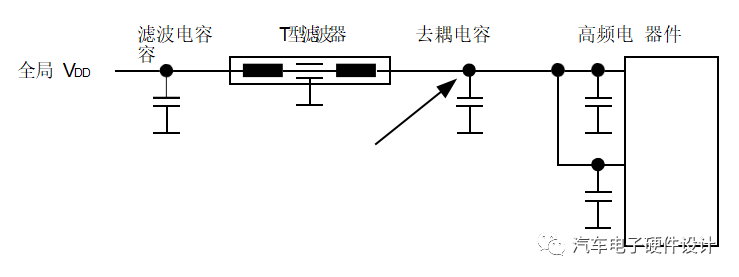

(3)滤波器

如果按照上述设计技术,那么大多数应用都能够完成EMC要求,不过,有关键EMC要求的或复杂的设计,可能需要再加滤波元件,根据一般 EE 经验,应该利用一个多级的电源滤波器。

(a)多级电源滤波器

最关键的电源应利用多级滤波以实现最大可能的噪声抑制。下图是滤波电路的例子,如前所述每一条线的阻抗都应已予考虑,尤其是垂直元件的连接(例如所有电容) 是至关重要的,例如T型过滤器提供一个完美的电源线与电容的连接并且没有增加额外的阻抗。只有PCB设计提供了一个到地面的相对较低阻抗, 全面躁声抑制才能实现。

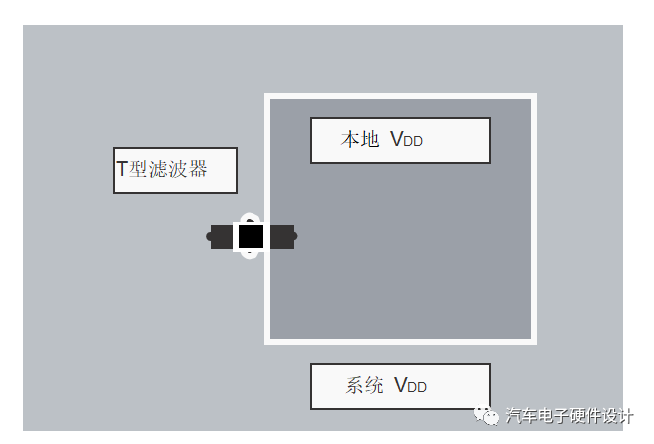

图 5-8: 多级电源滤波r

滤波电容T型滤波器去耦电容高频电器件容

高频电容:应该使用电感最小可行方案( 0603或更小)。应该使用陶瓷材料的NPO或者至少用X7R,电容值不得不在EMC测试时估测,在选择包装时应最大限度地选择现有容量的电容,到器件的连线应该如第5.1.2节(第33页“电源布线和去耦”)描述的那样。

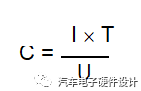

去耦电容:这个电容提供器件中频电流,因为它使脉冲电流形成直流电流,其主要任务是保持供电符合直流规格(例如1.5V+-5%),一个或多个去耦电容( 47 nF to 100 nF, X7R, 0603 )应连接到本地VDD平面上。所需电容的计算方法应根据以下公式,可能需要并行几个电容以降低有ESR和 ESL引起的纹波。

I = 供电系统的最大平均电流

T = 运行的时钟周期

U = 可接受的电压纹波,却省是1%

例如:

对于 3.3V供电系统可接受的电压纹波为U = 33 mV。8MHz 的石英晶振和 5倍频PLL,工作频率为 40MHz 或T = 25 ns,如果供电系统的平均器件电流是 I=100 mA,去耦电容必须至少为 76 nF。

如此计算去耦电容值可能由于所有高频电容累计值而减少,因为这些都是用于并行中的中频段的,连接到地平面和连接到本地地平面至少需要有 2个过孔,如果在生产条件允许的情况下,孔应放置在焊盘的内部, 否则应该使用最短导线长(最大 1mm)。

T型滤波器:铁氧体T型滤波器(例如Murata NFM60R30T222 ) 用于隔离本地电源面和系统电源面。它保持天线结构,为使器件电流噪声减小及使高频能量变热。

接地是最关键的,并应至少有 2 个过孔,如果生产条件允许,孔应放置在滤波器的焊盘内部,否则尽可能的缩短导线长度(最多 1mm)用于接地。

图 5-9: T型滤波器对本地电源的隔离

滤波电容:这个滤波电容(47 nF to 100 nF,X7R,0603)用铁氧体滤波器的一半构成另一个LRC滤波器。

(b)备用桥接元件

当电源电压失真时,最佳的滤波措施是根据评估结果删减可能并不需要的部分,并行元件较易删减, 但串行元件需要根据情况选择桥接元件, 如例图 5-10所示,如果实验证明了串行元件的必要性,所有部分其他元件都将移走,以至为新元件提供空间,另一方面, 不要提供太多的额外元件,因为这些可能造成空间的限制,影响其他部分的电路。

图 5-10: 备用桥接元件

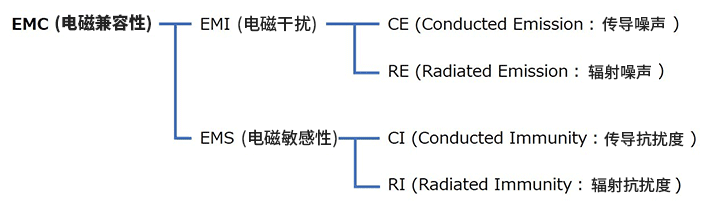

原文标题:微控制器 EMC之电源优化

文章出处:【微信公众号:汽车电子硬件设计】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

电源

+关注

关注

184文章

17704浏览量

249952 -

控制器

+关注

关注

112文章

16332浏览量

177798 -

emc

+关注

关注

170文章

3914浏览量

183117

原文标题:微控制器 EMC之电源优化

文章出处:【微信号:QCDZYJ,微信公众号:汽车电子工程知识体系】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

开关电源的EMI/EMC测试标准

如何优化emc存储性能

开关电源的EMC干扰是怎么产生的?

SN65HVD1040-Q1 EMC优化CAN收发器数据表

SN65HVD1050 EMC优化CAN总线收发器数据表

EMC优化CAN收发器SN65HVD1050-EP 数据表

高功率PCB中EMC的处理与优化策略

EMC的电源优化

EMC的电源优化

评论