描述了在实时嵌入式系统开发中遇到的与CACHE有关的问题。对引起这些问题的原因——CACHE和RAM的不一致性进行了讨论。最后,提出了解决问题的方法。

随着社会的发展、人们生活水平的提高,人们对嵌入式计算机应用的要求也越来越高。因此,对嵌入式系统的性能要求也越来越高。明显体现在嵌入式系统的CPU速度的不断提高上。但问题也随之而来,嵌入式CPU的主频不断地提高,一方面加强了CPU的处理能力,另一方面,在速度上造成了与慢速的系统存储器极不相配的情况,从而影响了整个系统的性能。

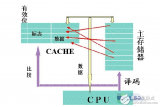

为了解决这个问题,引入了CACHE技术。CACHE是一种高速缓冲存储器,是为了解决CPU和主存之间速度不匹配而采用的一项重要技术。通过在主存和高速CPU之间设置一个小容量的高速存储器,在其中存放CPU常用的指令和数据,CPU对存储器的访问主要体现在对SRAM的存取,CPU可以不必加等待状态而保持高速操作。

采用CACHE技术,解决了CPU与主存之间速度不匹配的问题;但它又带来了一些其它问题,如本文将提到的一致性问题。

1 问题的发现与原因

在进行某嵌入式系统项目的开发过程中,有一个环节需要使用DMA方式进行数据传输。当程序运行后,发现传到目的地的数据块中经常会有一些错误的字节。如:数据本应为00 01 02 03 04 05 06 07 08 09 0A 0B 。..(16进制),结果却是00 01 02 03 00 00 00 00 08 09 0A 0B 。..。在某些环节也出现了类似的问题。例如,通过HDLC通道向外发送数据,发送的总是缓冲区初始化时的内容,实际要发送的数据总是发不出去,但使用调试工具看内存中的数据,却是正确的。

经过一段时间的调试,发现出现这种现象的环节都使用了DMA传输数据。在通过HDLC通道发送数据的例子中,HDLC通道内部也是用DMA方式从内存直接读数据并向外发送。经过分析,认为问题的原因是出在CACHE上,是由于CACHE数据与内存数据的不一致性造成的。

所谓CACHE数据与内存数据的不一致性,是指:在采用CACHE的系统中,同样一个数据可能既存在于CACHE中,也存在于主存中,数据一样则具有一致性,数据若不一样就叫做不一致性。具体表现在两个方面:

(1)更新时可能CACHE中的数据更新,而主存未更新,则造成数据丢失;

(2)在有DMA控制器的系统和多处理器系统中,有多个部件可以访问主存。这时,可能其中有些部件是直接访问主存,也可能每个DMA部件和处理器配置一个CACHE。这样,主存的一个区块可能对应于多个CACHE中的一个区块。于是会产生主存中的数据被某个总线部件更新过,而某个CACHE中的内容未更新,造成数据过时。

2 问题的分析

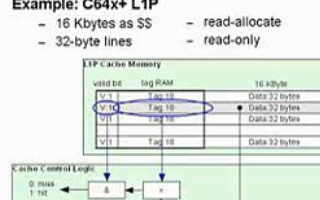

要解释这个问题,首先要了解CACHE的工作模式。CACHE的基本工作模式有两种:write-through模式和 copyback模式。在write-through模式下,所有的写操作都写入CACHE和RAM,保证了CACHE和RAM的一致。然而,每次对RAM都有写操作会使处理器的处理能力降低,并且占用总线带宽。在copyback模式下,写操作只写入CACHE,不写入RAM,从而提高了处理器性能和总线带宽。copyback模式下,CACHE中的内容只有在需要的时候才写到RAM中。当CACHE中无可用空间时,一般使用最近最少使用算法(LRU)来决定哪一个CACHE项被替换。copyback模式提供了很高的系统性能,但是需要更多的一致性作保证。为了便于理解,给出一个使用了CACHE的系统的逻辑框图,如图1所示。

该系统中两个地方会发生CACHE的不一致性:

(1)数据CACHE / RAM

数据CACHE与RAM之间的问题源于处理器和其他总线控制器对RAM的异步读写访问。DMA设备和其他总线控制器对RAM的访问是引起CACHE一致性问题的主要原因,这个问题可以通过在程序中加入一些代码来解决。

(2)共享CACHE LINE

当一个CACHE LINE被两个以上的线程共享时,也会产生一致性问题。当某个线程使一个CACHE LINE无效时,这个CACHE LINE中的一些项可能属于另外一个线程。这个问题也可以通过一定的方法来避免,只要在分配内存时大小是CACHE LINE大小的整数倍即可。

在哈佛体系结构、copyback模式和无软件干预的前提下,最佳的保持一致性的方法就是使用具有总线监听能力的硬件。将CACHE、RAM、DMA设备和其它所有的总线主控设备都连到一个物理总线上,以使CACHE可以对该总线上的总线交互过程进行监听,CACHE将对总线上的地址周期和控制(读/写)比特监听,数据周期则被延迟到需要时才进行。当CACHE中的一项被一个异步操作修改时,该CACHE项就会被标为无效。如果处理器对一个已经被标为无效的CACHE项进行访问时,CACHE就会从RAM中重新载入有效数据。在copyback模式下,处理器对CACHE进行写操作时,RAM相应地址中的内容就变成过时。如果另外一个设备想访问RAM中的这部分内容,CACHE就会抢占该访问周期,将有效的数据写入RAM。然后被抢占的访问周期重新开始并将读到RAM中的有效数据。但是,目前提供监听能力的板子并不多。

3 解决的方法

根据上面的分析和讨论,可见问题正是由数据CACHE / RAM的不一致性引起的。虽然关掉CACHE就可以解决一致性的问题,并且能够减小程序开发的复杂度。但是一个高性能的系统是需要CACHE的,关掉CACHE会大大降低系统的性能。因此,本文仅讨论在程序中加入代码来克服一致性问题的方法。

可以采用以下几种加入代码的方法来解决一致性的问题?本文使用WIND RIVER公司的嵌入式实时多任务操作系统VxWORKS,下面的函数都是VxWORKS提供的 :

(1)对于时间上不是那么关键的程序段,可以先用下面的代码维护数据CACHE的一致性。

cacheInvalidate DATA_CACHE address bytes

/ 输入缓冲区/

。..

cacheFlush DATA_CACHE address bytes

/输出缓冲区/

(2)对于时间上比较关键的程序段采用如下原则:在每次使用输出缓冲区前将其更新;在每次使用输入缓冲区前使其无效。

将缓冲区标示为“non-cacheable”可以防止一致性问题,这需要MMU支持。在分配缓冲区时,将其标示为“non-cacheable”即可。然而,动态缓冲区在释放时要标为“cacheable”,否则内存总会产生大量的缓冲区碎片。

下面给出一个高性能的驱动程序例子,它把更新/无效的概念进行了扩展。不是对整个CACHE系统,而是对每一个缓冲区都这样做。即通过分配对CACHE安全的缓冲区,在一个缓冲区的基础上操作,从而防止了不需要的更新/无效操作。在这个例子中使用了CACHE库中的函数cacheDMAMalloc? ,宏CACHE_DMA_INVALIDATE和CACHE_DMA_FLUSH实现一致性。在第4行调用函数cacheDMAMalloc 后,如果指针返回为非空,则说明分配到了一块对于一致性问题来说是安全的缓冲区。

第7行驱动程序在缓冲区中写入要传给外部设备的数据,在第9行准备传给外设之前,驱动程序必须更新数据CACHE以保证要传的数据是在内存中,而不是在CACHE中。

当驱动程序准备读外设传给内存的数据,在第13行驱动程序处理这些数据之前,必须使数据CACHE中对应于输入缓冲区的那部分无效以消除这些包含过时内容的条目。之后,驱动程序才能安全地处理从内存中取来的输入数据。

1: STATUS drvExample pBuf

2: void pBuf / 缓冲区指针 /

3: { /*

4: pBuf = cacheDMAMalloc BUF_SIZE

5: if pBuf == NULL

6: return ERROR /内存分配失败/

7: /其它初始化代码和向发送缓冲区填数据/

8: CACHE_DMA_FLUSH pBuf BUF_SIZE

9: drvWrite pBuf /向外设发送数据/

10: …… / 其它代码 /

11: drvWait /等待外设来的数据/

12: CACHE_DMA_INVALIDATE pBuf BUF_SIZE

13: / 处理外设来的数据 /

14: cacheDMAFree pBuf /释放内存 /

15: return OK

16:}

责任编辑:gt

-

处理器

+关注

关注

68文章

18894浏览量

227044 -

嵌入式

+关注

关注

5042文章

18795浏览量

298140 -

存储器

+关注

关注

38文章

7361浏览量

163037

发布评论请先 登录

相关推荐

中央处理器与高速缓冲存储器之间的联系

高速缓冲存储器的作用解析

高速缓冲存储器的特点解说

高速缓冲存储器的作用是什么_有什么特点

高速缓冲存储器基础知识详细介绍

基于CACHE高速缓冲存储器技术在嵌入式系统中的应用

基于CACHE高速缓冲存储器技术在嵌入式系统中的应用

评论