DSP芯片凭其优异的性能在高速计算领域有着巨大的应用前景。但其应用所涉及的知识非常庞杂。当程序调不通不知该从何处下手时,此文也许会有所帮助。

1. McBSP(Multichannel Buffered Serial Port)串口利用DMA中的多帧(Multi-Frame)方式通信的中断处理

在实际通信应用中,一个突发之后,程序必须为下一个突发作准备。因此一般采用串口的DMA多帧方式但在串口以DMA方式传输数据时却有一些问题要讨论。首先DMA的传输同步事件应设McBSP的传输事件即XEVT,这样一字节传输后会自动准备另一字节(McBSP的READY上升沿触发DMA传输)。中断发生时意味着一个块已传完,这时DMA的使能自动关闭,McBSP的READY将一直保持高状态。但是在下一次突发传输直接使能DMA时却启动不了传输(相信会有许多我遇到此类问题)。这是因为无法产生McBSP触发启动所需的READY上升沿。解决办法是在中断程序中先关闭McBSP的发送,使READY=0,随后在程序中发送使能DMA,再打开McBSP的发送即可。如先打开McBSP的发送后打开DMA,也是不会工作的。因为McBSP的READY已经由0变到1了,无法再产生READY上升沿。

2. 关闭DMA与关闭McBSP的区别

在通信领域,为了充分利用DSP的片上外设资源,常常利用DMA把从串口来的数据或要发的数据放入缓冲区,再处理。对DMA而言,只要其在数据缓冲区的指针指向了中断应发生的位置,就产生中断。但此时最后一个数据只是进入了McBSP而并未真正发出去,所以在传送结束的中断程序中只能关闭DMA不能关闭McBSP。因为此时McBSP的发寄存器DXR中还有一个字没有发出。

3 .McBSP串口配置的关键时序

主要是寄存器SPCR2的配置:在保持RRST、XRST、FRST各位为0的前提下,配置好其它串口控制寄存器。等待至少2个CLKR/T时钟以确保DSP内部的同步。 (1)可以向DXR装载数据或使能DMA。 (2)使能GRST(GRST=1)(如果需要DSP内部产生采样时钟)。 (3)使能RRST或XRST,注意此时要保证SPCR中仅有此一位发生改变。 (4)使能FRST(FRST=1)(如果需要DSP内部产生帧同步)。 (5)等待2个R/T CLK时钟周期后,收或发端便会有效。

4. 汇编语言程序中的变量

汇编语言程序中的公用变量应在文件中定义,如.def carry。汇编语言程序中使用的局部变量不需定义,可直接声明,例如trn_num .word 00h。如果在两个asm文件中有两个都没有定义的同名变量,则编译程序会认为分他们不是同一变量。在汇编程序的开头应有.mmregs宏语句。它一方面表示对默认定义的确认(ah,bh,trn等),另一方面可以对所用寄存器重新定义。如: .mmregs DMPREC .set 54h ;定义DMA优先和使能寄存器地址在54h DMSA .set 55h DMSDN .set 57h DXR10 .set 23h ;定义串口1的发送寄存器地址在23h。

5. ST1寄存器中CPL位的影响

CPL位是编译模式控制位,它表示在相对直接寻址时采用哪种指针。当CPL=0时,使用页指针DP;当CPL=1时,使用堆栈指针SP。实际使用中二者没有什么差别,但使用SP寻址的程序更易读。在程序中经常使用CPL=1。

审核编辑黄昊宇

-

dsp

+关注

关注

553文章

8030浏览量

349307 -

编程

+关注

关注

88文章

3627浏览量

93807

发布评论请先 登录

相关推荐

TMS320C6000 DSP软件可编程锁相环控制器指南

使用 AMD Versal AI 引擎释放 DSP 计算的潜力

使用AMD Versal AI引擎加速高性能DSP应用

用PPS进行miniDSP编程的几个问题求解答

DSP控制器的主要优势是什么?

使用运算放大器应注意哪几个问题

DSP的硬件架构与关键技术

解决关键问题 明星产品B15i获客户致谢

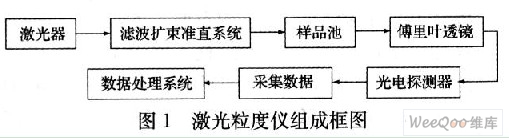

分享DSP和ARM的激光粒度仪关键电路设计

DSP编程的几个关键问题(1)

DSP编程的几个关键问题(1)

评论