本期分享的科研成果来自中科大、港科大与中科院微电子所的联合课题组,其团队研制的无线充电芯片峰值效率可达92.3%,迄今同类研究中报道的国际最高效率,其成果获得了2020年IEEE ASP-DAC的最佳设计奖,有望助力无线充电技术的进一步成熟。

研究背景

在大家日常所熟悉的手机领域,无线充电已经从5瓦发展到65瓦功率,高端电动汽车上的无线充电技术也开始向中级和紧凑型下放,可以预见无线充电将会成为未来充电技术的重要发展方向,在消费电子、生物医疗电子、物联网以及电动汽车等方面具有广阔的应用前景,一直备受学术界和产业界的关注。与传统有线充电具有稳定的直流电压相比,无线充电芯片首先需要对通过线圈耦合得到的交流电压进行整流和稳压。由于经过多级功率处理,充电效率大大降低,并且严重限制了充电功率。

为解决这项难题,中科大与港科大和中科院微电子所的联合课题组提出了一种应用于谐振型无线功率传输的新型无线充电芯片架构。相关研究成果于2020年4月以“A 6.78-MHz Single-Stage Wireless Charger With Constant-Current Constant-Voltage Charging Technique”为题发表于IEEE Journal of Solid-State Circuits。程林教授为论文第一作者和通讯作者。该项成果在2019年Symposia on VLSI Technology and Circuits会上时即被评为技术亮点(Technical Highlights)论文,其后发表于IEEE JSSC并获得了2020年IEEE ASP-DAC的最佳设计奖(Best Design Award)。

基本特性

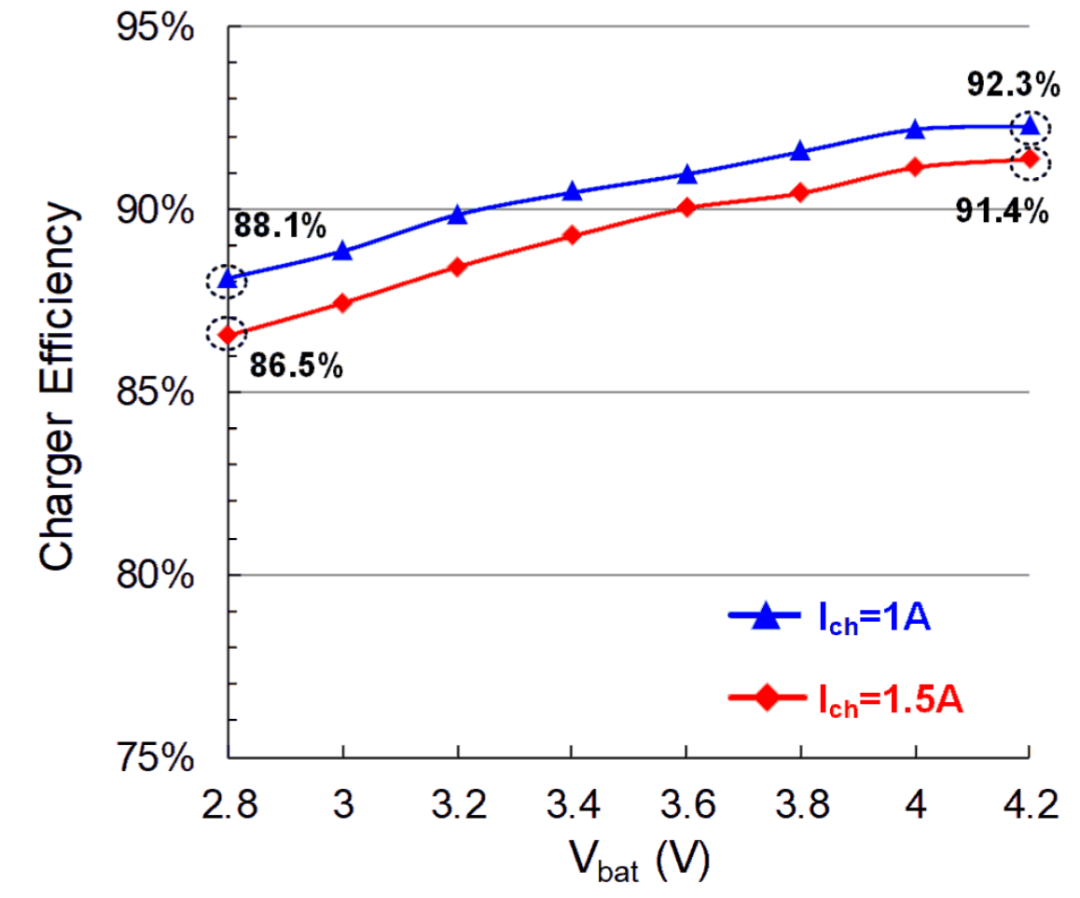

该研究提出了一种基于可重构谐振调节整流器的单级无线充电架构,首次将整流、稳压和恒流-恒压充电三个功能在单个功率级内完成,克服了现有芯片设计中需要两级或三级级联的缺点,从而大大提高了芯片的充电效率和集成度。此外,该研究还提出了一种片上栅压自举技术,采用了一种自适应相位数控制的单输入双输出倍压器将自举电容集成在片上,进一步提高了芯片的集成度。采用0.35μm CMOS工艺流片,测试结果表明芯片在充电电流为1A时,峰值效率可达92.3%,为迄今同类工作中报道的国际最高效率。该架构为今后谐振型无线充电芯片的设计提供了一个高效的解决方案。

模型与测试结果

这里给大家选取了原理结构图和部分测试结果:

无线充电电路示意图

芯片结构光学实拍图

测试步骤

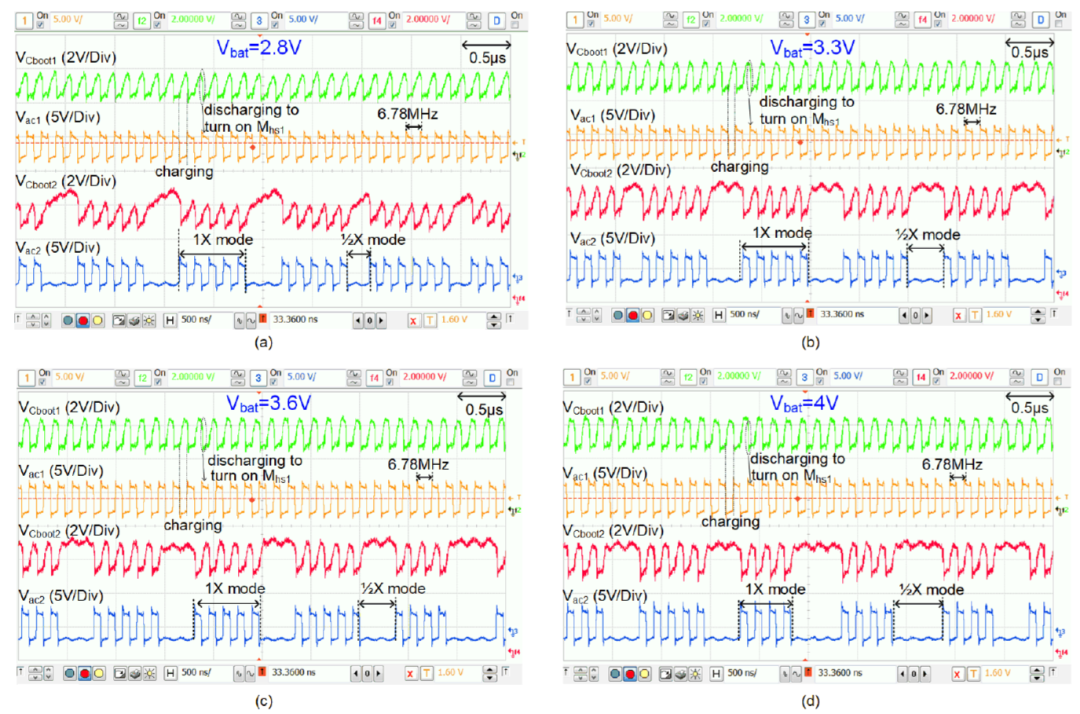

不同电压条件下的稳态波形(a)Vbat=2.8伏;(b)Vbat=3.3伏;(c)Vbat=3.6伏;(d)Vbat=4.0伏

转换效率测量

前景展望

无线充电联盟(WPC)主席诺·特雷弗斯曾断言无线充电最终会像WiFi一样无处不在,而现在无线充电技术的快速发展确实在消费电子和汽车电子领域展现了其便利与实用性,小编非常期待能看到《三体》中可随时随地的无感无线充电技术,真正改变人类的生活方式。本项研究成果在无线充电效率问题上给出了更高效的解决方案,想必将会助力无线充电技术的进一步成熟和普及。

原文标题:科研前线 | 中科大无线充电芯片获2020年IEEE ASP-DAC的最佳设计奖

文章出处:【微信公众号:芯片揭秘】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

芯片

+关注

关注

457文章

51345浏览量

428256 -

无线充电

+关注

关注

1295文章

3288浏览量

317281

原文标题:科研前线 | 中科大无线充电芯片获2020年IEEE ASP-DAC的最佳设计奖

文章出处:【微信号:ICxpjm,微信公众号:芯片揭秘】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

中科大无线充电芯片获IEEE ASP-DAC最佳设计奖

中科大无线充电芯片获IEEE ASP-DAC最佳设计奖

评论