作者:付汉杰,hankf@xilinx.com,文章转载自:博客园

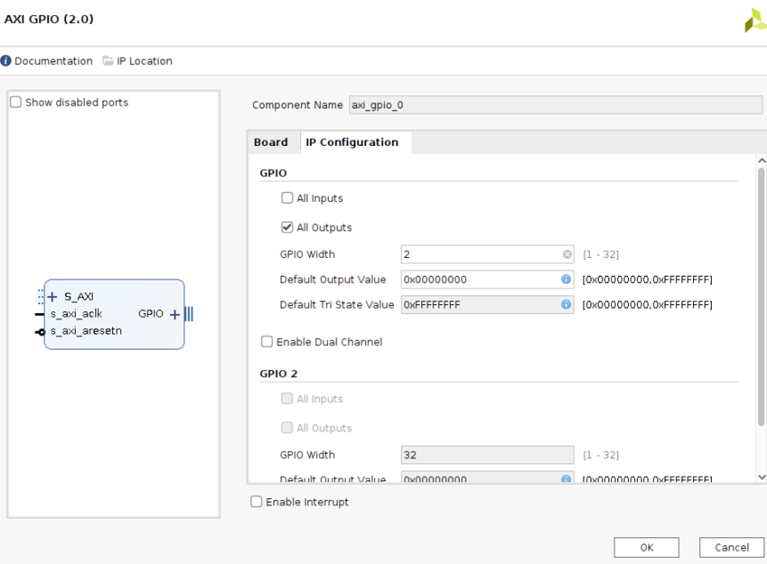

不同使用场景,对芯片的性能和功耗要求不一样。为了测试Xilinx MPSoC PS侧的最低功耗,基于ZCU106单板做了功耗优化。为了方便,使用最简单的软硬件环境。软件使用死循环做串口打印,硬件保留了如下模块。

A. A53 0

B. QSPI flash Dual Parallel

C. I2C 0/1

D. PMU

E. UART 0

F. GPIO MIO

G. SWDT 0/1

H. TTC 0/1/2/3

I. DDR 16-bit

J. DPLL/RPLL

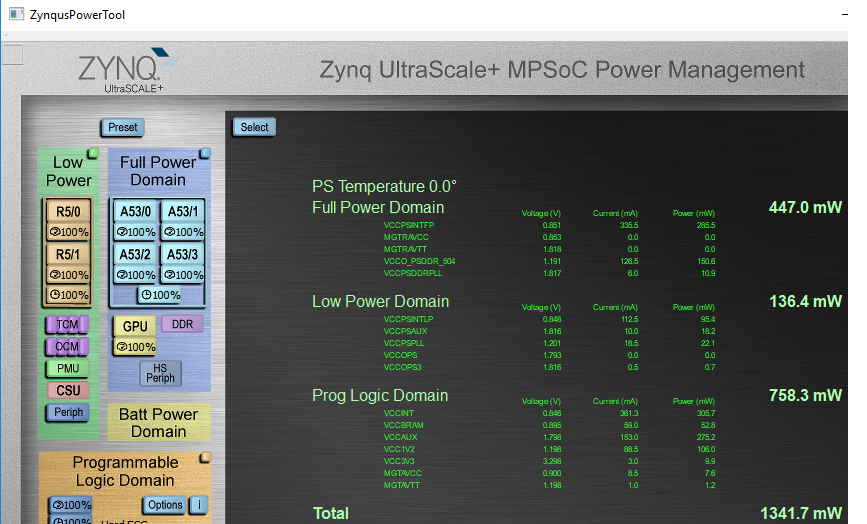

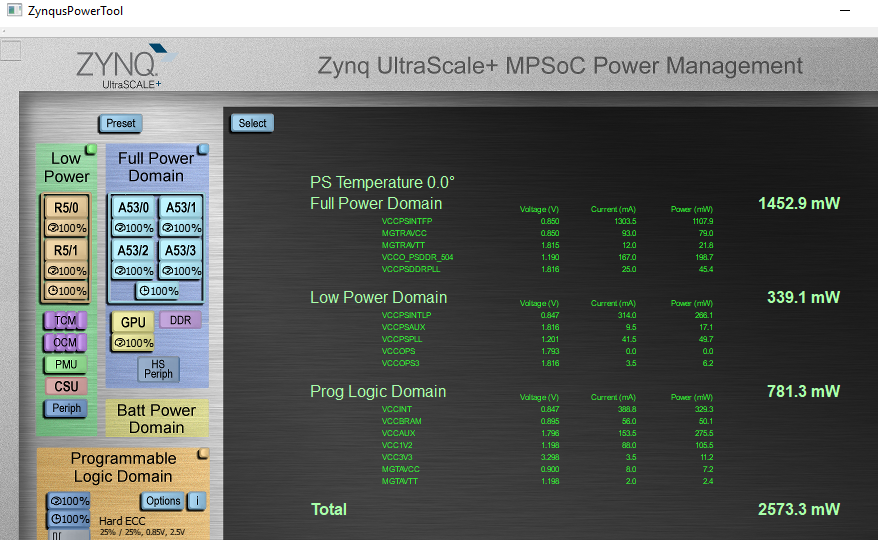

在关闭其他外设,尽可能降低各个模块的频率后,FPD功耗是447mw,LPD是136mw。作为对比,Vivado使用ZCU106单板建立工程,使用默认设置,FPD功耗是1452mw,LPD是339mw。可以看到,新设计节省了相当大的功耗。当然,具体的产品使用场景,可能有性能和功能要求。能达到什么效果,还需要根据产品要求再做评估。

优化后的功耗

优化前的功耗

责任编辑:xj

原文标题:【资深工程师分享】ZCU106 MPSoC 功耗优化

文章出处:【微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

-

Xilinx

+关注

关注

71文章

2173浏览量

122714 -

单板

+关注

关注

0文章

31浏览量

10993 -

MPSoC

+关注

关注

0文章

199浏览量

24395

原文标题:【资深工程师分享】ZCU106 MPSoC 功耗优化

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何实现蓝牙模块的功耗优化?

AMD/Xilinx Zynq® UltraScale+ ™ MPSoC ZCU102 评估套件

如何优化单片机项目的功耗

Multi-Scaler IP的Linux示例以及Debug(上)

基于ZCU106单板的功耗优化

基于ZCU106单板的功耗优化

评论