最佳处理解决方案常常是由RISC、CISC、图形处理器与FPGA的组合提供,或由FPGA单独提供,或以硬处理器内核作为部分结构的FPGA提供。然而,许多设计人员不熟悉FPGA的功能、其发展脉络以及如何使用FPGA。

设计人员一直在寻找系统构架的构建方法,以提供可满足所有应用需求的最佳计算解决方案。在许多情况下,这种最佳解决方案常常需要使用现场可编程门阵列(FPGA),但令人遗憾的是,很多设计人员对这些器件的功能以及如何进行整合并不熟悉。

为何要使用FPGA?

计算应用多种多样,能满足应用需求的最佳方法可能因应用而异,包括现成的微处理器(MPU)和微控制器(MCU)、现成的图形处理单元(GPU)、FPGA以及定制片上系统(SoC)器件。为了确定使用哪一种方法,需要仔细审视应用需求和考虑事项。

例如,当研究5G基站等尖端技术时,设计人员需要考虑到基础标准和协议仍在不断发展中。这意味着设计人员需要能够快速有效地应对任何超出控制范围的规范变更。

同样,他们需要能够灵活地响应未来在系统部署到现场后发生的标准和协议变更。此外,他们还必须能够响应系统功能中的意外错误或系统安全性方面的漏洞,修改现有功能或添加新功能,从而延长系统使用寿命。

尽管最高性能通常是由SoC提供,但这种方法既昂贵又耗时。另外,在芯片结构中实现的任何算法本质上都是“冻结在硅片中”。鉴于上述考虑,这种固有的不灵活性便成了问题。为了找到高性能和灵活性的最优平衡点,需要一条替代路线。该路线常常由FPGA、微处理器/微控制器与FPGA的组合或以硬处理器内核作为部分结构的FPGA提供。

什么是FPGA?

这是一个很难回答的问题,因为对不同人来说,FPGA是不同的东西。而且,FPGA的类型有很多,每种类型都有不同的能力和功能组合。

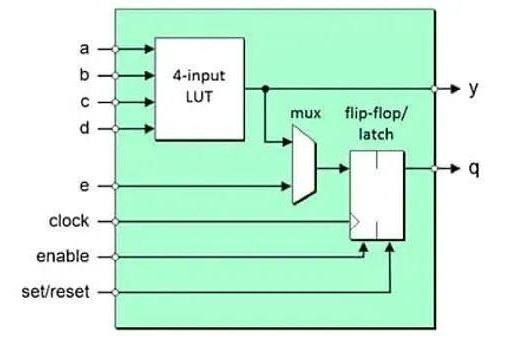

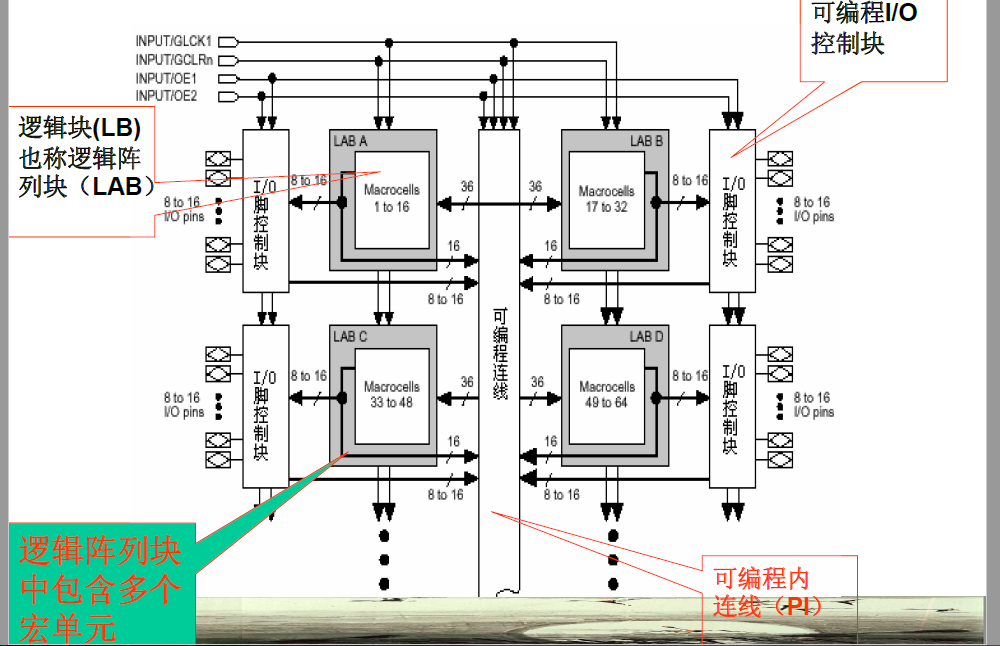

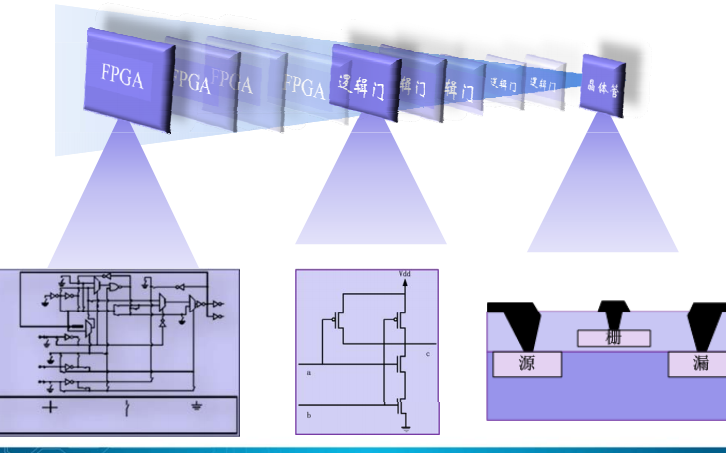

可编程结构是任何FPGA的核心(即“FPGA-dom”的界定方面),并以可编程逻辑块阵列的形式呈现(图1a)。每个逻辑块都是多种元件的集合,包括查找表(LUT)、多路复用器和寄存器,所有这些元件都可以进行配置(编程)以根据需要执行操作(图2)。

图1:最简单的FPGA仅包含可编程结构和可配置GPIO(a),不同架构是在此基本结构上增加其他元件而形成:SRAM块、PLL和时钟管理器(b),DSP块和SERDES接口(c),以及硬处理器内核和外设(d)。(图片来源:Clive“Max”Maxfield)

图2:每个可编程逻辑块都是多种元件的集合,包括查找表、多路复用器和寄存器,所有这些元件都可以进行配置(编程)以根据需要执行操作。(图片来源:Clive“Max”Maxfield)

许多FPGA使用4输入LUT,可配置为实现任何4输入逻辑功能。为了更好地支持某些应用采用的宽数据路径,有些FPGA提供6输入、7输入甚至8输入LUT。LUT的输出直接连接到逻辑块输出之一和多路复用器输入之一。多路复用器的另一个输入直接连接到逻辑块输入(e)。多路复用器可以配置为选择其中一个输入。

多路复用器的输出馈入寄存器输入。每个寄存器都可以配置为边沿触发的触发器或电平敏感锁存器(尽管如此,但不建议在FPGA内部使用锁存器形式的异步逻辑)。每个寄存器的时钟(或使能信号)可以配置为高电平有效或低电平有效。同样,置位/复位输入的有效电平也是可配置的。

这些逻辑块可以被视为漂浮在“可编程互连之海”中的“可编程逻辑之岛”。这种互连可配置为将任何逻辑块的任何输出连接到其他逻辑块的任何输入。同样,FPGA的主要输入可以连接到任何逻辑块的输入,任何逻辑块的输出都可以用来驱动器件的主要输出。

主要的通用输入/输出(GPIO)以组形式呈现,每组可配置为支持不同的接口标准,例如LVCMOS、LVDS、LVTTL、HSTL或SSTL。另外,输入的阻抗也是可配置的,输出的压摆率也一样可配置。

FPGA结构进一步扩展可包括SRAM块(称为块RAM(BRAM))、锁相环(PLL)和时钟管理器之类的东西(图1b)。此外,还可以添加数字信号处理(DSP)块(DSP切片)。它们包含可配置的乘法器和可配置的加法器,能够执行乘法累加(MAC)运算(图1c)。

高速SERDES块是FPGA的另一个常见特性,能支持千兆位串行接口。必须注意的是,并非所有FPGA都支持上述全部特性。不同FPGA针对不同的市场和应用提供不同的特性集合。

FPGA中的可编程结构可用来实现所需的任何逻辑功能或功能集合,一直到处理器内核甚至多个内核。如果这些内核是以可编程结构实现的,则称其为“软内核”。相较之下,有些FPGA(通常称为SoCFPGA)包含一个或多个“硬内核”处理器,其直接在硅片中实现(图1d)。这些硬处理器内核可能包括浮点单元(FPU)和L1/L2高速缓存。

同样,外设接口功能(如CAN、I2C、SPI、UART和USB)可以实现为可编程结构中的软内核,但许多FPGA将其作为硬内核在硅片中实现。处理器内核、接口功能和可编程结构之间的通信通常利用AMBA和AXI之类的高速总线实现。

第一批FPGA是由Xilinx于1985年推出上市,仅包含一个8x8可编程逻辑块阵列(没有RAM块、DSP块等)。相比之下,当今的高端FPGA可以包含数十万个逻辑块、数千个DSP块和以兆位(Mb)计的RAM。总体而言,它们可能包含数十亿个晶体管,相当于数千万个等效门(例如2输入NAND门)。

备选配置技术

为了确定逻辑块的功能和互连的布线,需要借助配置单元,后者可以用0/1(断开/接通)开关来形象地表示。这些单元还用于配置GPIO接口标准、输入阻抗、输出压摆率等。根据具体FPGA,这些配置单元可以采用如下三种技术之一来实现:

反熔丝:这些配置单元是一次性可编程(OTP)单元,意味着一旦对器件进行了编程,就无法撤回。此类器件往往仅限于太空和高安全性应用。其销量很小,因此价格很高,可谓昂贵的设计选择。

闪存:像基于反熔丝的配置单元一样,基于闪存的单元也是非易失性的。与反熔丝单元不同,闪存单元可以根据需要重新编程。闪存配置单元可以承受辐射,因而这些器件适合于太空应用(不过要对上部金属化层和封装进行修改)。

SRAM:采用这种手段时,配置数据存储在外部存储器中,每次FPGA上电时都要从存储器中加载数据(或在动态配置情况下,按照指令要求加载数据)。

对于配置单元基于反熔丝或闪存的FPGA,优势在于它们是“即时接通”,功耗很小。这些技术的一个缺点是,除了用于创建芯片其余部分的基础CMOS工艺之外,他们还需要其他处理步骤。

对于配置单元基于SRAM技术的FPGA,优势在于使用与芯片其余部分相同的CMOS工艺制造,并且具有更高的性能,因为它通常比反熔丝和闪存技术领先一代或两代。主要缺点是SRAM配置单元比(相同技术节点的)反熔丝和闪存单元更耗电,并且容易因为辐射而发生单粒子翻转(SEU)。

长期以来,后一个缺点导致基于SRAM的FPGA被认为不适合用于航空航天应用。最近,业界采用了特殊缓解策略,使得基于SRAM的FPGA与基于闪存的FPGA一同出现在“好奇号”火星漫游车等系统上。

利用FPGA提供灵活性

FPGA适用于多种多样的应用,特别适合用于实现智能接口功能、电机控制、算法加速和高性能计算(HPC)、图像和视频处理、机器视觉、人工智能(AI)、机器学习(ML)、深度学习(DL)、雷达、波束赋形、基站以及通信。

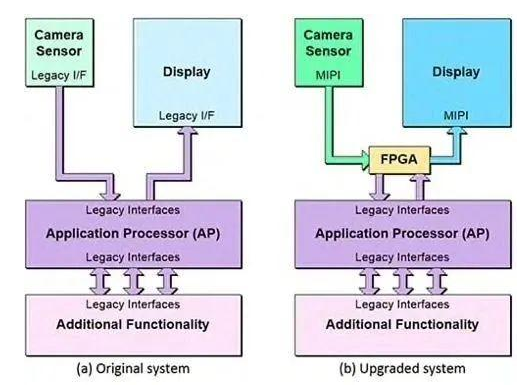

一个简单的例子是在其他使用不同接口标准或通信协议的器件之间提供智能接口。请考虑一个现有系统,其中有一个应用处理器使用旧式接口连接到相机传感器和显示设备(图3a)。

图3:FPGA可用于在其他使用不同接口标准或通信协议的器件之间提供智能接口,从而延长基于旧式器件的现有设计的寿命。(图片来源:Clive“Max”Maxfield)

现在,假设系统的创建者希望将相机传感器和显示设备升级为更轻、更便宜、功耗更低的现代产品。唯一的问题是,两个新外设或其中之一可能使用现代接口标准,而原应用处理器(AP)却无法提供支持。或者,它们可能支持完全不同的通信协议,例如移动行业处理器接口(MIPI)。在这种情况下,采用支持多种I/O标准的FPGA,再加之以某些软MIPIIP内核,将能提供一条快速、低成本、无风险的升级路径(图3b)。

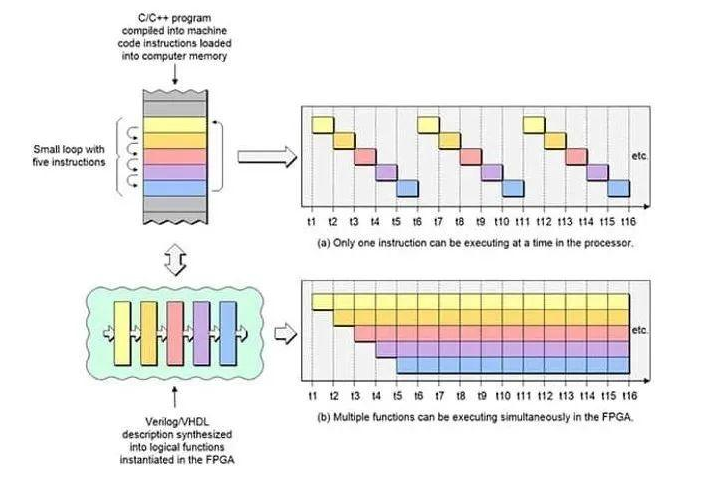

再举一个应用例子,考虑一些计算密集型任务,例如执行雷达系统所需的信号处理或通信基站中的波束赋形。采用冯诺依曼或哈佛架构的常规处理器非常适合某些任务,但不适合于需要重复执行相同操作序列的任务。这是因为运行单个线程的单个处理器内核一次只能执行一条指令(图4a)。

图4:微处理器一次只能(顺序地)执行一条指令,与此不同的是,FPGA中的多个功能块可以同时(并发地)执行。另外,FPGA能以大规模并行方式实现适当的算法。(图片来源:Clive“Max”Maxfield)

相比之下,FPGA中可以同时执行多个功能,支持以流水线方式完成一系列操作,进而实现更大的吞吐量。同样,FPGA不像处理器那样执行相同的操作,例如对1,000对数据值再执行1,000次运算,而是在可编程结构中实例化1,000个加法器,从而在单个时钟周期中以大规模并行方式执行相同的计算(图4b)。

哪些厂商制造FPGA?

这是一幅不断演变的画卷。具备最高容量和性能的高端器件有两家主要制造商,分别是Intel(其收购了Altera)和Xilinx。

Intel和Xilinx提供从低端FPGA到高端SoCFPGA的各种产品。另一家几乎完全专注于FPGA的供应商是LatticeSemiconductor,其针对的是中低端应用。最后但并非最不重要的一家是MicrochipTechnology(通过收购Actel、Atmel和Microsemi),现在可提供多个系列的中小型FPGA和低端SoCFPGA类产品。

由于产品系列众多,每个系列提供不同的资源、性能、容量和封装样式,因此为眼前的任务选择最佳器件可能很棘手。

下面是一些例子:Intel器件;LatticeSemiconductor器件;以及Xilinx器件。

如何使用FPGA进行设计?

传统的FPGA设计方法是工程师使用Verilog或VHDL之类的硬件描述语言来捕获设计意图。首先可以对这些描述进行仿真,以验证其是否符合要求,然后将其传送给综合工具,生成用于配置(编程)FPGA的配置文件。

每家FPGA供应商要么有自己内部开发的工具链,要么提供专业供应商定制的工具版本。无论哪种情况,都可以从FPGA供应商网站获得这些工具。另外,成熟工具套件可能有免费或低成本的版本。

为使FPGA更易于为软件开发人员所用,一些FPGA供应商现在提供高级综合(HLS)工具。这些工具会解析在C、C++或OpenCL中以高级抽象所捕获的期望行为的算法描述,并生成输入以提供给较低级的综合引擎。

对于希望入门的设计人员,有许多开发和评估板可用,每种板提供不同的功能和特性。这里给出三个例子:DFRobot的DFR0600开发套件,其具有Xilinx的Zynq-7000SoCFPGA;TerasicInc.的DE10Nano,其具有Intel的CycloneVSoCFPGA;ICE40HX1K-STICK-EVN评估板,其具有LatticeSemiconductor的低功耗iCE40FPGA。

若设计人员计划使用基于FPGA的PCIe子卡来加速X86主板上运行的应用程序,可以关注AlveoPCIe子卡等产品,也是由Xilinx提供。

总结

最佳设计解决方案常常由FPGA、处理器与FPGA的组合或以硬处理器内核作为部分结构的FPGA提供。

FPGA多年来发展迅速,能够满足灵活性、处理速度、功耗等多方面的设计需求,适合于广泛的应用。

责任编辑人:CC

-

FPGA

+关注

关注

1630文章

21763浏览量

604560

发布评论请先 登录

相关推荐

FPGA基础知识:什么是FPGA,为何需要FPGA?

RF和天线的基础知识以及实际的天线设计原理

FPGA基础知识简介

FPGA教程之CPLD与FPGA的基础知识说明

FPGA基础知识培训教程免费下载

了解FPGA和CPLD架构的基础知识资料下载

FPGA的基础知识以及解决方案

FPGA的基础知识以及解决方案

评论