作者:顾波,张红涛,刘新宇,邱道尹

随着国家电力系统两网改造工程的逐渐推进及“一户一表,供电到户”政策的贯彻实施,电力用户数量急剧膨胀,用电网络日益庞大,供电企业的用电管理任务也越来越重,加之国家供电的发送配分开,更要求供电企业加大对各大中小电户的监控力度。而传统的抄收方式主要是依靠人工每月定期上门抄取,这种做法不仅耗费大量的人力物力,工作效率低,给用户带来诸多不便,同时发生电费拖欠现象,造成电力公司的损失。低压电力线载波远程抄表系统是利用现有的低压电力网和公共电话网作为数据采集与传输通道,不仅从根本上克服了人工抄表带来的诸多缺点,实现了对用户用电量的自动抄表及收费管理等多种功能,而且具有施工量小、可靠性高、成本低等优点。 但现有低压电力线载波远程抄表系统由于各种原因,存在这样或那样的弊端,例如负荷情况复杂、噪声干扰强且具有时变性、信号衰减大、信道容量小等。如何克服这些缺点,是现阶段低压电力线载波远程抄表系统设计的主要目标。本文所用的基于令牌存储技术的采集器设计与实现技术,就是为了克服以上缺点的一种方法。

1 采集器硬件设计

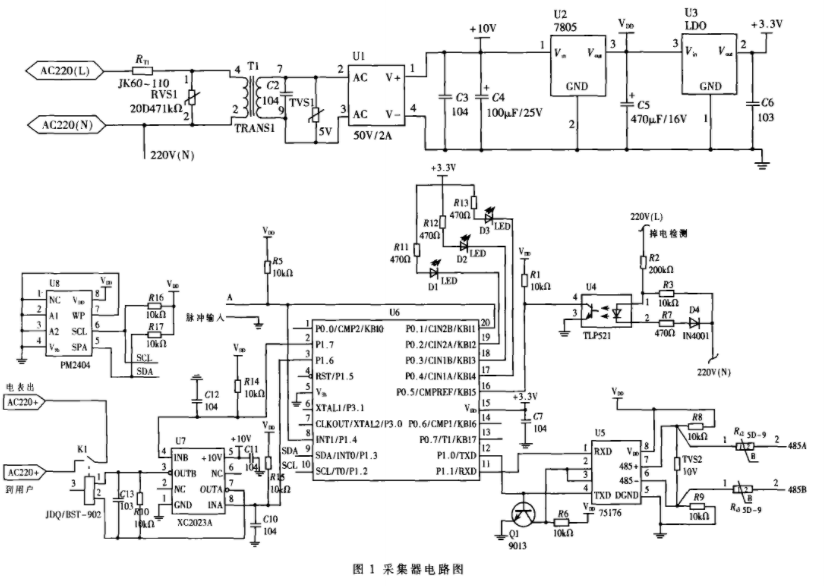

1.1 采集器电路设计

采集器的电路设计如图1所示。采集器是数据进行采集、累计、传输的部件,其设计的好坏将直接影响整个抄表系统的正确性。所以,采集器的设计是整个系统设计最为关键的一步,在设计采集器时,需做到以下三点:

(1)实时记录电表脉冲信号,并按要求保存,可根据脉冲个数等参数计算出当前电表度数。

(2)可实现继电器控制、状态监视并可记录继电器状态。

(3)可读取电表度数、电表地址等信息,并可对其进行参数设置,进行欠费指示、继电器通断等控制。

1.2 采集器各部分功能

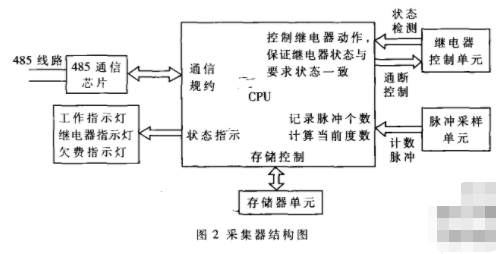

采集器总体结构如图2表示,其各部分功能如下:

(1)485通信芯片:主要实现采集器与上位机之间的通信,从而可以从采集器的存储器中读取相关数据,其具体通信协议以国家标准为主。

(2)状态指示:指示当前电表的工作状态,由3只二极管组成,其中一只表示正常工作;另一只表示用户欠费;第三只表示继电器动作,切断用户电表。

(3)状态检测:在系统掉电或重新启动时,确保启动时的状态与掉电前的状态相符合。

(4)脉冲采样:完成脉冲的采集与计数任务。

(5)存储控制:主要存储电表的地址、初始值、变比参数、已有的脉冲个数、已记录的电表数及继电器在系统掉电前的状态。

2 采集器软件设计

2.1 基于令牌存储技术的数据存储设计

在进行采集器的设计时,数据准确、安全地存储和传输是非常重要的,其结果决定着其他部分的正常工作。但由于采集器工作在现场的最前端,容易受到环境的影响,如采集器的突然掉电、数据在存储过程中突然受到计数脉冲中断的影响等,这些都会导致写到存储器中的数据不准确。如何克服这些不足,是采集器设计过程中的一个难点。根据采集器的实际工作环境,本文提出一种基于令牌储存技术的数据存储设计方法,该方法能很好地解决数据存储过程中的不准确和不安全现象。

该方法的具体思路为:在存储区中开辟三个互不相连的存储空间,分别定义为ADDR1、ADDR2、ADDR3,每个存储区又分为两部分,第一部分存储令牌,用tokening表示(用一个整数表示),第二部分存储当前电表度数,用memdata表示。下面详细说明本算法的思想。

(1)系统初始参数:当系统第一次使用时,把ADDR1.tokening、ADDR2.tokening和ADDR3.tokening中的数据值全部设置为零,把ADDR1.memdata、ADDR2.memdata和ADDR3.memdata中的数据设置为0、0.01、0.02(其中0.01代表0.01度电)。

(2)当用电量有0.01度时,需要将这0.01度电加到存储区的用电度数中。首先把ADDR1.tokening、ADDR2.tokening和ADDR3.tokening中的数据相加,其和为0时,则把ADDR1.memdata中的数据加0.01,同时改变ADDR1.tokening中的数据,使其为1。

(3)当用电量第二次到0.01度时,把ADDR1.tokening、ADDR2.tokening和ADDR3.tokening中的数据相加,其和为1时,由此可以得到ADDR1.memdata刚被存储过,把ADDR2.memdata中的数据加0.01,改变ADDR2.tokening中的数据,使其为2。

(4)当用电量第三次到0.01度时,把ADDR1.tokening、ADDR2.tokening和ADDR3.tokening中的数据相加,其和为3时,由此可以判断ADDR1.memdata和ADDR2.memdata已经存储过,把ADDR3.memdata中的数据加0.01,改变ADDR3.tokening中的数据,使其为4。

(5)当用电量第四次到0.01度时,把ADDR1.tokening、ADDR2.tokening和ADDR3.tokening中的数据相加,其和为7,这时可以判断ADDR1.memdata、ADDR2.memdata和ADDR3.memdata都已经被存储过了,重新从ADDR1.memdata开始存数,把ADDR1.memdata中的数据加0.01,改变ADDR1.tokening中的数据,使其为0。

(6)当用电量第五次到0.01度时,把ADDR1.tokening、ADDR2.tokening和ADDR3.tokening中的数据相加,其和为6,这时可以判断ADDR1.memdata中数据刚改变,应该把数据存储到ADDR2.memdata中,把ADDR2.memdata中的数据加0.01,并把ADDR2.tokening中的数据改为0。

(7)当用电量第六次到0.01度时,把ADDR1.tokening、ADDR2.tokening和ADDR3.tokening中的数据相加,其和为4,这时可以判断ADDR1.memdata和ADDR2.memdata都已经被存储过了,应该把ADDR3.memdata中的数据加0.01度,并把ADDR3.tokening中的数据改为0。这时的令牌状态又重新回到了初始状态,并且保证了数据区中的数据相差0.01度电,当有新的数据到来时,令牌数据又重新从初始状态开始。

(8)错误处理:当系统掉电或被其他干扰影响时,经常会出现存储数据不正确的现象,如果使用上述存储方法,可以克服这些错误。每次在更改存储区中的数据或向上位机发送电表度数时,都会首先把三组存储区中的数据和令牌值取出来,然后根据令牌值,把三组数据两两相减,根据数据间的差额可以判断三组存储区中的数据是否正确,若正确才进行改变或发送,否则可以根据另外两组数据来还原其中一组数据,从而保证整个数据在系统运行期间的正确性。

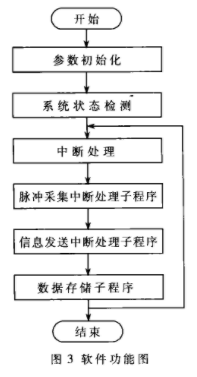

2.2 软件系统设计

软件设计的任务主要是实现采集器的各部分功能,如图3所示。包括485芯片通信功能设计、脉冲采集设计、数据存储设计、状态检测设计、系统初始化等部分功能。

基于令牌储存技术设计思想设计的采集器,极大地提高了采集器的稳定性和数据的正确性。采用本技术设计的采集器,在河南郑州、济源、周口等地市使用,其抄表成功率在99.8%以上,很好地满足了用户要求。

责任编辑:gt

-

芯片

+关注

关注

456文章

50936浏览量

424681 -

继电器

+关注

关注

132文章

5354浏览量

149165 -

数据采集

+关注

关注

39文章

6157浏览量

113760

发布评论请先 登录

相关推荐

基于FPGA的软硬件协同仿真加速技术

单片机软硬件联合仿真解决方案

支持过程级动态软硬件划分的RSoC设计与实现

基于SoPC的状态监测装置的嵌入式软硬件协同设计

基于Altera FPGA的软硬件协同仿真方法介绍

单片机测控系统的软硬件平台技术

基于SoPC的状态监测装置的嵌入式软硬件协同设计与实现

基于FPGA的软硬件协同测试设计影响因素分析与设计实现

电源电路板软硬件设计

为什么要从“软硬件协同”走向“软硬件融合”?

软硬件融合的概念和内涵

基于令牌储存技术实现数据存储电路的软硬件设计

基于令牌储存技术实现数据存储电路的软硬件设计

评论