一个用于构建可扩展和FPGA上的快速BNN推理加速器 专门针对量化神经网络 每秒处理数亿次机器学习推断

您听说过 FINN 吗?没有?这个答案并不令人惊讶,因为这是一个用于探索基于 FPGA 的深层神经网络推断的实验框架的全新再实现,而且它现在仍是赛灵思研究实验室 (Xilinx Research Lab) 的测试版。然而, 虽然还是测试版,它已经发布了 v0.4b(测试版),并且自从在 GitHub 上开源以来,受到了广泛关注。

2020 年 5 月,赛灵思研究实验室的论文《FINN-R:快速探索量化神经网络的端到端深度学习框架》获得了计算机协会 (ACM) 可重构技术和系统汇刊 (TRETS) 2020 年年度最佳论文奖 —— 该奖项每年只授予全年论文中的一篇。该论文的第一作者、杰出工程师 Michaela Blott 女士和她的团队在今年夏天的第 57 届设计自动化大会线上颁奖典礼上接受了这一荣誉。该论文的评选引起了人们对 FINN 的更广泛关注:FINN 是什么,为什么选择 FINN,如何实现 FINN?带着这些问题,我们采访了 Michaela Blott 女士。

FINN 是什么?

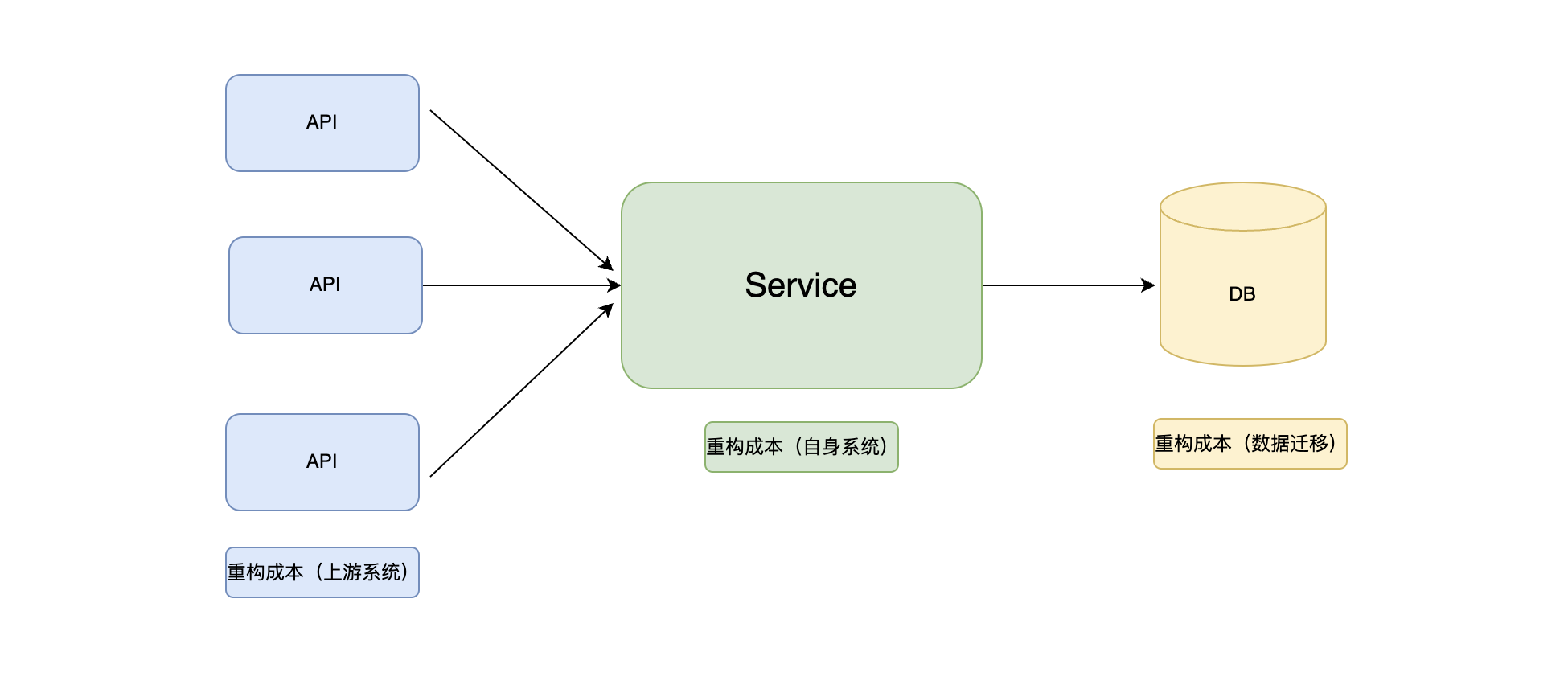

FINN(神经网络快速推断)是我们的一个旗舰开源项目的名称,是赛灵思研究实验室的一个实验框架,用于探索基于 FPGA 的深层神经网络推断。它专门针对量化神经网络,着重于为每个网络生成定制的数据流式架构。这种形式的高度专业化有助于加速需要更高吞吐量和超低时延的应用。 然而,要实现定制相当困难,而且通常只有专家才可以进行定制。对此,FINN 提供了一个端到端流程,即使是机器学习工程师也可以创建这些高度定制的硬件解决方案,以前馈数据流架构的形式为具有任意精度/任意层的空间展开式卷积神经网络加速器提供支持。它实际上是一种工具流,能够帮助没有硬件专业知识的人员生成高度定制的 FPGA 设计,并从我们的器件所提供的性能和效率中获益。 最初的版本侧重于二进制网络。自此,我们扩展到可支持任意精度 (FINN-R) 并提供更高灵活性的终端架构和目标平台,其中包括给定器件的硬件成本估算。我们在包括 PYNQ 和 Alveo 在内的一系列平台上对各种不同精度的神经网络生成的架构进行了评估,从小型 CIFAR-10 分类器、基于 PASCAL VOC 数据集的 YOLO 对象检测到 ImageNet 分类网络和 LSTM。我们目前正在添加更多极端用例,比如网络入侵检测,在这种情况下,FINN 每秒可以处理数亿次机器学习推断。 如需了解有关 FINN 的更多基本信息,请访问项目页面,查看出版物或一些演示。

FINN 有哪些特性?

●模板化的 Vivado HLS 流组件库:FINN 带有 HLS 硬件库,该硬件库可将卷积,全连接,池化和 LSTM 层分类实现为流组件。该库使用 C++ 格式来支持各种精度。

●超低时延和高性能的数据流:通过为每一层组成流组件,FINN 可以生成加速器,这些加速器可以以亚微秒级的时延对图像进行分类。

●多种端到端的设计示例:我们提供的示例从训练量化神经网络开始,一直到硬件上运行的加速设计。这些示例涵盖了一系列数据集和网络拓扑。

●用于快速生成设计的工具流程:FINN 工具流程支持自动或手动为每层分配单独的计算资源,并生成用于综合的完整设计。这样可以快速探索设计空间。

为什么要为开源

重新构建 FINN?

在过去的几年里,爱尔兰赛灵思研究实验室的团队对量化神经网络 (QNN) 进行了大量研究。从 2016 年基于 FPGA 的二进制神经网络 (BNN) 开始,我们已经对量化深度学习的众多方面进行了研究,涵盖从更好的量化方法、混合量化和修剪到精确吞吐量权衡和递归拓扑等众多领域。虽然我们工作的某些演示已经实现开源有一段时间了,但我们希望能更进一步。我们喜欢 QNN,同时也很青睐在赛灵思 FPGA 上为其构建的高性能、高效率的数据流加速器,我们希望您和 FPGA/ML 社区也能这样做。实现这一目标的(协同)设计流程实际上相当复杂,从在机器学习框架中定制神经网络开始,经过涉及众多优化、HLS 代码生成和 Vivado 综合的多个设计步骤,最后得到 FPGA 比特流,可以作为某个应用的组成部分进行部署。其中大量步骤都需要一些手动操作,但是如果能有一个模块化的、灵活的解决方案堆栈来支持您完成这个流程将非常有帮助。这就是为什么我们要从头开始重建我们的 FINN 解决方案堆栈,使其更加模块化。

我们选择 FINN 开源路线的主要原因是为了提供更高程度的灵活性和透明度。机器学习研究进展迅速,因此 FINN 是研究人员可以用来实现最新层类型的工具。

用户如何进一步了解 FINN?

您可以使用 GitHub 问题跟踪器报告错误,但请不要以提交问题的形式来提出问题,因为这在 gitter 频道中可以得到更好的处理。此外,我们也衷心欢迎您针对本项目做出贡献,请查看贡献指南和公开问题列表。如果您有任何想法,请随时联系 Gitter 进行讨论。 我们渴望扩大我们的社区,并希望听到您的消息。

为什么开源和神经网络

非常适合赛灵思?

赛灵思提供了可以对其器件进行编程的工具。有了开源,我们就可以充分利用并为世界一流的成果做出贡献。FINN 的量化感知训练库 Brevitas (https://github.com/Xilinx/brevitas)建立在 Pytorch 上,Pytorch 是基于 Torch 库的常用开源机器学习库,用于计算机视觉和自然语言处理。 我们为这个现有的开源框架提供了大量的库,这些库使得对网络的训练可以一直精确到 1 位。这充分利用了 Pytorch 已有的所有优异技术,并使用户群体从量化中获益。此外,将这些网络映射到我们的 FPGA 上的实现工具是开源的,它利用了现有的赛灵思技术,其中包括高层次综合以及基于 FPGA 的布局布线。参见下图。

关于赛灵思实验室

赛灵思研究实验室通过其对公司战略和愿景的贡献占据了技术领先地位。该组织为未来的产品创造新的技术机遇,致力于应对最新涌现的工程挑战,并消除对实现公司业务目标至关重要的技术风险。我们积极地与各个高校、初创企业和采用早期技术的客户建立联系,发现新挑战并获得他们对新想法的反馈。

关于 Michaela Blott 简介

Michaela Blott 是爱尔兰都柏林赛灵思研究中心的杰出工程师,她领导着一个由国际科学家组成的团队,该团队致力于推进激动人心的研究,为赛灵思器件探索全新的应用领域,例如应用于嵌入式和超大规模部署的机器学习。她在德国凯泽斯劳滕大学获得硕士学位,在研究机构(如苏黎世联邦理工学院和贝尔实验室)和开发机构拥有超过 25 年的先进计算机架构以及先进 FPGA 和电路板设计经验。她积极投身于国际研究界,担任 FPL 2018 年的技术联合主席、研讨会组织者 (H2RC、ITEM)、众多欧盟项目的行业顾问、众多技术计划委员会(FPL、ISFPGA、DATE 等)的成员,2015 年获得 WMB 奖,入围 2019 年 VentureBeat Women 人工智能奖,并获得 2019 年女性科技奖。

原文标题:Xilinx实验室为何为开源而重构 FINN?

文章出处:【微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

Xilinx

+关注

关注

71文章

2173浏览量

122723 -

网络

+关注

关注

14文章

7645浏览量

89577 -

开源

+关注

关注

3文章

3467浏览量

42923

原文标题:Xilinx实验室为何为开源而重构 FINN?

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

THS1209 SYNC脚位的功能为何?

采用Xilinx FPGA的AFE79xx SPI启动指南

基于相变材料的可重构超构表面用于图像处理

如何以及为何要在EtherCAT®应用中使用DP83826

「重构:改善既有代码的设计」实战篇

Xilinx为何重构 FINN?

Xilinx为何重构 FINN?

评论