同步电路设计将系统状态的变化与时钟信号同步,并通过这种理想化的方式降低电路设计难度。同步电路设计是 FPGA 设计的基础。

01

触发器

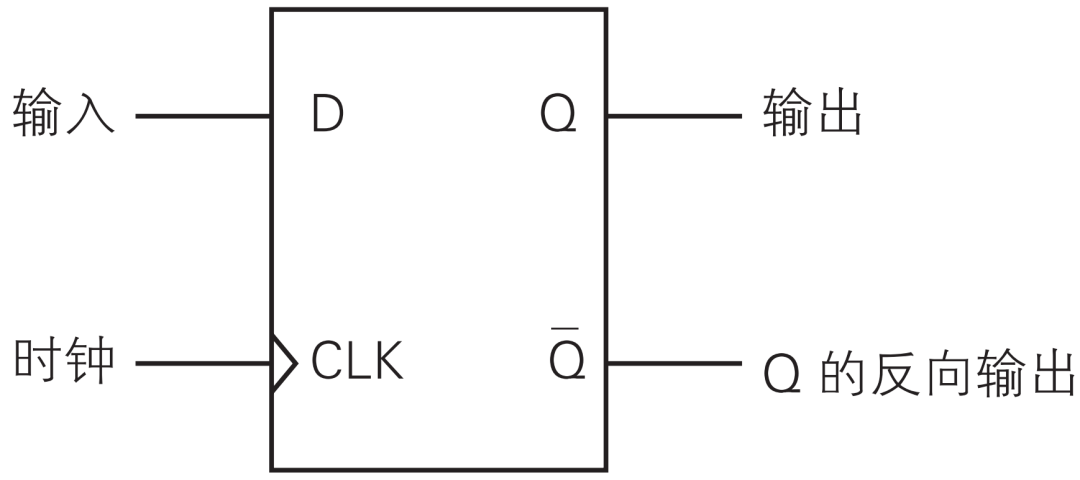

触发器(Flip Flop,FF)是一种只能存储1个二进制位(bit,比特)的存储单元,并且具备记忆功能,可以用作时序逻辑电路的记忆元件。FPGA逻辑单元内的D触发器(D-FF)具有两个稳定状态,即"0"和"1",在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态,就是一种在时钟的上升沿(或下降沿)将输入信号的变化传送至输出的边沿触发器。D-FF的符号和真值表如图1所示。D-FF在CLK信号(时钟)的上升沿将输入值传送至输出Q。

图 1 D 触发器

02

建立时间和保持时间

时钟是整个电路最重要、最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行,这就要求时钟信号时延差要非常小, 否则就可能造成时序逻辑状态出错;因而明确FPGA设计中决定系统时钟的因素,尽量较小时钟的延时对保证设计的稳定性有非常重要的意义。

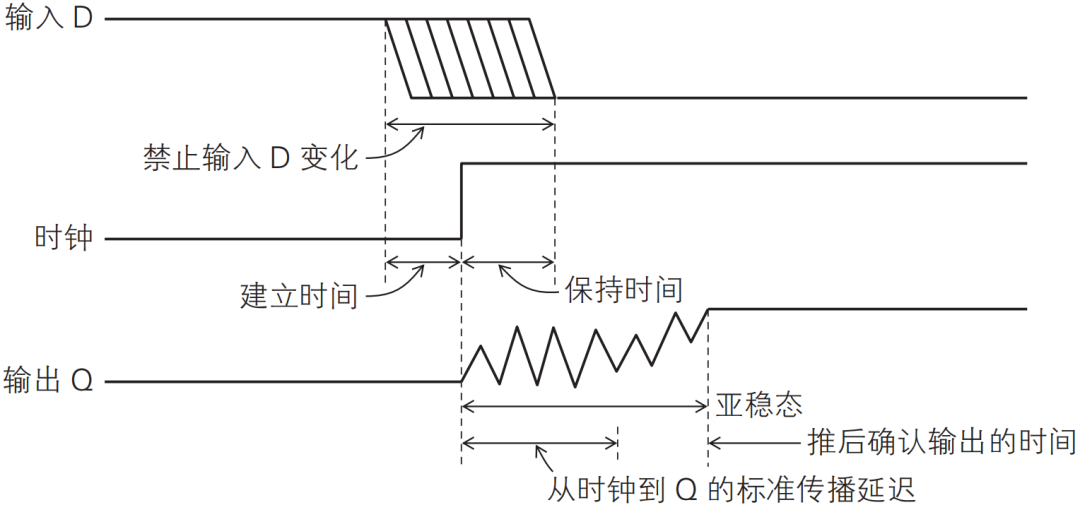

建立时间(Tsu:set up time)是指在时钟沿到来之前数据从不稳定到稳定所需的时间,如果建立的时间不满足要求那么数据将不能在这个时钟上升沿被稳定的打入触发器;

保持时间(Th:hold time)是指数据稳定后保持的时间,如果保持时间不满足要求那么数据同样也不能被稳定的打入触发器。

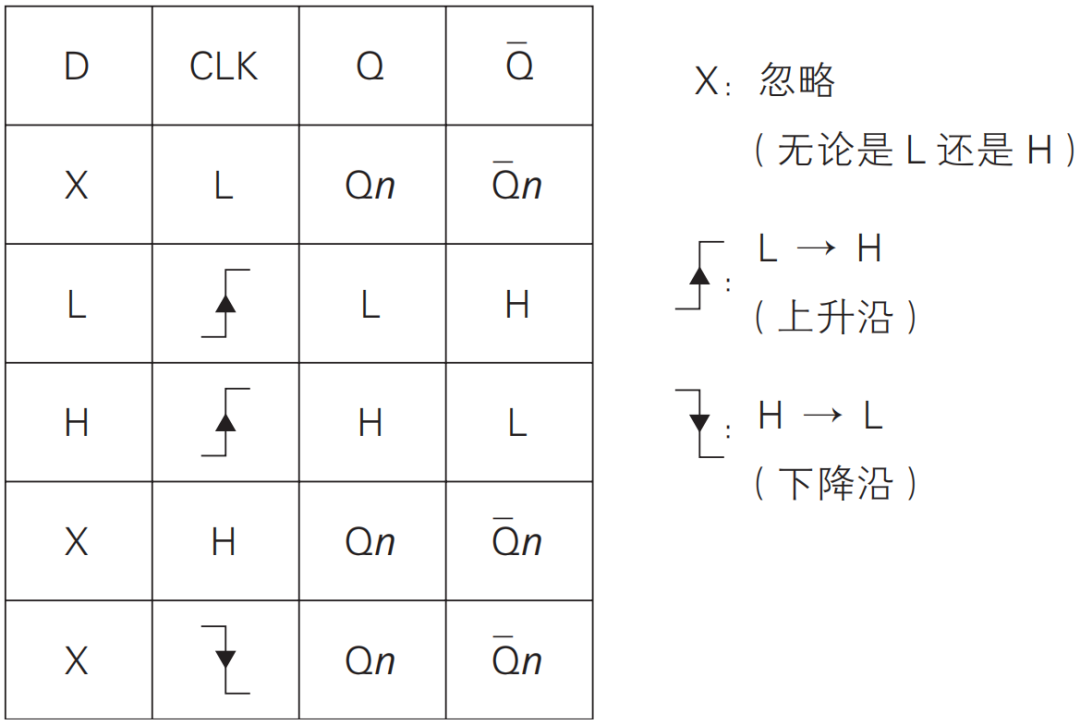

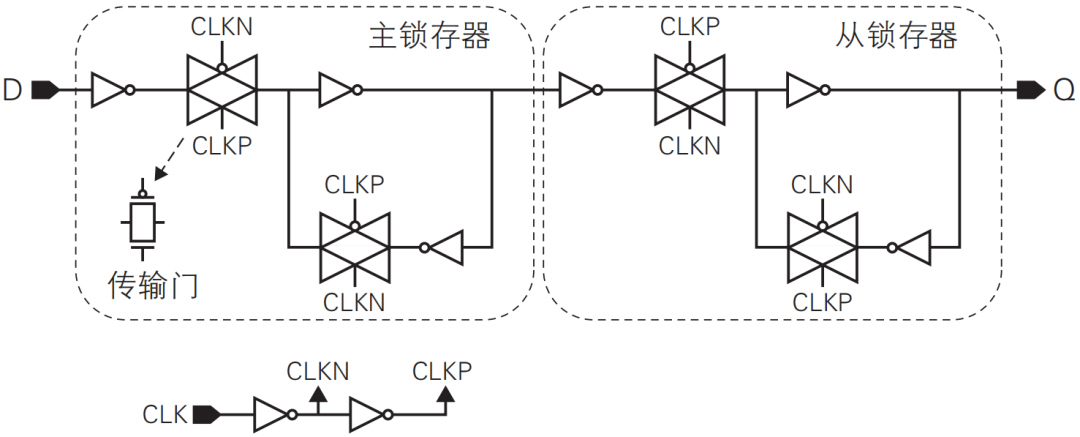

CMOS 工艺下的D-FF结构如图2所示,先由传输门和两个反相器组成一个循环电路(锁存器),再由前后两级锁存器按主从结构连接而成。这里的传输门起开关的作用,随着CLK的状态变化切换开关。只看输出的话,前级锁存器的值会将时钟输入的变化井然有序地传入后级锁存器。为了防止时钟信号变化时输入信号发生冒险,从而使稳定的输入信号进入前级锁存器,前级锁存器的时钟相位应该与产生输入信号的电路时钟反向。图3 为 D-FF 的原理图。

图 2D-FF 的电路结构

图 3D-FF 的原理

当CLK=0主锁存器工作)时,位于前级的主锁存器将输入D的值保存进来,后级的从锁存器则维持上一时钟周期的数据。由于此时前级和后级反相器环路之间的传输门是关闭状态,所以前级的信号不会传送到后级。当CLK=1(从锁存器工作)时,前级反相器环路中保存的数据会传输到后级,同时输入D的信号会被隔离在外。此时如果前级反相器环路中的信号没有循环一圈以上,就会出现如图4所示的在 0 和 1 之间摇摆的中间电位,这就是所谓的亚稳态(metastable)。由于亚稳态时间比延迟时间长,在该阶段读取数据可能会引入错误,所以我们引入建立时间(setup time)来约束在时钟上升沿到来前输入 D 保持稳定 的时间。

当 CLK=1 时,如果输入 D 在传输门关闭前就发生变化,那么本该 在下一周期读取的数据就会提前进入锁存器,从而引起反相器环路振荡 或产生亚稳态。因此在 CLK=1 之后也需要输入 D 维持一定的时间,我 们称之为保持时间(hold time)约束。

为了正确地从输入读取数据,并正确地将数据输出,FPGA 内所有 的 FF 都要遵守建立时间和保持时间等时序上的约束。

图4建立时间和保持时间

03

时序分析

从硬件描述语言(Hardware Description Language,HDL)编写的RTL(Register Transfer Level,寄存器传输级)设计代码生成网表(逻辑门间的配线信息)的过程称为逻辑综合。最终决定逻辑综合所生成的电路网表在FPGA中以何种方式实现的两道工序称为布局和布线。FPGA内部规则地摆放着大量设计好的电路及电路间配线,用以实现用户设计。所谓 FPGA 的设计流程,就是决定专为FPGA综合生成的电路摆放在哪儿、电路之间以什么样的布线路径相连的过程。

为了保证设计好的电路能够正常工作,不单要保证功能(逻辑)正确,还必须要确保时序正确。而时序分析是以分析时间序列的发展过程、方向和趋势,预测将来时域可能达到的目标的方法。此方法运用概率统计中时间序列分析原理和技术,利用时序系统的数据相关性,建立相应的数学模型,描述系统的时序状态,以预测未来。在 FPGA 的设计流程中,从逻辑综合到布局布线,每一步都会对生成的电路进行评估分析。由于基于仿真的方式分析每个逻辑值并进行动态时序分析的方法过于耗时,所以 FPGA 的性能评估主要采用静态时序分析(Static Timing Analysis,STA)。STA只需要提供电路网表就可以进行全面的评估验证,并且原理上只需遍历一次电路的拓扑结构,因此也具有分析速度快的优点。最近,随着电路规模不断增大,不仅FPGA其他 EDA 工具也采用 STA 的方式来验证电路是否能够按照要求的速度正确工作。时序分析包含对设计电路的建立时间分析和保持时间分析,并能够以此进行时序验证。时序验证主要是评估 FPGA 上设计电路的延迟是否满足时序约束(时序上的设计需求)。布线的延迟取决于 FPGA 设计电路的摆放位置和所使用的布线,也就是说取决于布局布线工具的编译结果。当 FPGA 的性能和逻辑门资源富余时编译过程较为容易;相反,当设计电路的规模和 FPGA 片上资源相当时,布局布线过程所需时间可能会很长。时序分析必须检查所有路径上逻辑延迟和布线延迟的时序余裕,确保它们满足建立时间和保持时间的时序约束。

04

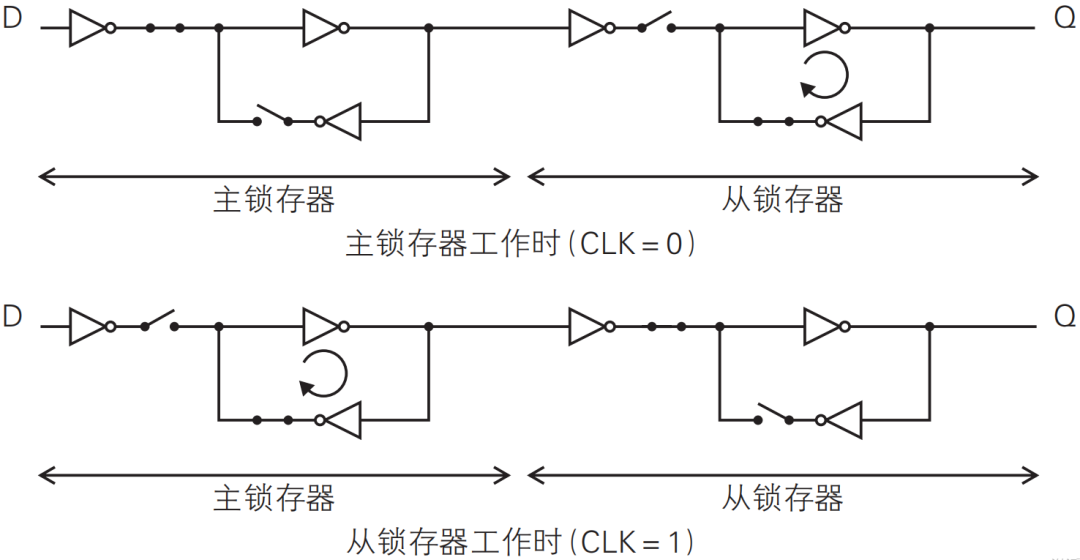

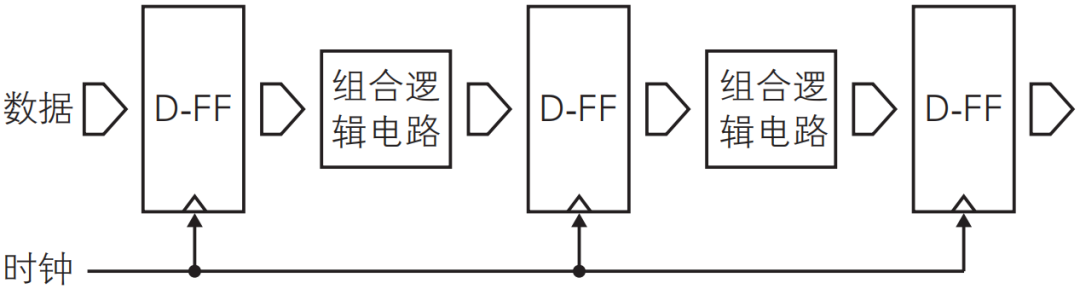

单相时钟同步电路

布局布线上具有一定自由度的 FPGA 都以同步电路设计方式为主, 而同步电路可以使用STA进行时序分析和验证。STA具有验证速度高的优点,但对电路结构有一定的要求:延迟分析的起点和终点必须是基于同一时钟的FF,从而可以通过累加起点和终点间的延迟来计算、验证每条路径的总延迟。因为各条路径上的布线长度长短不一,所以信号的延迟会不同,输出数据变化的时间点也会有所差别。因此如图5所示,FPGA设计中的输入信号会先被送到FF,输出信号则必须从FF引出,并且所有FF都由同相的时钟驱动。这种设计属于由同一时钟的同一边沿同步动作的电路类型,而反相时钟(相位反转的时钟或反方向的边沿)不属于此类。基本上,采用单一时钟进行同步是较为理想的选择。

同步设计的一个前提是所有FF都必须同时接收到时钟信号,而现实中时钟信号的布线非常长,时钟信号驱动的负荷(扇出数)、布线延迟等原因会导致出现时间差,因此很难严格地满足上述条件。这种时钟信号到达时间的错位称为时钟偏移(skew)。另外,由于时钟振荡器的 变动或信号变形,时钟边沿会偏离平均位置,这种情况称为时钟抖动(jitter)。为了保证所有 FF 的输入时钟信号同步,需要将时钟偏移和时 钟抖动控制在一定范围之内。

图5 单相时钟同步电路

时钟偏移和逻辑门电路的延迟一样,会对时钟周期的设定产生影响。因此时钟设计是集成电路时序设计的重要一环。而 FPGA 上已经提前实现好了多层时钟树结构,并且通过驱动能力强的专用布线(global buffer)将时钟低偏移地连接到整个芯片的FF 上,因此在时钟设计上要 比 ASIC 容易很多。

责任编辑:xj

原文标题:理解FPGA的基础知识——同步电路设计

文章出处:【微信公众号:FPGA技术联盟】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1629文章

21729浏览量

603024 -

同步电路

+关注

关注

1文章

60浏览量

13310

原文标题:理解FPGA的基础知识——同步电路设计

文章出处:【微信号:gh_873435264fd4,微信公众号:FPGA技术联盟】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

同步电路设计:将系统状态的变化与时钟信号同步

同步电路设计:将系统状态的变化与时钟信号同步

评论