10月21日,Flex Logix 公司今天宣布其InferX X1 芯片可开始出货。该芯片是AI边缘系统领域迄今为止性能最高的芯片之一。InferX X1可对目标检测与识别等各类神经网络模型进行加速,其应用范围包括机器人、工业自动化、医学成像、基因测序、银行安全、零售分析、自动驾驶、航天工程等等。与目前业内领先的AI边缘推理解决方案相比,InferX X1 在处理 YOLOv3 目标检测识别模型时的性能提高了 30% ,在处理其他多个用户模型时的性能提高了10倍。

相比于其他各类目标检测与识别的神经网络模型,YOLOv3的准确率是比较高的。因此,许多机器人、银行安全及零售分析领域的客户都计划在产品中使用 YOLOv3。还有一些客户根据自己的应用需求,开发了一系列AI模型,希望可以在较低成本下获得更高的吞吐量。Flex Logix 对这些客户模型进行了基准测试。基准测试的结果显示,InferX X1 不仅可以完全满足用户在吞吐量方面的要求,并且价格更低。Flex Logix 将于近期开始向早期客户出货样品芯片,并计划于明年一季度向更广大客户群体提供样品芯片。批量生产的芯片将于2021年下半年开始全面出货。

InferX X1芯片面积为54mm2, 仅为1美分硬币的1/5大小,更是远远小于其它同类产品。InferX X1 芯片的批量价格仅有目前行业领军产品的1/10左右。这是高质量、高性能的AI推理产品第一次真正走向普罗大众。原本昂贵的AI推理将不再遥不可及。

InferX X1 配套的软件使其非常易于用户使用。其中的InferX Compiler可以将TensorFlow Lite 或者 ONNX 的模型直接转换为可以在InferX X1上运行的程序。

“对于已有边缘推理系统的用户来说,他们需要更高性价比的AI推理解决方案。只有这样,他们才能真正将神经网络模型全面应用在其批量化产品中。InferX X1 恰好满足了这类用户的需求。相比于目前行业的领军产品,InferX X1 可以为用户带来数十倍甚至上百倍的性价比提升。” Flex Logix 的创始人CEO Geoff Tate 在受访时这样表示。

Gforce Marketing公司的首席营销主任及SemiWiki杂志的撰稿人Mike Gianfagna先生认为:“Flex Logix此次推出的技术将为整个AI市场带来革命性的变化。InferX X1将显著拓宽现有的AI应用市场,将AI推理带入更为广阔的市场领域。其它推理解决方案在性价比方面目前很难与Flex Logix相匹敌。因此,这次发布的InferX X1将颠覆当前的AI市场格局。我们相信Flex Logix在未来会呈现指数级别的飞速成长。”

TIRIAS Research的首席分析官 Kevin Krewell表示:“TIRIAS Research相信,在数据中心内部和以外的各类应用场景中,针对机器学习模型的大规模部署才刚刚开始。我们是否可以在广阔的工业领域中大规模布局AI推理应用的关键性因素就在于芯片解决方案的功耗和成本效率。我们相信,Flex Logix推出的 InferX X1加速器和PCIe板将带给我们更高的能效比和性价比。”

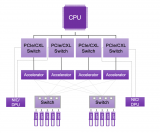

基于多项Flex Logix 的专有技术,InferX X1 采用了一种全新的架构,可以在较小面积内实现较高的吞吐量。其中,Flex Logix 专利的 XFLX可编程互联网络架构,也被应用于嵌入式FPGA技术,并在过去数年中被国内外多家知名公司所使用。其中包括 Dialog半导体、波音、桑迪亚国家实验室、以及大唐电信旗下的辰芯科技。除了 XFLX以外,InferX X1还用到了可重配置张量处理器。它由64个一维的张量处理器构成,可通过重新配置来高效地支持各种神经网络模型的运算。由于重配置的时间只有几个微秒,所以神经网络模型的每一层都可以拥有经过优化的数据路径。

InferX X1的批量生产芯片和配套软件将于2021年第二季度开始全面出货。用户样品及早期软件工具则计划于2021年第一季度开始对用户进行供货。目前,Flex Logix 可以向符合以下条件的先期用户提供样品芯片和软件,并进行基准测试支持。这些条件包括:需要有现成的基于 TensorFlow Lite 或者 ONNX 的神经网络模型,并有可在2021年进行批量生产的产品项目。相关的具体技术指标及价格指引也都将对这些用户提前提供。

更多相关信息请访问https://flex-logix.com。

具体技术指标

高达70% MAC 利用率,可使较小面积和较低成本处理高清图像和较大模型。

一维张量处理器(1D TPU)即一维脉动阵列

o 64B 输入张量

o 64 INT8 MACs

o 32 BF16 MACs

o 64Bx256B权重矩阵

o 一维脉动阵列每64个时钟周期可完成4096次乘加运算。

每颗X1芯片中的可重配置张量处理器由64个一维张量处理器(1D TPU)组成

o 可以将多个TPU配置成串联或者并联结构,以实现多种不同的张量运算。这种灵活性可以很有效地支持不断衍生的诸如3D卷积等新型运算,并保持较高性能。o 可编程互联网络架构可以很好地解决SRAM与TPU间的数据通路的竞争问题,达到非常高的数据交互速度。

eFPGA可编程逻辑可用于实现包括控制TPU运行的高性能状态机,以及各种运算符的控制逻辑

神经网络模型中的每一层都可被专门进行重配置;每一次重配置只需要几微秒的时间。

在处理当前层级的同时,下一层神经网络模型的配置及权重可在后台从DRAM中被加载;这可以极大减少由DRAM带宽限制所带来的计算的停顿。

Layer fusion功能可通过将一个以上的配置文件进行合并来降低DRAM延时。

仅使用较少的内存资源以降低成本:LPDDR4x DRAM, 总共14MB SRAM

x4 PCIe Gen 3 or Gen 4 可提供芯片与主机间的高速通信。

在16nm制程下芯片面积为54 mm2

倒装BGA封装尺寸为21 x 21 mm

InferX X1将于近期开始像部分用户进行样品芯片的出货,并计划于2021年第二季度开始进行批量产品的出货。

商业报价(1000-100万颗)

满足工业级或航空级温度要求的X1芯片也可向用户出货。

责任编辑:tzh

-

芯片

+关注

关注

456文章

50892浏览量

424377 -

机器人

+关注

关注

211文章

28468浏览量

207371 -

AI

+关注

关注

87文章

31000浏览量

269341

发布评论请先 登录

相关推荐

ADI收购Flex Logix,强化数字产品组合

今日看点丨ADI收购eFPGA公司Flex Logix;业界首款!湖北发布高性能车规级芯片DF30

ZS7606X内置MOS的高性能同步整流芯片中文手册

示波器探头x1和x10表示什么意思

示波器探头X1和X10对峰值电压的影响

芯品# 高性能计算芯片

技术巅峰!探秘国内高性能模拟芯片的未来发展

示波器探头X1和X10的区别

构建高性能计算芯片

多核架构高性能电机控制芯片

Flex Logix宣布高性能芯片InferX X1芯片出货

Flex Logix宣布高性能芯片InferX X1芯片出货

评论