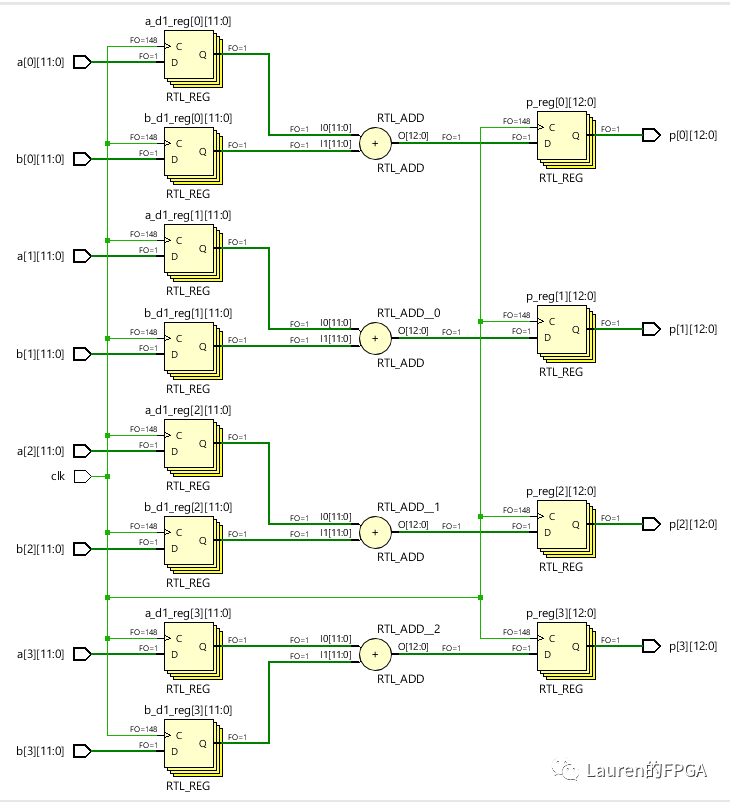

这里并行加法是指多个加法操作同时执行,这意味着需要消耗多个加法器。这里我们以4个12-bit数相加(加数和被加数均为12-bit,故和为13-bit,从而避免了溢出问题)。相应的电路图如下图所示。图中的RTL_ADD即为加法器,同时此电路对输入和输出数据均添加了流水寄存器。

此电路对应的RTL代码如下图所示,这里我们使用了SystemVerilog来描述。输入a和b均为4个12-bit数据构成的数组。输出p也是4个12-bit构成的数组。代码第17行至第23行是核心部分,包括了对输入、输出添加流水寄存器和加法操作。

责任编辑:lq

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电路图

+关注

关注

10346文章

10721浏览量

530971 -

加法器

+关注

关注

6文章

183浏览量

30137 -

数组

+关注

关注

1文章

417浏览量

25963

原文标题:并行加法的高效实现

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

高速并行总线的工作原理是什么 高速并行总线有哪些

多个数据通道的同时传输。与串行总线相比,并行总线在同一时间内能够传输多个数据位,从而提高了数据传输的速率。这种并行传输方式通常通过一组数据线来实现,每条线传输数据的一个位(bit)。为了确保数据的同步和完整性,

实现两个单一频率正弦波相加的加法器的芯片选取有什么特殊要求吗?opa2320可以吗?

实现两个单一频率正弦波相加的加法器的芯片选取有什么特殊要求吗?opa2320可以吗?

发表于 09-11 08:30

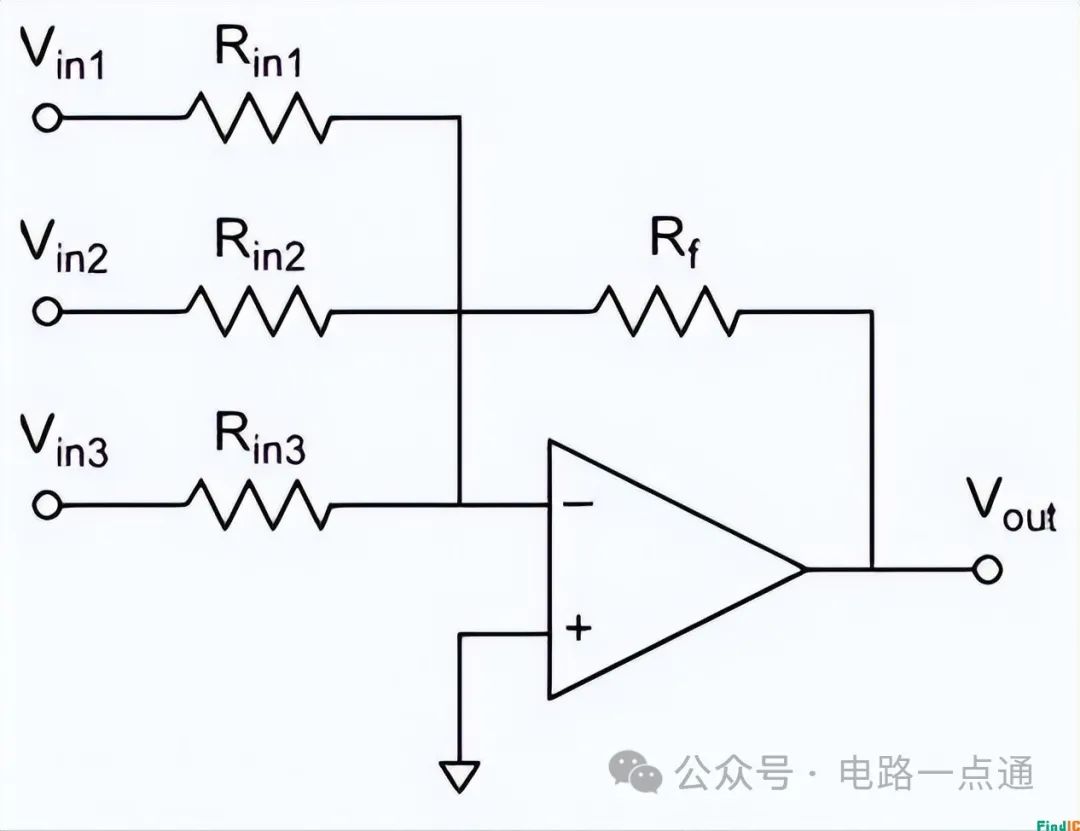

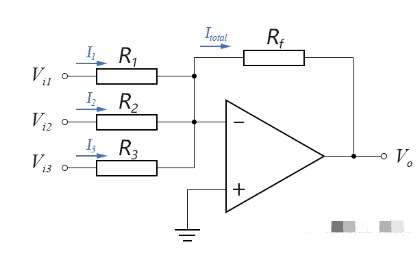

加法运放电路实验报告数据分析

加法运放电路实验报告的数据分析主要包括对实验结果的观察、与理论值的对比以及误差原因的分析。以下是一个基于常见加法运放电路实验的数据分析示例: 一、实验目的与原理 实验目的 :了解加法器的模拟实

在多FPGA集群上实现高级并行编程

今天我们看的这篇论文介绍了在多FPGA集群上实现高级并行编程的研究,其主要目标是为非FPGA专家提供一个成熟且易于使用的环境,以便在多个并行运行的设备上扩展高性能计算(HPC)应用。

边OTG边充电芯片如何实现充电与数据传输并行?

边OTG边充电芯片实现充电与数据传输并行的功能,主要依赖于其内部的设计和与USB Type-C接口标准的结合。

请问增益为1的加法器有哪些?

增益为1的加法器指的是输出信号的幅度与输入信号幅度相等的加法器。这类加法器在模拟电路设计中非常重要,因为它们在执行加法运算的同时,不会改变信号的幅度。

串行加法器和并行加法器的区别?

串行加法器和并行加法器是两种基本的数字电路设计,用于执行二进制数的加法运算。它们在设计哲学、性能特点以及应用场景上有着明显的区别。

同相加法器和反相加法器的区别是什么

同相加法器和反相加法器是运算放大器在模拟电路设计中常用的两种基本电路结构,它们在信号处理方面有着不同的特性和应用场景。

加法放大器的原理和应用

加法放大器,作为一种重要的电子电路设备,其在信号处理、音频混合、以及多种电子系统中发挥着关键作用。它基于放大器的线性特性,通过特定的电路设计,将多个输入信号进行相加,并输出放大后的信号。本文将对加法放大器的原理、特点、设计方法以及其在不同领域的应用进行详细的阐述。

verilog中for循环是串行执行还是并行执行

的for循环也是并行执行的。 Verilog中的for循环可以用来实现重复的操作,例如在一个时钟周期中对多个电路进行操作。在循环内部,多个语句可以同时执行,而不受循环次数的限制。这种并行执行的机制使得Verilog在硬件设计中非

反相加法运算电路原理介绍

反相加法运算电路利用运算放大器(通常简称为Op-Amp)的特性来实现多个输入信号的加法运算。每个输入信号都通过一个电阻连接到运算放大器的反相输入端,而运算放大器的同相输入端则接地或虚拟接地。输出电压

并行加法的高效实现

并行加法的高效实现

评论