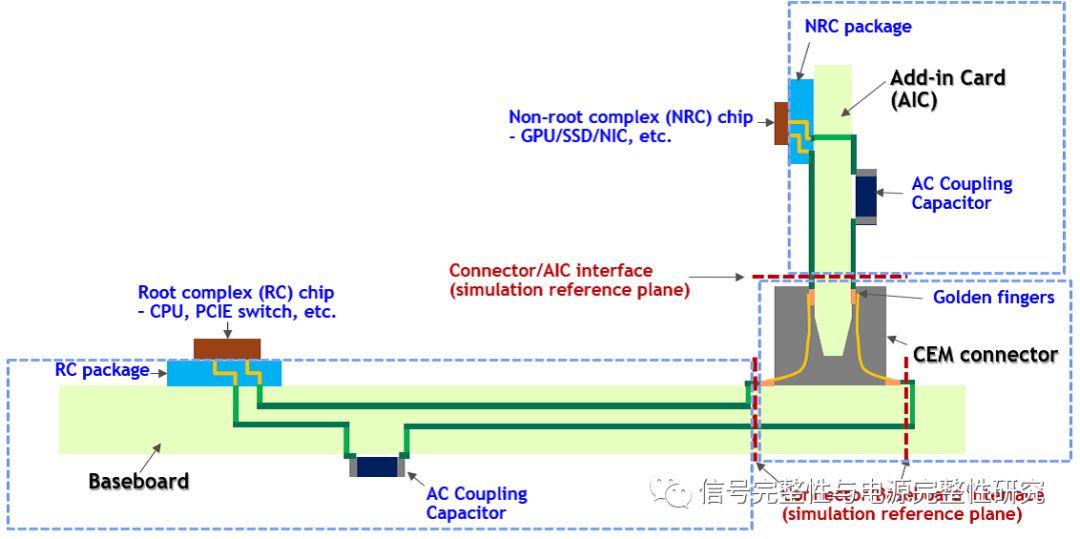

前言:PCIExpress base和CardElectro Mechanical(CEM)规范定义了用于桌面/服务器PCIe通道的拓扑结构。典型的通道包括Root Complex(CPU),Baseboard(主板),CEM连接器,Add-in Card(AIC)和Non-root complex(GPU / SSD / NIC)。交流耦合电容放置在靠近发射器的TX通道上。

PCIe Gen5相关规范预计将于2019年完成。数据速率从16 GT/s增加到32GT/s。该通道最多可包含2个CEM连接器,并且在母板和AIC上具有与Gen4类似的走线长度。(小于4 inch)

PCIE5.0 大致拓扑结构

本文讨论了Gen5的新性能要求,并描述了在连接器和AIC上实现这些要求的关键设计因素,上一代Gen4的设计要求简列如下:

1.使用更高等级的PCB材料,例如Megtron 6、 Megtron 7、IT-988G-SE材料需要多和加工厂沟通,其他要求可能具有挑战性,如无卤素、耐高温、超大板要求。

2.必须保持CEM连接器的向后代的兼容性,同时提高其性能。

要使用以前的PCIeCard,CEM连接器的外部外壳尺寸必须保持不变。可以修改连接器的内部尺寸以实现所需的损耗和串扰预算,但仍必须保持与旧AIC的兼容性。在连接器内部,我们可以改变触点的几何形状,以实现更好的插入损耗(IL)和回波损耗(RL),同时保持相同的形状因子以保持向后兼容性。这改善了配合接口区域的阻抗,同时将串扰提高到-40dB以下的水平。我们还可以在设计中添加有损塑料材料,以抑制不需要的接地模式共振。

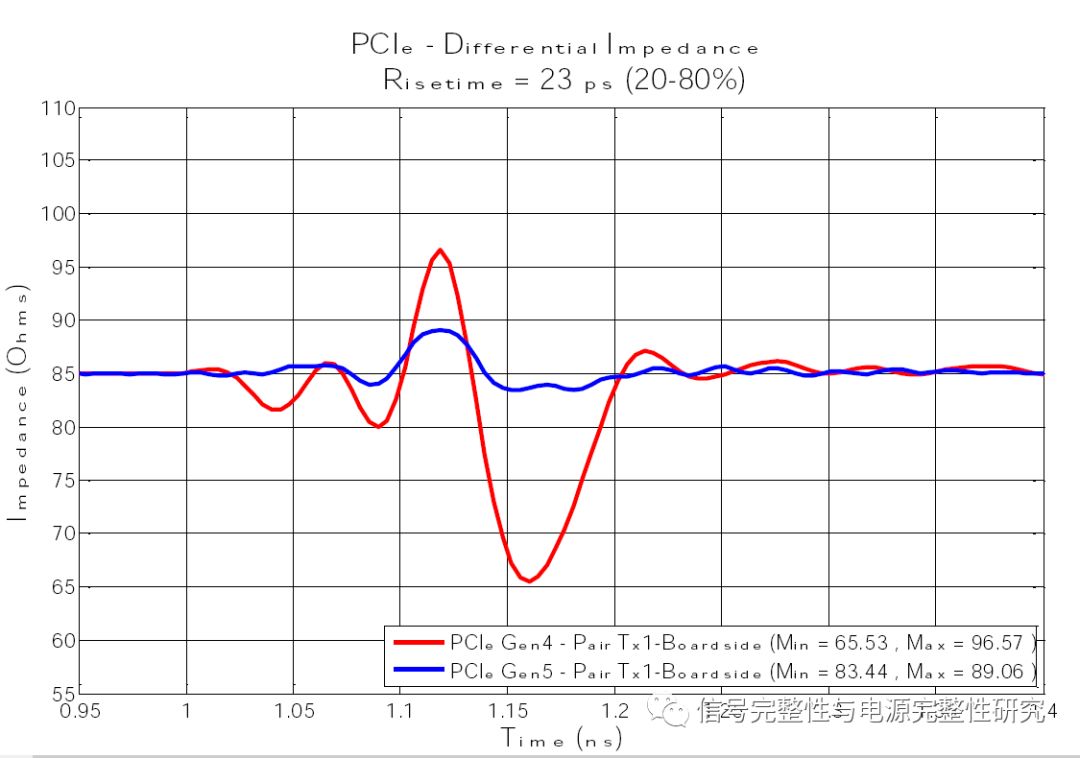

PCIe4 和PCIe 5 CEM连接器阻抗比对(Amphenol)

3.关于走线和VIA

对于AIC设计人员来说,第一个要问的关键问题是,“我们可以继续使用Gen5 PCB的微带走线技术吗?”虽然Gen4中的大多数基板已经使用带状线,但典型的AIC仍然使用微带来实现更简单的布线,通常短于4inch,性能可接受。由于所有球栅阵列(BGA)焊盘,金手指和背面安装的交流耦合电容都在表面层上,因此微带线选择可最大限度地减少通孔数量。历史上,微带通常表现出比带状线更低的损耗,因为通常使用更宽的线宽来保持85欧姆的阻抗。然而,对于Gen5速度,微带线具有与带状线相当的损耗,并且在阻抗控制,铜表面粗糙度,远端串扰和模式转换方面比带状线差得多。微带线对大批量生产(HVM),温度和湿度变化也更敏感。相比之下,带状线需要更多的过孔用于层过渡,并且可能需要通过back drill减少stub。造成布线通道狭窄,这可能需要增加PCB层数。

4.对于差分线阻抗公差控制,要求最好在+-5%,保证PCB阻抗平滑。

综上所述:对于每个产品系列,所有这些因素之间的权衡导致不同的设计选择。Gen5的回损目标也很难实现。通常,金手指和连接器接触处造成了阻抗不匹配。为了解决这个问题,我们建议改进引入线的形状和尺寸,以更好地保持阻抗并优化回波损耗,从而优化整体通道性能。

Gen5的新增设计规则分享如下:

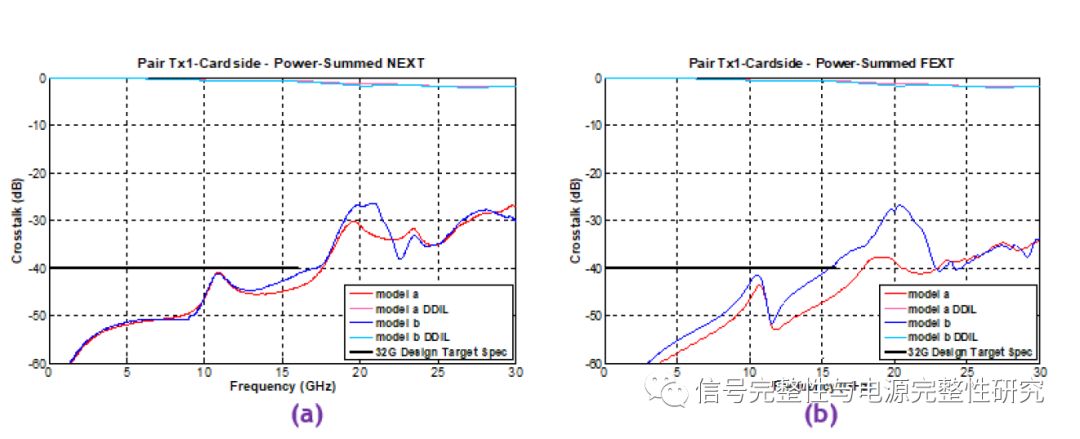

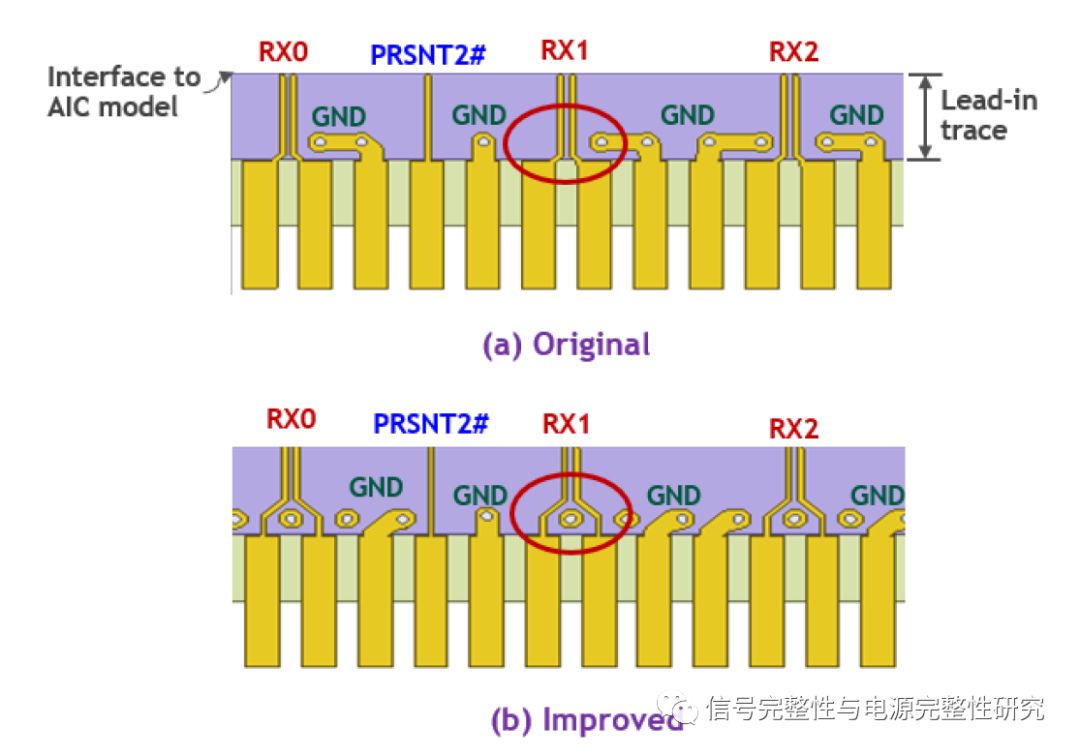

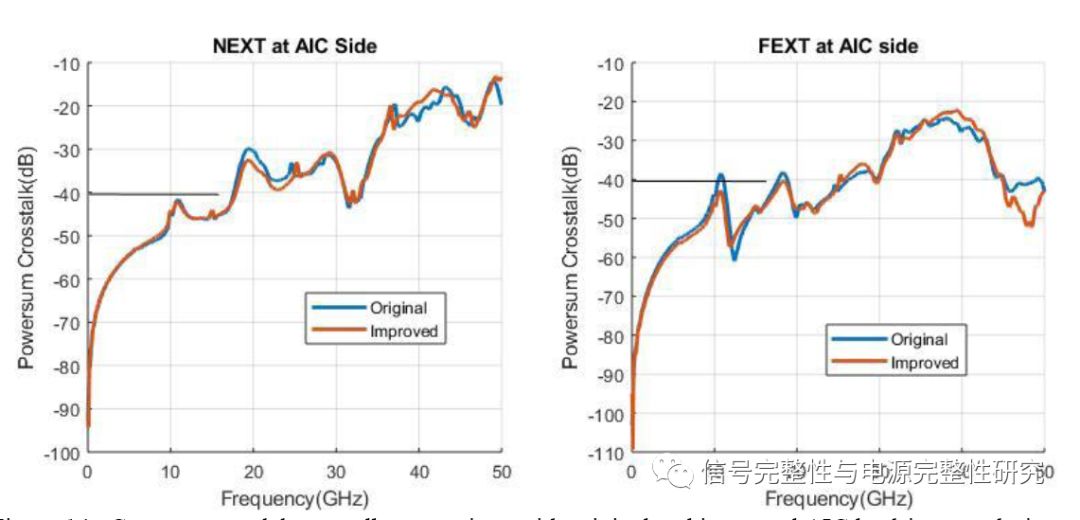

1.CEM连接器处的优化设计,如下图是2中fanout的方式

2种CEM连接器的出线方式

蓝色线显示原始结构的串扰,其中不包括额外的通孔。红色线显示了通过添加接地通孔可以实现的实质性改进,每个pin脚接另一端地,接地通孔用于改善接回流地路径的整体完整性。

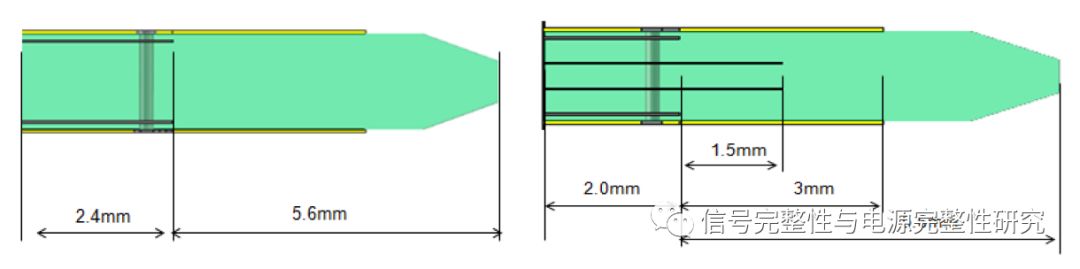

2.Add-in Card (AIC) 金手指部分尺寸的设计

PCIe 4 和PCIe 5AIC Card 尺寸比对

(Amphenol)

PCIe 4 和PCIe 5 AIC Card 内部尺寸比对

(Amphenol)

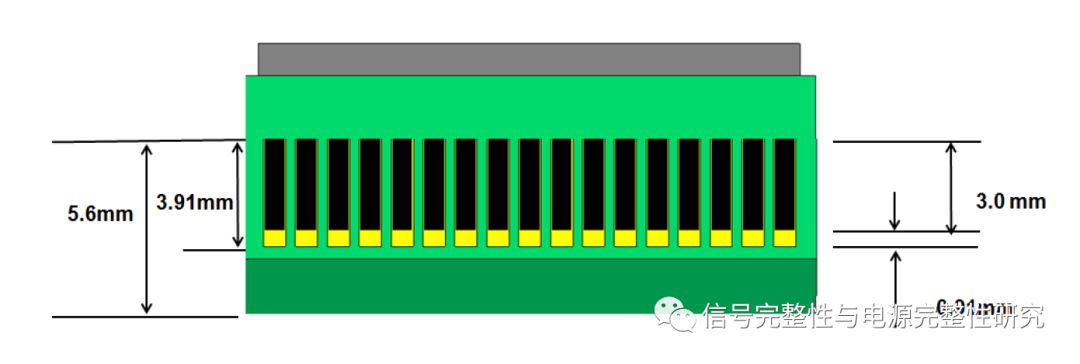

为了保持向后兼容性,根据PCIe Gen5规范,金边指的前边缘距离插卡边缘依然是5.6 mm。连接区域与较旧的Gen4版本相同。 PCIe Gen4和Gen5的AIC形状因子分别如上图所示

为了减少NEXT,在PCIe Gen5附加卡的边缘指区域下方增加了20.5mil的内部接地层。内部接地层位于PCB内部深处,并且不延伸到边缘手指处。

3. 金手指部分焊盘的设计

PCIe4 和PCIe 5 AIC Card 焊盘尺寸比对

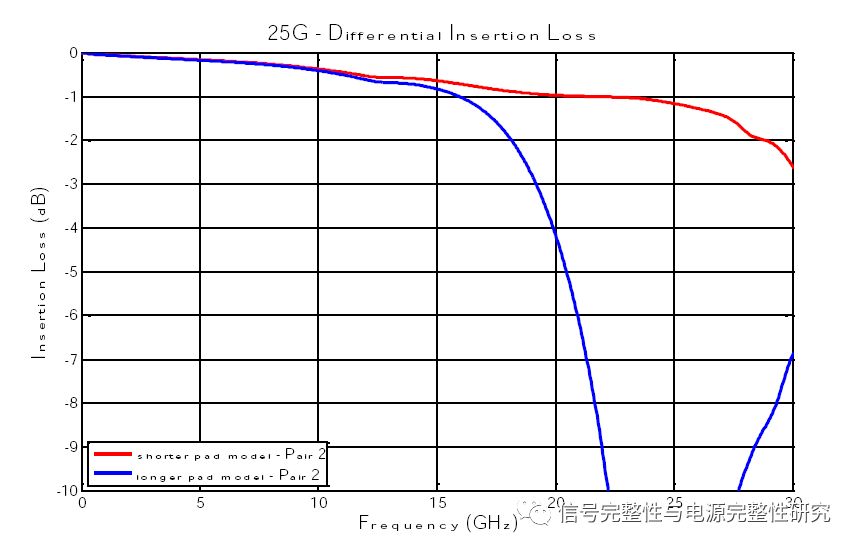

对比Gen4和Gen5之间的AIC焊盘尺寸。 PCIe Gen5焊盘尺寸为3.91x0.7 mm(上图中所示的黄色焊盘),PCIe Gen5的接触焊盘已减小到3.0x0.6 mm(图中所示的黑色焊盘)。更改接触垫尺寸可将擦拭距离从2.5mm(PCIe Gen4 SMT)减小到1.6 mm(PCIe Gen5 SMT),满足建议的最小擦拭距离1.43 mm且有足够的缓冲。 根据PCB制造商的意见,只要尺寸公差不低于+/- 0.038 mm,手指尺寸的减小就不会产生任何成本影响。 这种公差可由顶级PCB供应商维护。

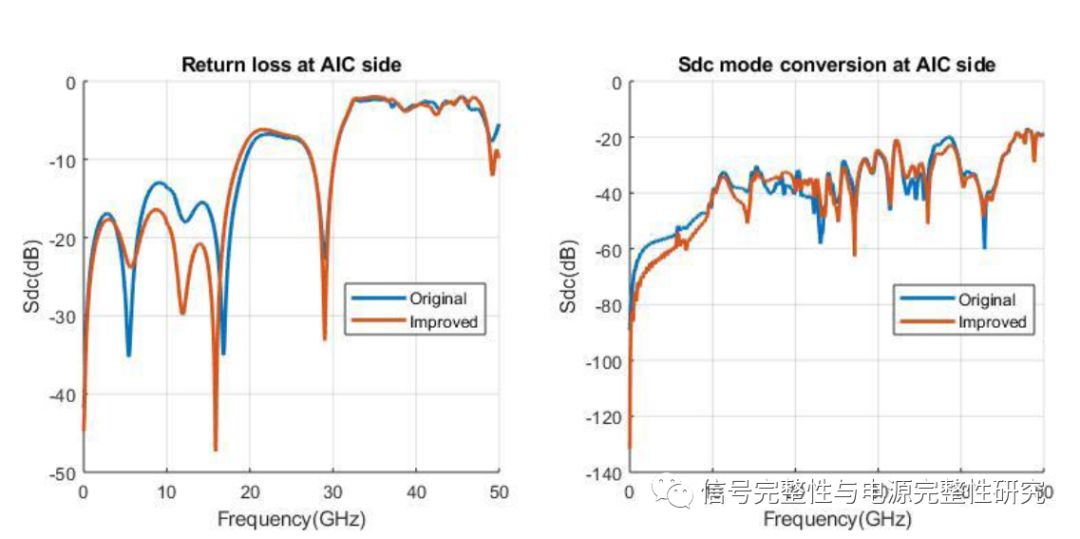

优化焊盘后损耗结果比对

4. AIC走线部分优化

使用上述优化结果,X-talk,插损,回损指标均有相应提高

5.使用带状线

微带线设计时,仿真结果显示出比带状线更差的X-talk,但对于具有20dB+损耗的全通道,它们在眼图边缘上的差异很小。

原文标题:SI-list【中国】PCIe Gen 5.0 PCB的设计与优化

文章出处:【微信公众号:信号完整性与电源完整性研究】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

pcb

+关注

关注

4333文章

23223浏览量

401854 -

cpu

+关注

关注

68文章

10942浏览量

213784 -

服务器

+关注

关注

12文章

9410浏览量

86439

原文标题:SI-list【中国】PCIe Gen 5.0 PCB的设计与优化

文章出处:【微信号:si-list,微信公众号:高频高速研究中心】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

PCIe 5.0市场加速渗透,PCIe 6.0研发到来

银翼新境 致态TiPro9000引领个人存储PCIe 5.0新时代

CDCDB800/803超低附加抖动、8路输出PCIe Gen1至Gen5时钟缓冲器

pcie 4.0与pcie 5.0的区别

在主板上优化PCIe通道设置

Xilinx 7系列FPGA PCIe Gen3的应用接口及特性

使用TMUXHS4412多路复用器的PCIe®Gen 4.0应用布局指南

使用TI PCI-Express Gen5.0转接驱动器进行眼图扫描

PCIe 5.0 SerDes 测试

美光研发出世界首款PCIe Gen6 SSD

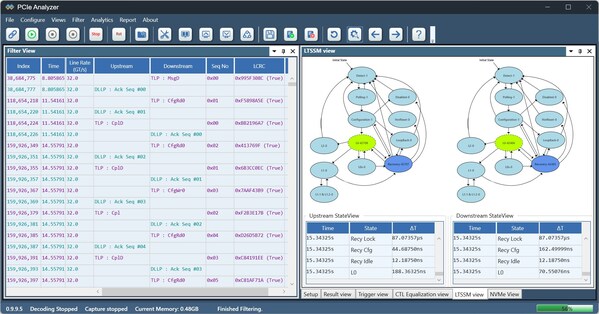

Prodigy Technovations推出功能强大的PCIe Gen5协议分析仪

HighPoint发布商用PCIe Gen5解决方案,最大可达960TB SSD容量

英韧科技:无AI不存储,国产PCIe 5.0主控率先发力

PCIe Gen5.0的设计与优化

PCIe Gen5.0的设计与优化

评论