1. 电阻电容的封装形式如何选择,有没有什么原则?比如,同样是 104 的电容有 0603、0805 的封装,同样是 10uF 电容有 3216,0805,3528 等封装形式,选择哪种封装形式比较合适呢?

我看到的电路里常用电阻电容封装:

电容:

0.01uF 可能的封装有 0603、0805

10uF 的封装有 3216、3528、0805

100uF 的有 7343

320pF 封装:0603 或 0805

电阻:

4.7K、10k、330、33 既有 0603 又有 0805 封装。

请问怎么选择这些封装?

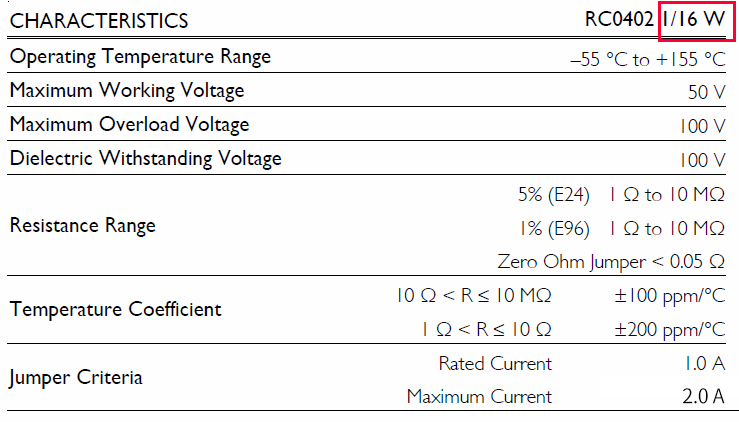

答:贴片的封装主要有:0201 1/20W 0402 1/16W 0603 1/10W 0805 1/8W 1206 1/4W

电容电阻外形尺寸与封装的对应关系是: 0402=1.0x0.5 0603=1.6x0.8 0805=2.0x1.2 1206=3.2x1.6 1210=3.2x2.5 1812=4.5x3.2 2225=5.6x6.5

电容本身的大小与封装形式无关,封装与标称功率有关。它的长和宽一般是用毫米表示的。但是型号是采用的英寸的表示方法。

选择合适的封装第一要看你的 PCB 空间,是不是可以放下这个器件。一般来说,封装大的器件会比较便宜,小封装的器件因为加工进度要高一点,有可能会贵一点,然后封装大的电容耐压值会比封装小的同容量电容耐压值高,这些都是要根据你实际的需要来选择的,另外,小封装的元器件对贴装要求会高一点,比如 SMT 机器的精度。如手机里面的电路板,因为空间有限,工作电压低,就可以选用 0402 的电阻和电容,而大容量的钽电容就多为 3216 等等大的封装

2. 有时候两个芯片的引脚(如芯片 A 的引脚 1,芯片 B 的引脚 2)可以直接相连,有时候引脚之间(如 A-1 和 B-2)之间却要加上一片电阻,如 22 欧,请问这是为什么?这个电阻有什么作用?电阻阻值如何选择?

答:这个电阻一般是串电阻,拿来做阻抗匹配的,当然也可以做降压用,用于 3.3V I/O 连接 2.5V I/O 类似的应用上面。阻值的选择要认真看 Datasheet,来计算

3. 藕合电容如何布置?有什么原则?是不是每个电源引脚布置一片 0.1uf?有时候看到 0.1uf 和 10uf 联合起来使用,为什么?

答:电容靠近电源脚。

补充一点看法:

在两个芯片的引脚之间串连一个电阻,一般都是在高速数字电路中,为了避免信号产生振铃(即信号的上升或下降沿附近的跳动)。原理是该电阻消耗了振铃功率,也可以认为它降低了传输线路的 Q 值。

通常在数字电路设计中要真正做到阻抗匹配是比较困难的,原因有二:1、实际的印制板上连线的阻抗受到面积等设计方面的限制;2、数字电路的输入阻抗和输出阻抗不象模拟电路那样基本固定,而是一个非线性的东西。

实际设计时,我们常用 22 到 33 欧姆的电阻,实践证明,在此范围内的电阻能够较好地抑制振铃。但是事物总是两面的,该电阻在抑制振铃的同时,也使得信号延时增加,所以通常只用在频率几兆到几十兆赫兹的场合。频率过低无此必要,而频率过高则此法的延时会严重影响信号传输。另外,该电阻也往往只用在对信号完整性要求比较高的信号线上,例如读写线等,而对于一般的地址线和数据线,由于芯片设计总有一个稳定时间和保持时间,所以即使有点振铃,只要真正发生读写的时刻已经在振铃以后,就无甚大影响。

前面已经补充了一点,再补充一点:关于接地问题。

接地是一个极其重要的问题,有时关系到设计的成败。

首先要明确的是,所有的接地都不是理想的,在任何时候都具有分布电阻与分布电感,前者在信号频率较低时起作用,后者则在信号频率高时成为主要影响因素。由于上述分布参数的存在,信号在经过地线的时候,会产生压降以及磁场。若这些压降或磁场(以及由该磁场引起的感应电压)耦合到其它电路的输入,就可能会被放大(模拟电路中)或影响信号完整性(数字电路中)。所以,一般要求在设计时就考虑这些影响,有一个大致的原则如下:

1、在频率较低的电路中(尤其是模拟电路或模数混合电路中的模拟部分),采用单点接地,即各级放大器的地线(包括电源线)分别接到电源输出端,成为星形连接,并且在这个星的节点上接一个大电容。这样做的目的是避免信号在地线上的压降耦合到其他放大器中。

2、在模拟电路中(尤其是小信号电路)要避免出现地线环,因为环状的地线会产生感应电流,此电流造成的感应电势是许多干扰信号的来源。

3、如果是单纯的数字电路(包括模数混合电路中的数字部分)且信号频率不高(一般不超过 10 兆),可以共用一组电源与地线,但是必须注意每个芯片的退耦电容必须靠近芯片的电源与地引脚。

4、在高速的数字电路(例如几十兆的信号频率)中,必须采取大面积接地,即采用 4 层以上的印制板,其中有一个单独的接地层。这样做的目的是给信号提供一个最短的返回路径。由于高速数字信号具有很高的谐波分量,所以此时地线与信号线之间构成的回路电感成为主要影响因素,信号的实际返回路径是紧贴在信号线下面的,这样构成的回路面积最小(从而电感最小)。大面积接地提供了这样的返回路径的可能性,而采用其他的接地方式均无法提供此返回路径。需要注意的是,要避免由于过孔或其他器件在接地平面上造成的绝缘区将信号的返回路径割断(地槽),若出现这种情况,情况会变得十分糟糕。

5、高频模拟电路,也要采取大面积接地。但是由于此时的信号线要考虑阻抗匹配问题,所以情况更复杂一些,在这里就不展开了。

审核编辑 黄昊宇

-

电阻

+关注

关注

86文章

5464浏览量

171608 -

电容

+关注

关注

99文章

5991浏览量

149956 -

封装

+关注

关注

126文章

7767浏览量

142696

发布评论请先 登录

相关推荐

电阻电容的封装形式如何选择?有哪些原则需考虑

电阻电容的封装形式如何选择?有哪些原则需考虑

评论