一、PCB 的内层是如何制作的?

由于 PCB 制造复杂的工艺流程,在智能制造规划与建设时,需考虑工艺、管理的相关工作,进而再进行自动化、信息化、智能化布局。

1、工艺流程分类

按 PCB 层数不同,分为单面板、双面板、多层板,这三种板子流程不太相同。

单面和双面板没有内层流程,基本是开料——钻孔——后续流程。

多层板会有内层流程

1)单面板工艺流程

开料磨边→钻孔→外层图形→(全板镀金)→蚀刻→检验→丝印阻焊→(热风整平)→丝印字符→外形加工→测试→检验

2)双面板喷锡板工艺流程

开料磨边→钻孔→沉铜加厚→外层图形→镀锡、蚀刻退锡→二次钻孔→检验→丝印阻焊→镀金插头→热风整平→丝印字符→外形加工→测试→检验

3)双面板镀镍金工艺流程

开料磨边→钻孔→沉铜加厚→外层图形→镀镍、金去膜蚀刻→二次钻孔→检验→丝印阻焊→丝印字符→外形加工→测试→检验

4)多层板喷锡板工艺流程

开料磨边→钻定位孔→内层图形→内层蚀刻→检验→黑化→层压→钻孔→沉铜加厚→外层图形→镀锡、蚀刻退锡→二次钻孔→检验→丝印阻焊→镀金插头→热风整平→丝印字符→外形加工→测试→检验

5)多层板镀镍金工艺流程

开料磨边→钻定位孔→内层图形→内层蚀刻→检验→黑化→层压→钻孔→沉铜加厚→外层图形→镀金、去膜蚀刻→二次钻孔→检验→丝印阻焊→丝印字符→外形加工→测试→检验

6)多层板沉镍金板工艺流程

开料磨边→钻定位孔→内层图形→内层蚀刻→检验→黑化→层压→钻孔→沉铜加厚→外层图形→镀锡、蚀刻退锡→二次钻孔→检验→丝印阻焊→化学沉镍金→丝印字符→外形加工→测试→检验

1、内层制作(图形转移)

内层:裁板,内层前处理,压膜,曝光,DES 连线

切料(裁板 -Board Cut)

1)开料裁板

目的: 按照订单要求将大料切成 MI 规定的大小(依制前设计所规划要求,将基板材料裁切成工作所需尺寸)

主要原物料:基板,锯片

基板是由铜片和绝缘层压合而成,依要求有不同板厚规格,依照铜厚可分为 H/H,1OZ/1OZ,2OZ/2OZ 等种类

注意事项:

a. 避免板边巴里影响品质,裁切后进行磨边,圆角处理

b. 考虑涨缩影响,裁切板送下制程前进行烘烤

c. 裁切须注意机械方向一致原则

磨边 / 圆角:通过机械打磨去除开料时板四边的直角留下的玻璃纤维,以减少在后工序生产过程中擦花 / 划伤板面,造成品质隐患

烤板:通过烘烤去除水汽和有机挥发物,释放内应力,促进交联反应,增加板料尺寸稳定性,化学稳定性和机械强度

控制点:

板料:拼板尺寸,板厚,板料类型,铜厚

操作:烤板时间 / 温度,叠板高度

(2)裁板后内层制作

作用及原理:

经过磨板粗化的内层铜板,经磨板干燥,贴上干膜 IW 后,利用 UV 光(紫外线)照射,曝光后的干膜变硬,遇弱碱不能溶解,遇强碱能溶解,而未曝光的部分遇弱碱能溶解掉,内层线路就是利用该物料的特性将图形转移到铜面上来的,即图像转移。

Detail :(在曝光区域抗蚀剂中的感光起始剂吸收光子分解成游离基,游离基引发单体发生交联反应生成不溶于稀碱的空间网状大分子结构,而未曝光部分因未发生反应可溶于稀碱。

利用二者在同种溶液中具备不同溶解性能从而将底片上设计的图形转移到基板上即完成图像转移)。

线路图形对温湿度的条件要求较高,一般要求温度 22+/-3℃,湿度 55+/-10%,以防止菲林的变形。对空气中的尘埃度要求高,随制作的线路密度增大及线路越小,含尘量小于等于 1 万级以上。

物料介绍:

干膜:干膜光致蚀剂简称干膜(Dry film)为水溶性阻剂膜,厚度一般有 1.2mil ,1.5mil 和 2mil 等,分聚酯保护膜,聚乙烯隔膜和感光膜三层。聚乙烯隔膜的作用是当卷状干膜在运输及储存时间中,防止其柔软的阻膜剂与聚乙烯保护膜之表面发生沾黏。而保护膜可防止氧气渗入阻剂层与其中自由基产生意外反应而使其光聚反应,未经聚合反应的干膜则容易被碳酸钠溶液冲脱。

湿膜:湿膜为一种单组分液态感光膜,主要由高感光树脂,感光剂,色料,填料及少量溶剂组成,生产用粘度 10-15dpa.s,具有抗蚀性及抗电镀性,湿膜涂覆方式有网印,喷涂等方式。

流程介绍:

干膜成像法,生产流程如下:

前处理——压膜——曝光——显影——蚀刻——去膜

前处理(Pretreate)

目的:去除铜面上的污染物如油脂氧化层等杂质,增加铜面的粗糙度,以利于后续的压膜制程

主要原物料:刷轮

前处理方式:

(1)喷砂研磨法

(2)化学处理法

(3)机械研磨法

化学处理法的基本原理:以化学物质如 SPS 等酸性物质均匀咬蚀铜表面,去除铜表面的油脂及氧化物等杂质。

化学清洗:

用碱溶液去除铜表面的油污,指印及其他有机污物,然后用酸性溶液去除氧化层和原铜基材上未防止铜被氧化的保护涂层,最后再进行微蚀处理以得到与干膜具有优良粘附性能的充分粗化的表面。

控制要点:

a. 磨板速度(2.5-3.2mm/min)

b. 磨痕宽度(500#针刷磨痕宽度:8-14mm ,800# 不织布磨痕宽度:8-16mm),水磨实验,烘干温度(80-90℃)

压膜(Lamination)

目的:将经处理之基板铜面透过热压方式贴上抗蚀干膜。

主要原物料:干膜(Dry Film),溶液显像型,半水溶液显像型,水溶性干膜主要由其组成中含有机酸根,会与强碱反应使之成为有机酸根类,可被谁溶掉。

原理:辘干膜(贴膜):先从干膜上剥下聚乙烯保护膜,然后在加热加压的条件下将干膜抗蚀剂粘贴在覆铜箔板上,干膜中的抗蚀剂层受热变软,流动性增加,借助于热压辘的压力和抗蚀剂中粘结剂的作用完成贴膜。

辘干膜三要素:压力,温度,传递速度

控制要点:

a. 贴膜速度(1.5+/-0.5m/min),贴膜压力(5+/-1kg/cm2),贴膜温度(110+/——10℃),出板温度(40-60℃)

b. 湿膜涂布:油墨粘度,涂布速度,涂布厚度,预烤时间 / 温度(第一面 5-10 分钟,第二面 10-20 分钟)

曝光(Exposure)

目的:经光源作用将原始底片上的图像转移到感光底板上。

主要原物料:底片内层所用底片为负片,即白色透光部分发生聚合反应,黑色部分则因不透光,不发生发应,外层所用的底片为正片,与内层所用底片相反。

干膜曝光原理:在曝光区域抗蚀剂中的感光起始剂吸收光子分解成游离基,游离基引发单体发生交联反应生成不溶于稀碱的空间网状大分子结构。

控制要点:对位精准,曝光能量,曝光光尺(6-8 级盖膜),停留时间。

显影(Developing)

目的:用碱液作用将未发生化学反应之干膜部分冲掉。

主要原物料:Na2CO3

使用将未发生聚合反应之干膜冲掉,而发生聚合反应之干膜则保留在板面上作为蚀刻时之抗蚀保护层。

显影原理:感光膜中未曝光部分的活性基团与稀碱溶液发生反应生成可溶性物质而溶解下来,从而把未曝光的部分溶解下来,而曝光部分的干膜不被溶解。

控制要点:

a. 显影速度(1.5-2.2m/min),显影温度(30+/-2℃)

b. 显影压力(1.4-2.0Kg/Cm2),显影液浓度(N2CO3 浓度 0.85-1.3%)

蚀刻(Etching)

目的:利用药液将显影后露出来的铜蚀掉,形成内层线路图形。

主要原物料:蚀刻药液(CuCl2)

内层蚀刻原理:内层图形转移制程中,D/F 或油墨是作为抗蚀刻,有抗电镀之用或抗蚀刻之用,因此大部分选择酸性蚀刻(干膜 / 湿膜覆盖电路图形的表面。

防止铜蚀刻:其他裸露在基板上不要的铜,以化学反应将予以除去,使其形成所需的线路图形,线路图形蚀刻完成再以氢氧化钠溶液退干膜 / 湿膜)。

常见问题:蚀刻不净,蚀刻过度,线幼,开路,短路。

控制要点:

a. 蚀刻:速度,温度(48-52℃),压力(1.2-2.5Kg/cm2)

b. 退膜:44-54℃,8-12%NaOH 溶液

去膜(Strip)

目的:利用强碱将保护铜面之抗蚀层剥掉,露出线路图形。

主要原料:NaOH

二、细数射频板叠层结构、以及布线要求

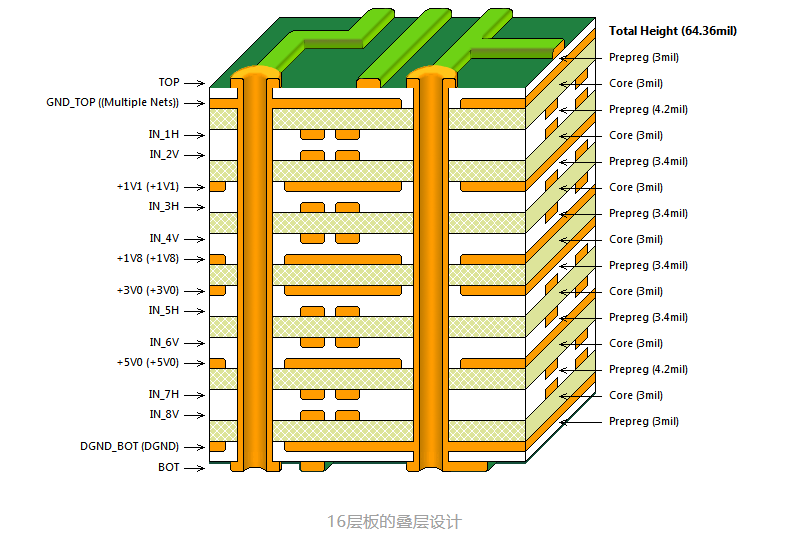

1、射频板叠层结构

RF PCB 单板的叠层结构除了要考虑射频信号线的阻抗以外,还需要考虑散热、电流、器件、EMC、结构和趋肤效应等问题,通常我们在多层印制板分层及堆叠中遵徇以下一些基本原则:

A) RF PCB 的每层都大面积铺地,没有电源平面,RF 布线层的上下相邻两层都应该是地平面。

即使是数模混合板,数字部分可以存在电源平面,但是 RF 区仍然要满足每层都大面积铺地的要求。

B) 对 RF 双面板来说,顶层为信号层,底层为地平面。

四层 RF 单板,顶层为信号层,第二层和第四层为地平面,第三层走电源、控制线。特殊情况在第三层可以走一些 RF 信号线。更多层的 RF 单板,以此类推。

C) 对于 RF 背板来说,上下两表面层都是地面,为了减小过孔及连接器的引起的阻抗不连续性,第二、三、四、五层走数字信号。

而其它靠底面的带状线层都是 底面 信号层。同样,RF 信号层上下相邻两层该是地面,每层都应该大面积铺地。

D) 对于大功率、大电流的射频板应该将 RF 主链路放置到顶层并且用较宽的微带线连接。

这样有利于散热和减小能量损耗,减少导线腐蚀误差。

E) 数字部分的电源平面应靠近接地平面,并且安排在接地平面之下。

这样可以利用两金属平板间的电容作电源的平滑电容,同时接地平面还对电源平面上分布的辐射电流起到屏蔽作用。

具体叠层方法和平面分割要求可以参照 EDA 设计部颁布的《20050818 印刷电路板设计规范——EMC 要求》,以网上标准为准。

2、射频板布线要求

2.1 转角

射频信号走线如果走直角,拐角处的有效线宽会增大,阻抗不连续而引起反射。故要对转角进行处理,主要为切角和圆角两种方法。

(1) 切角适用于比较小的弯角,切角的适用频率可达 10GHz。

(2) 圆弧角的半径应足够大,一般来说,要保证:R>3W。

2.2 微带线布线

PCB 顶层走射频信号,射频信号下面的平面层必须是完整的接地平面,形成微带线结构。要保证微带线的结构完整性,有以下要求:

(1) 微带线两边的边缘离下方地平面边缘至少要有 3W 宽度。且在 3W 范围内,不得有非接地的过孔。

(2) 微带线至屏蔽壁距离应保持为 2W 以上。(注:W 为线宽)。

(3) 同层内非耦合微带线要做包地铜皮处理并在地铜皮上加地过孔,孔间距小于λ/20,均匀排列整齐。

地铜箔边缘要光滑、平整、禁止尖锐毛刺。建议包地铜皮边缘离微带线边缘大于等于 1.5W 的宽度或者 3H 的宽度,H 表示微带衬底介质的厚度。

(4) 禁止 RF 信号走线跨第二层的地平面缝隙。

2.3 带状线布线

射频信号有时要从 PCB 的中间层穿过,常见的为从第三层走,第二层和第四层必须是完整的接地平面,即偏心带状线结构。应保证带状线的结构完整性须要求:

(1) 带状线两边的边缘离上下地平面边缘至少 3W 宽度,且在 3W 范围内,不得有非接地的过孔。

(2) 禁止 RF 带状线跨上下层的地平面缝隙。

(3) 同层内带状线要做包地铜皮处理并在地铜皮上加地过孔,孔间距小于λ/20,均匀排列整齐。地铜箔边缘要光滑、平整、禁止尖锐毛刺。

建议包地铜皮边缘离带状线边缘大于等于 1.5W 的宽度或者 3H 的宽度,H 表示带状线上下介质层总厚度。

(4) 如果带状线要传输大功率信号,为了避免 50 欧姆线宽过细,通常要将带状线区域的上下两个参考平面的铜皮做挖空处理,挖空宽度为带状线的总介质厚度的 5 倍以上,如果线宽仍然达不到要求,则再将上下相邻的第二层参考面挖空。

审核编辑 黄昊宇

-

pcb

+关注

关注

4335文章

23229浏览量

401943

发布评论请先 登录

相关推荐

PCB内层制作流程以及射频板叠层布线

PCB内层制作流程以及射频板叠层布线

评论