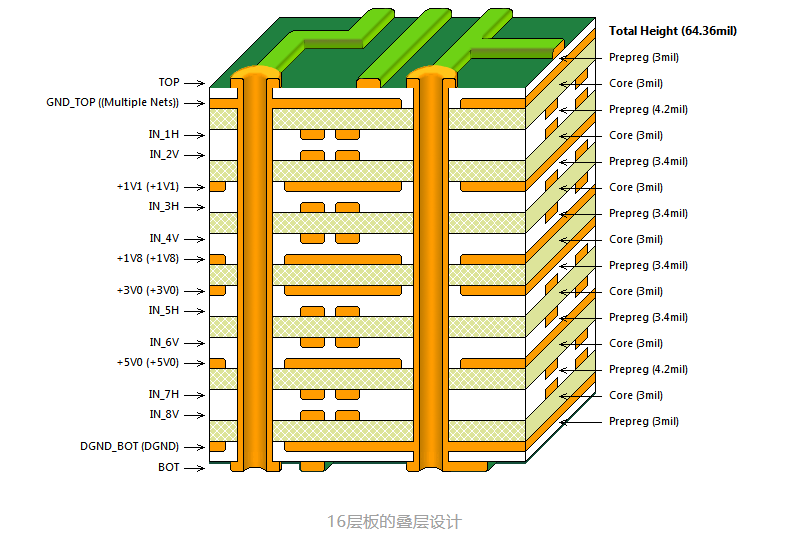

总的来说叠层设计主要要遵从两个规矩:

1. 每个走线层都必须有一个邻近的参考层(电源或地层);

2. 邻近的主电源层和地层要保持最小间距,以提供较大的耦合电容;

下面列出从两层板到十层板的叠层:

一、单面 PCB 板和双面 PCB 板的叠层

对于两层板来说,由于板层数量少,已经不存在叠层的问题。控制 EMI 辐射主要从布线和布局来考虑;

单层板和双层板的电磁兼容问题越来越突出。造成这种现象的主要原因就是因是信号回路面积过大,不仅产生了较强的电磁辐射,而且使电路对外界干扰敏感。要改善线路的电磁兼容性,最简单的方法是减小关键信号的回路面积。

关键信号:从电磁兼容的角度考虑,关键信号主要指产生较强辐射的信号和对外界敏感的信号。能够产生较强辐射的信号一般是周期性信号,如时钟或地址的低位信号。对干扰敏感的信号是指那些电平较低的模拟信号。

单、双层板通常使用在低于 10KHz 的低频模拟设计中:

1 在同一层的电源走线以辐射状走线,并最小化线的长度总和;

2 走电源、地线时,相互靠近;在关键信号线边上布一条地线,这条地线应尽量靠近信号线。这样就形成了较小的回路面积,减小差模辐射对外界干扰的敏感度。当信号线的旁边加一条地线后,就形成了一个面积最小的回路,信号电流肯定会取道这个回路,而不是其它地线路径。

3 如果是双层线路板,可以在线路板的另一面,紧靠近信号线的下面,沿着信号线布一条地线,一线尽量宽些。这样形成的回路面积等于线路板的厚度乘以信号线的长度。

二、四层板的叠层

推荐叠层方式:

1. SIG-GND(PWR)-PWR (GND)-SIG;

2. GND-SIG(PWR)-SIG(PWR)-GND;

对于以上两种叠层设计,潜在的问题是对于传统的 1.6mm(62mil)板厚。层间距将会变得很大,不仅不利于控制阻抗,层间耦合及屏蔽;特别是电源地层之间间距很大,降低了板电容,不利于滤除噪声。

对于第一种方案,通常应用于板上芯片较多的情况。这种方案可得到较好的 SI 性能,对于 EMI 性能来说并不是很好,主要要通过走线及其他细节来控制。主要注意:地层放在信号最密集的信号层的相连层,有利于吸收和抑制辐射;增大板面积,体现 20H 规则。

对于第二种方案,通常应用于板上芯片密度足够低和芯片周围有足够面积(放置所要求的电源覆铜层)的场合。此种方案 PCB 的外层均为地层,中间两层均为信号 / 电源层。信号层上的电源用宽线走线,这可使电源电流的路径阻抗低,且信号微带路径的阻抗也低,也可通过外层地屏蔽内层信号辐射。从 EMI 控制的角度看, 这是现有的最佳 4 层 PCB 结构。主要注意:中间两层信号、电源混合层间距要拉开,走线方向垂直,避免出现串扰;适当控制板面积,体现 20H 规则;如果要控 制走线阻抗,上述方案要非常小心地将走线布置在电源和接地铺铜岛的下边。另外,电源或地层上的铺铜之间应尽可能地互连在一起,以确保 DC 和低频的连接性。

三、六层板的叠层

一、 对于芯片密度较大、时钟频率较高的设计应考虑 6 层板的设计

推荐叠层方式:

1.SIG-GND-SIG-PWR-GND-SIG;

对于这种方案,这种叠层方案可得到较好的信号完整性,信号层与接地层相邻,电源层和接地层配对,每个走线层的阻抗都可较好控制,且两个地层都是能良好的吸收磁力线。并且在电源、地层完整的情况下能为每个信号层都提供较好的回流路径。

2.GND-SIG-GND-PWR-SIG -GND;

对于这种方案,该种方案只适用于器件密度不是很高的情况,这种叠层具有上面叠层的所有优点,并且这样顶层和底层的地平面比较完整,能作为一个较好的屏蔽层 来使用。需要注意的是电源层要靠近非主元件面的那一层,因为底层的平面会更完整。因此,EMI 性能要比第一种方案好。

小结:对于六层板的方案,电源层与地层之间的间距应尽量减小,以获得好的电源、地耦合。但 62mil 的板厚,层间距虽然得到减小,还是不容易把主电源与地 层之间的间距控制得很小。对比第一种方案与第二种方案,第二种方案成本要大大增加。因此,我们叠层时通常选择第一种方案。设计时,遵循 20H 规则和镜像层 规则设计

四、八层板的叠层

八层板通常使用下面三种叠层方式

A:由于差的电磁吸收能力和大的电源阻抗导致这种不是一种好的叠层方式。它的结构如下:

1.Signal 1 元件面、微带走线层

2.Signal 2 内部微带走线层,较好的走线层(X 方向)

3.Ground

4.Signal 3 带状线走线层,较好的走线层(Y 方向)

5.Signal 4 带状线走线层

6.Power

7.Signal 5 内部微带走线层

8.Signal 6 微带走线层

B:是第三种叠层方式的变种,由于增加了参考层,具有较好的 EMI 性能,各信号层的特性阻抗可以很好的控制

1.Signal 1 元件面、微带走线层,好的走线层

2.Ground 地层,较好的电磁波吸收能力

3.Signal 2 带状线走线层,好的走线层

4.Power 电源层,与下面的地层构成优秀的电磁吸收

5.Ground 地层

6.Signal 3 带状线走线层,好的走线层

7.Power 地层,具有较大的电源阻抗

8.Signal 4 微带走线层,好的走线层

C:最佳叠层方式,由于多层地参考平面的使用具有非常好的地磁吸收能力。

1.Signal 1 元件面、微带走线层,好的走线层

2.Ground 地层,较好的电磁波吸收能力

3.Signal 2 带状线走线层,好的走线层

4.Power 电源层,与下面的地层构成优秀的电磁吸收

5.Ground 地层

6.Signal 3 带状线走线层,好的走线层

7.Ground 地层,较好的电磁波吸收能力

8.Signal 4 微带走线层,好的走线层

对于如何选择设计用几层板和用什么方式的叠层,要根据板上信号网络的数量,器件密度,PIN 密度,信号的频率,板的大小等许多因素。对于这些因素我们要综 合考虑。对于信号网络的数量越多,器件密度越大,PIN 密度越大,信号的频率越高的设计应尽量采用多层板设计。为得到好的 EMI 性能最好保证每个信号层都 有自己的参考层。

审核编辑 黄昊宇

-

pcb

+关注

关注

4329文章

23188浏览量

400559

发布评论请先 登录

相关推荐

晶科能源钙钛矿/TOPCon叠层电池效率破纪录

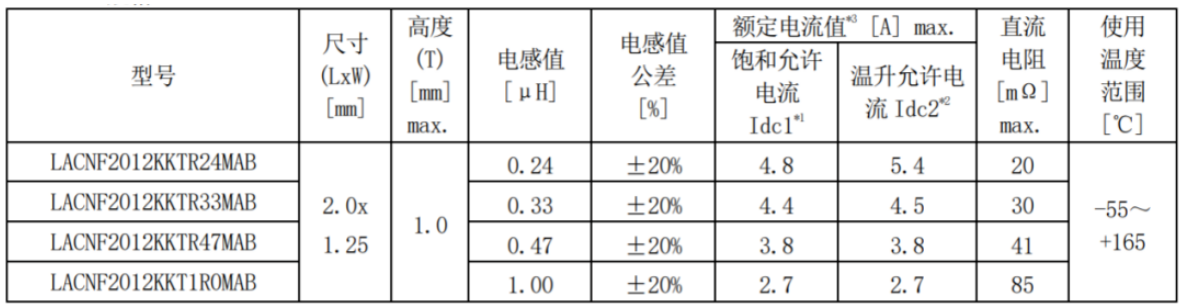

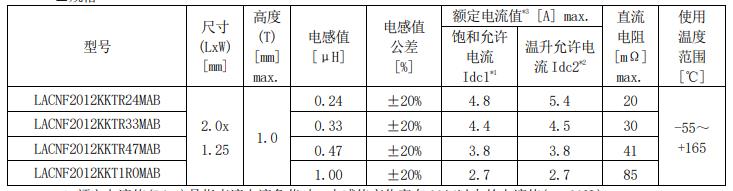

如何根据贴片叠层电感参数进行选型

AMEYA360:太阳诱电应对 165℃的叠层金属类功率电感器实现商品化!

晶科能源获批浙江省先进叠层光伏技术重点实验室认定

一文详解九层板PCB结构

绕线电感和叠层电感的区别是什么

太阳诱电:应对165℃的叠层金属类功率电感器实现商品化

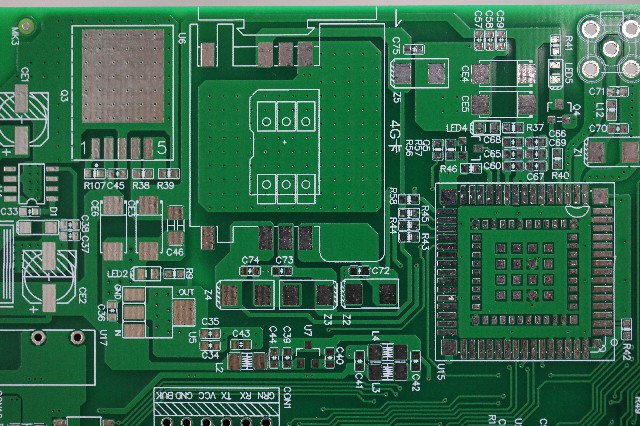

Cadence快板PCB培训

晶科能源基于N型TOPCon的钙钛矿叠层电池转化效率再创纪录

谷景揭秘贴片叠层电感精度是不是越高越好

钙钛矿叠层电池:Topcon与HJT底电池性能对比研究

简述PCB叠层设计

简述PCB叠层设计

评论