随着服务器、计算机机器性能需求的逐渐提高,高速率、高频率 DDR 也开始应用于高端设计中。但目前针对 DDR 设计资料非常少,特别是针对信号完整性(SI)方面的,随着 DDR 速率的提高,极易容易引起电路的 SI 问题,信号测试验证也变得越来越困难。一般 DDR 信号测试、仿真验证,大多数用 SPEED2000,大家在学习 DDR 仿真前,可以先补充 SPEED2000 的时域波形仿真和 IBIS 仿真基础。今天我们以 DDR 内存条为例,进行简单的 DDR SI 仿真供大家学习借鉴。

下面是在 Cadence 中 SPEED2000,具体软件操作使用步骤,如下所示:

1. Cadence17.2 的 SPPED2000 在 Generator 里

2. 点击 Generator 后会选择 license,这里注意要全选,否则后面 DDR 仿真会报 spd error

3. 选择 DDR Simulaion,点击“load layout file”,选择 layout 文件,支持 brd 文件,这里以 cadence 的内存条模板学习。

4. 选择 enable DDR Simulation Mode,点击 set up components and bus group,这里 cadence 的模板是一个内存条,所以控制芯片端为金手指接口,选择 J1。

5. 点击下一步,选择内存,这里 U0-U7 都是内存颗粒。

6. 点击下一步选择串联电阻,不用管,下一步,选择 power,这里 VDD/VTT/GND 都勾上,点击下一步

7. 选择 power source VRM,cadence 的内存条已经定义了一个 VRM,Vsource 和 Vterm,等于我们板上的 DCDC,点击右边会出现带有 Editor 含义的 E,点击 E,编辑电压为 1.5 和 0.75,点击下一步

8. 设置 BUS group,设置 A0~A15 为地址信号,命名为 ADDR

9. 设置 CLK

10. 设置 DATA

11. 下一步直到仿真信号预览,检查下是不是对的,点击完成。

12. 在右侧会出现 BUD Tree,设置 Bus tree,右键 J1,点击“connect IBIS”,或者点击左边的“set up controller model”

13. 对 U0 同样操作,定义完 IBIS 后,使用 copy IBIS to

14. 设置完 IBIS 模型后,选择左侧“select Bus groups for simulation”,设置仿真类型为写,等级为 2(考虑耦合因素),速度为 1.333GHz,仿真时间为 40ns

15. 设置仿真激励码型,这里需要用到 Agilent 的码型生成工具,官网有下载,选择 PRBS7 码型

16. 将 PRBS7 码型粘贴到地址仿真码型中,和数据除了 TQS 的码型中,注意后面的两个点不能删除,2 个点代表循环。设置完成,点击下方的 save analysis options

17. 至此,DDR 仿真参数设置完成,file -save as,保存一下,然后点击开始仿真,大约需要 1~3 分钟

18. 查看仿真结果,可以看 CLK/DATA/TQS 等波形,可以看到波形高频分量损耗和反射串扰造成的波形失真,等等很多信息。(感觉仿的不对,但是仿了 5 遍了都是这样)

审核编辑黄宇

-

DDR

+关注

关注

11文章

712浏览量

65416 -

仿真

+关注

关注

50文章

4106浏览量

133774 -

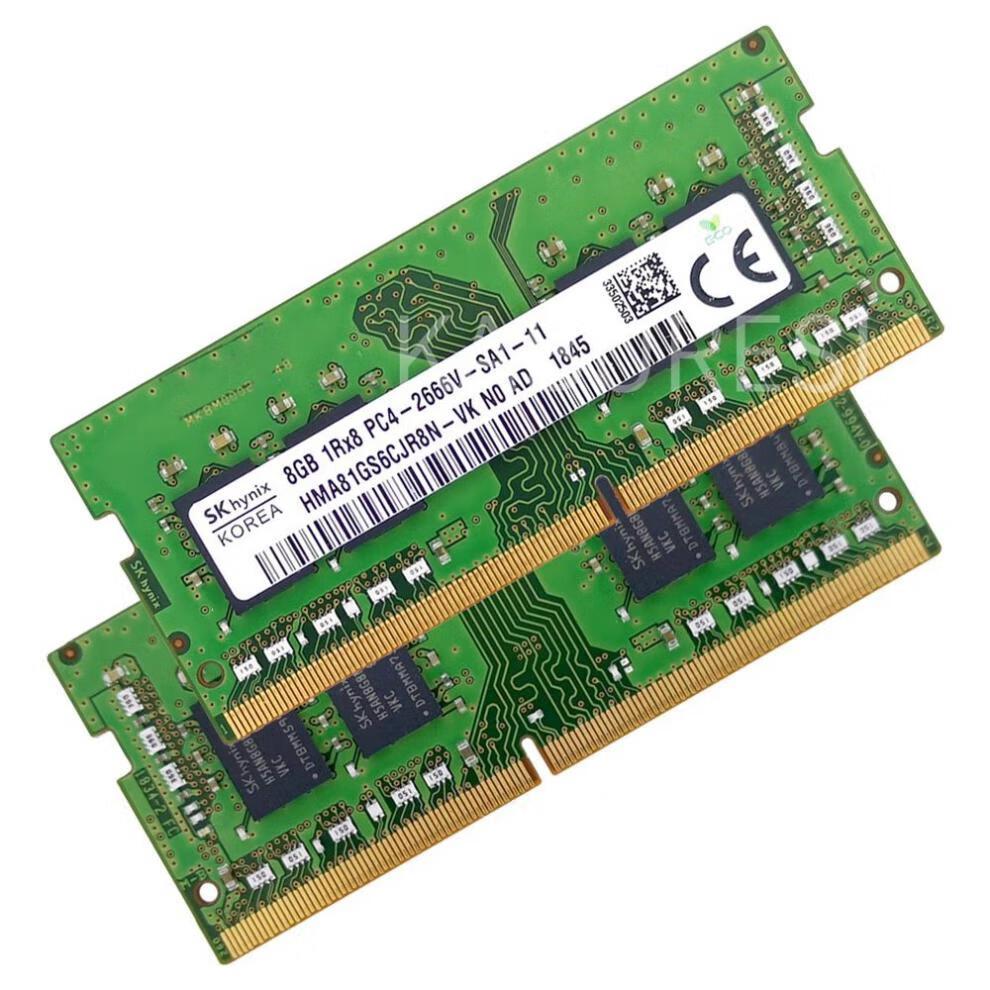

内存条

+关注

关注

0文章

145浏览量

19557

发布评论请先 登录

相关推荐

雷克沙推出全新战神之翼系列DDR5内存条

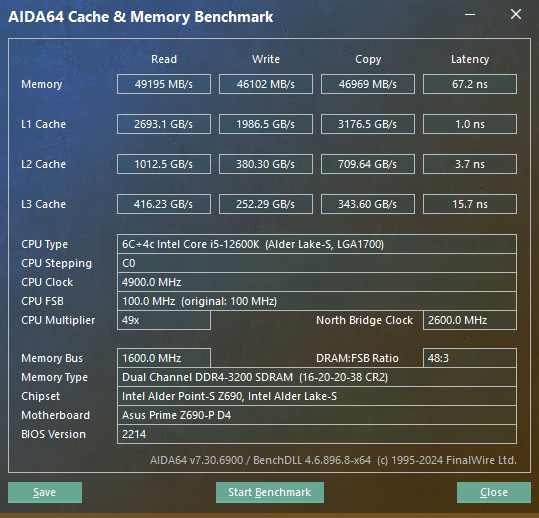

如何检测DDR内存性能

如何选择DDR内存条 DDR3与DDR4内存区别

十铨科技推出首款工业级DDR5 6400MT/s内存条

金士顿发布FURY Renegade DDR5 CUDIMM内存条

金百达、精亿、光威这三个品牌的内存条哪个好?

电脑内存条的作用和功能

内存时钟和内存条有什么不同

内存条接触不良会导致哪些情况

卓越性能精亿内存条赤龙银甲系列DDR4 16G(8GX2) 3200 内存条测评 值得推荐价格亲民质量过硬的国货老牌

DDR5内存条上的时钟走线

研华工控机购买指南:DDR3、DDR4、DDR5怎么选?如何选择内存条?

以DDR内存条为例教你进行SI仿真

以DDR内存条为例教你进行SI仿真

评论