不幸的是,电子设计程序在生成以下内容的Gerber文件之前不会生成警报:轨道错误未完成或轨道丢失的卡。在很多情况下,由于其极其简单,我们在设计PCB时并未将其链接到原理图。如果我们在不采取任何预防措施的情况下选择此程序,则有可能在设计结束时发现一些线索,这些线索可能由于遗忘或由于我们删除了一个组件而将其替换为另一个组件或由于某种原因而中止了绘制轨迹的过程而留下了线索一个没有连接的情况,后来我们从另一层继续跟踪,忘记了程序不会在跟踪开始时自动插入跟踪。

使用以下实用方法,可以检测并纠正一端没有连接到任何东西但其末端与位于另一层的另一条轨道的起点重合的轨道,这导致了一个假设,即它是同一信号并且连接它们的路径丢失了。以同样的方式,我们将能够检测到一条未在任何轨道或垫上结束且在另一层上没有对应关系的轨道,这使我们认为只有该轨道丢失了。在这种情况下,我们肯定会检查卡的整个设计,因为肯定有缺少线索可以完成您的生产线。

说明:

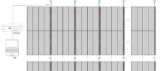

l我们在设计程序中为卡片的TOP,BOTTOM和Pads层选择黑色。

l根据电路的大小,我们以两倍或更大的比例在纸的TOP面(包括焊盘和走线)上打印。

l在电路的底部(包括焊盘和走线)以相同的比例在另一张纸上打印。

l如果我们目视检查,我们可以轻松地检测到没有终止的轨迹,即它们没有连接到另一条轨迹,垫或铜质平面。

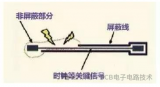

l让我们叠加两个打印件,如果可能,在光源的帮助下,翻阅纸张以确认信号的对应关系。在说明前一个图表的示例中,很明显,该电路的TOP电路中标有红色指示器的点没有连接到指示端的任何一侧。

l动画显示了当重叠两层时,标记为“缺少轨迹”的错误包含的笔画在另一点开始于另一层的同一点处结束,这表明仅缺少连接它们的轨迹。

l我们还观察到,标记为“未完成的磁道”的错误没有相同的对应关系,这表明该磁迹不完整或已遗留,应将其擦除以避免混淆。

注意:

强烈建议再次运行电气设计规则(DRC)分析,以检测由于在卡上插入新元素而产生的错误,并另外再次生成所有Gerber文件。

结论:尽管该程序可以很好地工作,但是建议在设计印刷电路时不从原理图开始,还是花一些时间在我们要连接的焊盘之间绘制电网并保持其各自的层可见,只要有可能,我们就应该花时间设计原理图并在PCB上运行设计规则的实用程序,该程序无疑会根据程序自动生成的网络来检测不完整的连接,并另外使数据层在PCB上可见。尚未如上所述跟踪的连接。

-

印制电路板

+关注

关注

14文章

953浏览量

40741 -

PCB设计

+关注

关注

394文章

4680浏览量

85458 -

PCB打样

+关注

关注

17文章

2968浏览量

21678

发布评论请先 登录

相关推荐

蛇形走线设计在电路板布线中的秘密

探索电路板pcb螺旋走线的特点

光缆配线架怎么走线

如何对PCB进行差分对的走线操作呢?

Altium Designer中走线模式的切换方法

pcb走线的规则设置方法介绍

高速PCB信号走线的九大规则

如何在印制电路设计中检测丢失的走线和不完整的走线?

如何在印制电路设计中检测丢失的走线和不完整的走线?

评论