富士通进一步改进制造工艺,为 ASIC 和 COT 客户提供世界一流的 65 纳米 CMOS 技术。这种极具竞争力的 65 纳米技术具有最大化性能和最小化功耗的选项。因此,该技术既适合以性能为导向的应用程序,也适合结合了卓越性能和长电池寿命的移动应用程序。

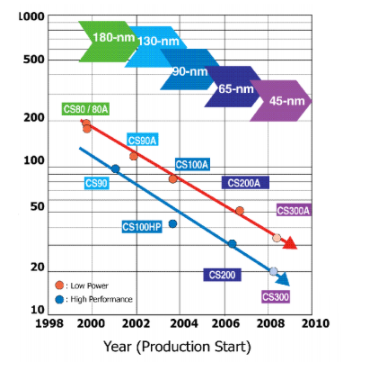

正如公司的技术路线图(图 1)所示,与 90 纳米技术相比,富士通的 65 纳米技术将栅极缩小了 25%。富士通将于 2006 年初开始接受 65 纳米技术的流片验收。

CMOS技术路线图

富士通 65 纳米技术为用户提供了两个系列的选择:

CS200A 用于低功耗/移动使用

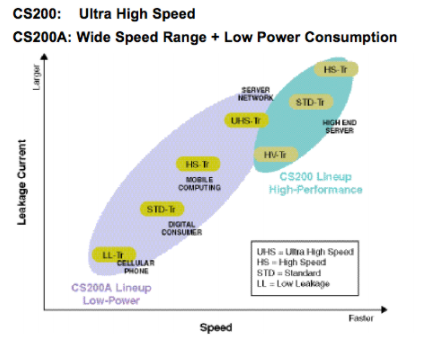

图 2 说明了这两个系列的应用范围。这两个系列都提供了一系列具有不同泄漏功率/性能点的晶体管,使设计人员能够混合晶体管类型以实现高性能和低功耗。CS200A 技术提供了种类繁多的晶体管,从用于手机等应用的低泄漏 (LL) 到用于服务器或网络设备的超高速 (UHS)。

CS200和CS200A晶体管品种

高性能晶体管

CS200 技术的进步包括改进的 CMOS 晶体管配置。具体来说,CS200 晶体管的栅极长度为 30 nm,比 CS100 晶体管的尺寸缩小了 75%。较小的晶体管还使用新的镍多晶硅/多晶硅堆栈,而不是用于 CS100 晶体管的多晶钴/多晶硅堆栈。新材料较低的薄层电阻可确保较低的栅极电阻,从而转化为更高的速度。

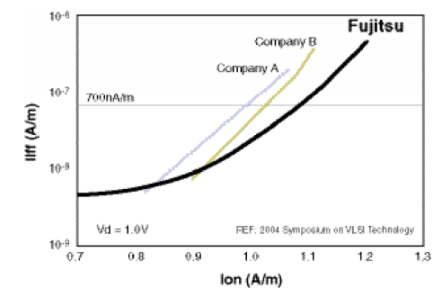

nMOSFET 的 I(on) 和 I(off) 特性

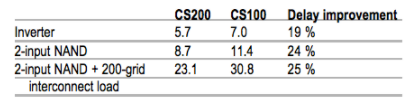

为了说明这种晶体管配置的优势,图 3 显示了 CS200 nMOSFET 的 Ion 和 Ioff 特性以及竞争技术的特性。富士通的 CS200 晶体管在速度和漏电流方面都表现出卓越的特性。一些 CS200 基准电路的 SPICE 仿真显示速度提高了 20% 到 30%,如下表所示。富士通投入了大量精力来实现这些性能改进,以便在公司自己的高性能服务器中使用。

CS200 电路延迟性能(每门 ps)

编辑:hfy

-

cpu

+关注

关注

68文章

10858浏览量

211643 -

服务器

+关注

关注

12文章

9138浏览量

85366 -

晶体管

+关注

关注

77文章

9684浏览量

138118 -

富士通

+关注

关注

2文章

194浏览量

54574

发布评论请先 登录

相关推荐

基于ZU3EG的低功耗高性能嵌入式AI高性能计算模组

统一工艺和架构,赛灵思28纳米FPGA成就高性能和低功耗的完

ADC08B3000低功耗、高性能CMOS模数转换器数据表

ADC083000单通道、低功耗、高性能CMOS模数转换器数据表

ADC081500低功耗、高性能CMOS模数转换器数据表

ADC081000低功耗、高性能CMOS模数转换器数据表

高性能/低功耗65纳米 CMOS技术解析

高性能/低功耗65纳米 CMOS技术解析

评论