本应用笔记介绍了 ZNEO CPU 中的 DMA 控制器及其突出的特性,例如 DMA 和 CPU 带宽共享控制以及四个独立的 DMA 通道。本文档还描述了 DMA 模式,以及它的软件实现和应用程序的测试/演示。

特征

ZNEO CPU 突出的直接内存访问特性是:

- 四个独立的 DMA 通道

- 支持内存到内存、内存到外设、外设到内存以及外设到外设的数据传输。

- 在直接或链表模式下运行

- 字节、字或四元数据传输长度

- DMA 和 CPU 带宽共享控制

- 高达 64K 传输(64 kByte、64 kWord 或 64 kQual)

- 外部 DMA 请求和 DMA 确认信号

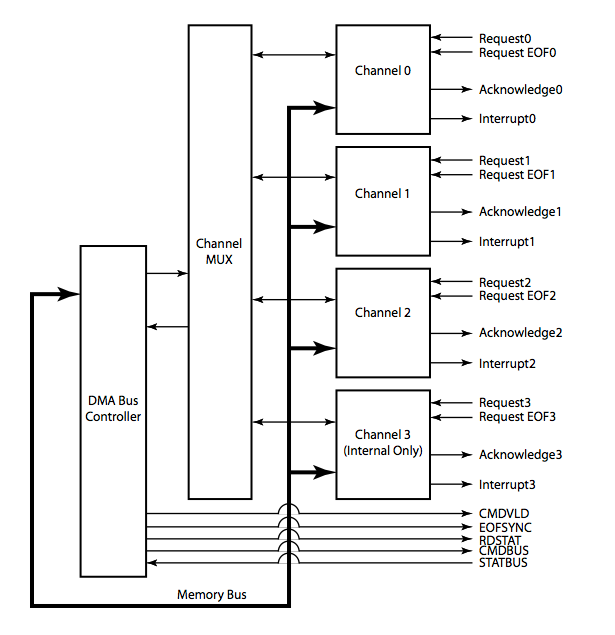

ZNEO DMA 用于减轻处理器执行重复性任务的负担。它将数据从一个内存地址传输到另一个内存地址,或从一个外设传输到另一个外设。这些任务需要由 DMA 控制器生成的读和/或写周期。每个 DMA 传输至少需要 2 个系统时钟周期来执行。图 1 显示了 Z16F MCU 的 DMA 控制器框图,该控制器基于 ZNEO 架构。

图 1 DMA 框图

DMA 模式

直接模式仅使用 DMA 中的寄存器进行操作。软件直接写入这些寄存器以设置和启用 DMA。通过直接设置 DMAxCTL0 寄存器中的相应位进入直接模式。下图显示了 DMA 寄存器以及它们如何指向内存中分配的缓冲区。

链表模式

链表模式需要软件为每个缓冲区分配缓冲区和设置描述符列表。完成此操作后,软件将使用第一个描述符的地址写入 DMAxLAR。然后 DMA 将第一个描述符读入 DMA 控制和地址寄存器,LAR 数据除外。它执行由 DMA 中的描述符数据指定的传输。传输完成后,DMA 读入列表中的下一个描述符并继续执行传输。

软件实施

此参考设计使用 ZNEO Z16F2800100ZCOG 开发套件。它利用 ZNEO CPU 的 DMA 控制器,特别是 DMA 的通道 0,用于演示目的。该应用程序还使用 UART0 提供菜单驱动的控制台,允许用户测试 DMA 控制器的不同操作模式。此外,ADC、Timer2 和 UART1 等外设用于支持 DMA 演示。有关外设初始化的说明,请参见附录 A。

CPU带宽选择

在任何 DMA 初始化之前,确保 CPU 总线设置为分配所需/所需的带宽以供 DMA 使用。如果未设置,将使用重置值;也就是说,每三个 CPU 操作允许 DMA 传输一次。在本应用笔记中,不同的带宽选择用于为 CPUCTL 的不同值提供示例。下表列出了用于每种传输类型的 CPU 带宽。相同的 CPU 带宽将用于直接模式和链表模式。

结果

直接模式在 DMA0CTL 的 IEOB 和 EOF 位设置为 1 且未设置水印值的情况下进行测试。也就是说,只有在当前缓冲区的末尾才会产生中断。链表模式使用与直接模式相同的设置进行测试,DMA0CTL 的 HALT 位设置为 1。

编辑:hfy

-

控制器

+关注

关注

112文章

16320浏览量

177792 -

寄存器

+关注

关注

31文章

5334浏览量

120219 -

cpu

+关注

关注

68文章

10853浏览量

211544

发布评论请先 登录

相关推荐

基于DMA控制器的UART串行通信设计

Crossbar的多通道DMA控制器设计

dma控制器芯片8257资料介绍

基于AXI总线的DMA控制器的设计

dma控制器由什么组成

基于SystemC的可配置多通道DMA控制器的设计

DMA控制器原理详解

ZNEO CPU 上的 DMA 控制器特性分析

ZNEO CPU 上的 DMA 控制器特性分析

评论