本应用笔记介绍了 ARM Cortex-M3 处理器的主要特性,并描述了为其开发软件的不同方面。它还涵盖了现有 ARM 项目到 Cortex-M3 平台的迁移。

Cortex-M3

ARM Cortex-M3 是一种高性能、低成本和低功耗的 32 位 RISC 处理器。Cortex-M3 处理器只执行 Thumb-2 指令。它不支持 ARM 指令集。Cortex-M3 处理器基于 ARM 架构 v7-M,拥有高效的哈佛 3 级流水线内核。它还具有硬件划分和低延迟中断服务程序 (ISR) 进入和退出。

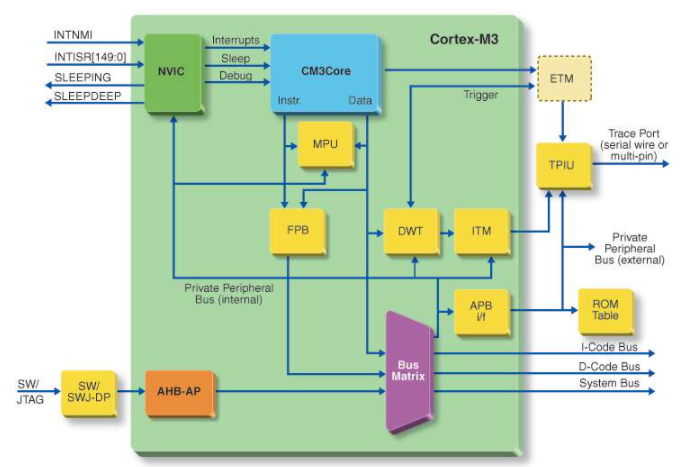

除了 CPU 内核外,Cortex-M3 处理器还包括许多其他组件。其中包括嵌套向量中断控制器 (NVIC)、可选的内存保护单元 (MPU)、定时器、调试访问端口 (DAP) 和可选的嵌入式跟踪宏单元 (ETM)。Cortex-M3 也有一个固定的内存映射。

嵌套向量中断控制器 (NVIC)

根据芯片制造商使用的实现方式,NVIC 可以支持多达 240 个外部中断,具有多达 256 个不同的优先级,可以动态重新确定优先级。它同时支持电平和脉冲中断源。处理器状态在中断进入时由硬件自动保存,并在中断退出时恢复。NVIC 还支持中断的尾链。

在 Cortex-M3 中使用 NVIC 意味着 Cortex-M3 的向量表与以前的 ARM 内核非常不同。Cortex-M3 向量表包含异常处理程序和 ISR 的地址,而不是像大多数其他 ARM 内核那样包含指令。初始堆栈指针和复位处理程序的地址必须分别位于 0x0 和 0x4。这些值然后在复位时加载到适当的 CPU 寄存器中。

内存保护单元 (MPU)

MPU 是 Cortex-M3 的可选组件。如果包含在内,它会通过强制执行特权和访问规则来支持保护内存区域。它最多支持八个不同的区域,每个区域可以再分成八个相同大小的子区域。

调试访问端口 (DAP)

DAP 使用 AHB-AP 接口与处理器和其他外设进行通信。调试端口有两种不同的支持实现,串行线 JTAG 调试端口 (SWJ-DP) 和串行线调试端口 (SW-DP)。您的 Cortex-M3 实现可能包含其中之一,具体取决于您的芯片制造商使用的实现。

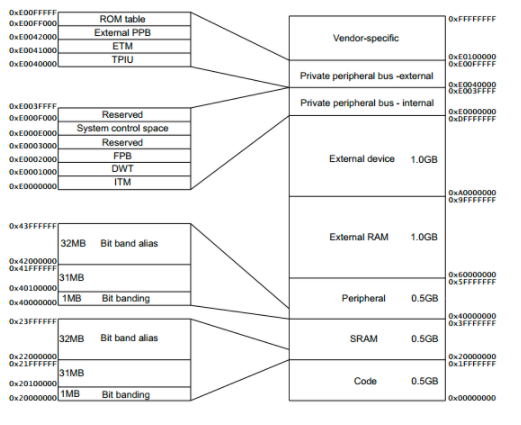

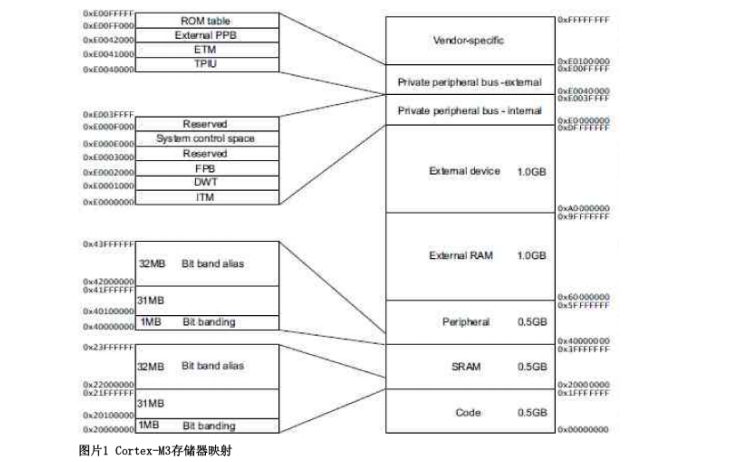

内存映射

与大多数以前的 ARM 内核不同,基于 Cortex-M3 的设备的内存映射的整体布局是固定的。这允许在基于 Cortex-M3 的不同系统之间轻松移植软件。地址空间被分成许多不同的部分。这在下面的图 2 中显示。

编辑:hfy

-

cpu

+关注

关注

68文章

10929浏览量

213452 -

定时器

+关注

关注

23文章

3257浏览量

115625 -

中断控制器

+关注

关注

0文章

59浏览量

9502

发布评论请先 登录

相关推荐

Cortex-M3处理器是什么

STM32 的核心Cortex-M3 处理器是什么

ARM Cortex-M3定义指南

STM32系列ARM Cortex-M3微控制器原理与实践

Cortex-M3 技术参考手册

选择ARM处理器,ARM7还是Cortex-M3

Cortex-M3内核的ARM处理器的应用资料说明

Cortex-M3处理器内核与基于Cortex-M3的MCU关系

STM32 的核心Cortex-M3 处理器

ARM Cortex-M3 处理器的主要特性分析

ARM Cortex-M3 处理器的主要特性分析

评论