一般而言,悬空或未使用的 CMOS 输入的问题是它们不能悬空,否则由于栅极输入电容的逐渐充电,它们可能会导致以下情况:

可能有静态电流流过输入级,导致不必要的过度功耗。

当输入电压达到阈值水平时,器件可能会开始高频振荡,从而产生热量,最终可能损坏器件。

因此,作为标准解决方案,所有未使用的(开路或浮动)输入都简单地连接到 GND 或 VCC 以防止这些不利影响。

解决方案

以下是几种解决方案,包括其增加的成本、组件数量和有效性:

1. 静态上拉/下拉电阻

当总线不受任何设备驱动时,静态上拉/下拉电阻是一种经常使用的解决方案,用于定义未使用的 CMOS 输入的状态。尽管这些电阻会导致额外的功耗并增加组件数量,但它们非常有效。但是,当使用当今的 TSSOP48-56 等窄间距封装时,甚至可能没有足够的空间在 PCB 上添加这些上拉/下拉电阻。

2. 外部总线保持电路

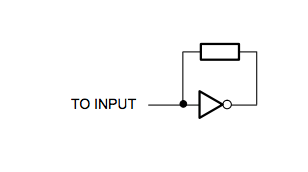

外部总线保持电路(见图 1)是另一种在其输入和输出之间使用反相器和电阻器的解决方案。该电路根据输入的状态将输入连接到 GND 或 VCC,并将总线保持在这种状态,因此它的名称为“总线保持”。虽然该电路减少了前面描述的静态上拉/下拉电阻引起的过度功耗,但它显着增加了元件数量和成本。

图 1 外部总线保持电路

3. 集成总线保持电路

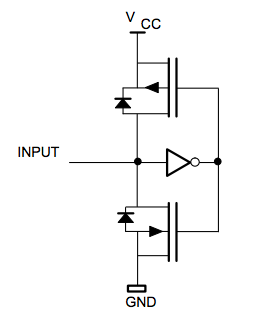

飞利浦半导体已将集成总线保持电路(见图 2)应用于多个逻辑系列。集成总线保持电路最大限度地减少了额外的功耗,并在内部提供额外的组件数量,而无需为设备增加额外成本。

图 2 集成总线保持电路

集成总线保持电路的作用类似于动态上拉/下拉电阻,如下所示:

当输入为“0”时,反相器的输出为“1”,因此较低的 FET 导通并起到下拉电阻的作用。

类似地,当输入为“1”时,上部 FET 被激活并起到上拉电阻的作用。

编辑:hfy

-

CMOS

+关注

关注

58文章

5724浏览量

235675 -

pcb

+关注

关注

4320文章

23117浏览量

398417

发布评论请先 登录

相关推荐

TTL电路中的常见问题及解决方案

解决方案 | 基于TSMaster的平板电脑解决方案

智慧园区系统集成解决方案应用

BCM中的开关检测:集成MSDI解决方案与半分立解决方案

Cadence 助力 MaxLinear 将模拟和数字设计集成到同一颗芯片中,持续保持连接解决方案领域领先地位

医院集成平台解决方案

专用集成电路 通用集成电路有哪些特点 专用集成电路 通用集成电路区别在哪

基于VPLC711的曲面外观检测XYR运动控制解决方案

采用小型封装的高度集成电路保护和电源管理解决方案TPS2597xx数据表

释放总线潜力:汽车总线离线模拟解决方案

集成总线保持电路的解决方案

集成总线保持电路的解决方案

评论