本应用报告介绍了实现 IDT 基于 PLL 的零延迟缓冲器的输入参考时钟和输出时钟之间定义的相位关系的不同方法。该报告重点介绍了 PLL 反馈环路中不同走线长度和反馈时钟输入端的电容负载对生成早期(或晚期)时钟的影响。早期时钟定义为输出时钟的相位相对于参考输入时钟提前的情况。

简介

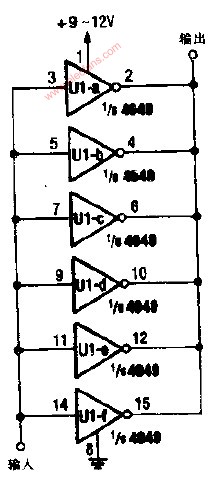

时钟驱动器架构有两种主要类型:缓冲器型和带锁相环 (PLL) 的反馈型。在缓冲器型(非 PLL)时钟驱动器中,输入波通过器件传播并由输出缓冲器“重新驱动”。输出信号直接跟随输入信号,并带有一些器件传播时间延迟 (tPD)。

反馈型时钟驱动器利用来自设备时钟输出之一的附加反馈输入路径。反馈路径可以在设备内部或外部。对于外部反馈,PCB 上的走线用于将输出引脚连接到反馈输入引脚。这种类型的设备通常基于一个或多个 PLL,这些 PLL 用于对齐反馈和参考输入的相位和频率。可以补偿板级走线长度不匹配,以实现输入和输出时钟之间定义的偏移关系。输出可以有选择地进行分频、相乘或反相,同时仍然保持非常低的输入到输出偏差。

什么是锁相环?

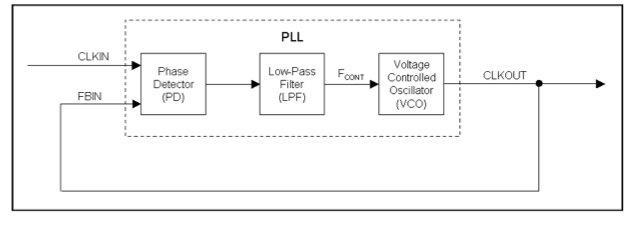

基本的 PLL 是一种反馈系统,它接收输入的振荡信号并生成以输入信号的整数倍或分数倍数振荡的输出波形。它由相位或频率检测器、滤波器和压控振荡器组成,如图 1 所示。为了使 PLL 将参考输入 (CLKIN) 与输出对齐,必须将输出反馈到反馈(FBIN) PLL 的输入。

锁相环 (PLL) 框图

相位检测器 (PD) 通常评估 CLKIN 输入相对于 FBIN 输入的上升沿。如果 CLKIN 输入超前 FBIN 输入,表明压控振荡器 (VCO) 的运行速度比理想情况要慢,则 PD 会产生一个在 CLKIN 输入的上升沿触发并持续到上升沿的“Pump Up”信号FBIN 输入。这个“上泵”脉冲迫使 VCO 运行得更快,并减少了 CLKIN 输入和 FBIN 输入之间的时间差。

如果 FBIN 输入超前于 CLKIN 输入,则 PD 会产生一个“抽空”信号,该信号在 FBIN 输入的上升沿触发并持续到 CLKIN 输入的上升沿。“Pump Down”脉冲强制 VCO 运行得更慢,并减少 FBIN 输入和 CLKIN 输入之间的时间差。

编辑“hfy”

-

锁相环

+关注

关注

35文章

590浏览量

88050 -

滤波器

+关注

关注

161文章

7919浏览量

179506 -

缓冲器

+关注

关注

6文章

2000浏览量

45859 -

pll

+关注

关注

6文章

785浏览量

135467 -

时钟驱动器

+关注

关注

0文章

50浏览量

13913

发布评论请先 登录

相关推荐

零延时缓冲器

如何在ISE中延迟缓冲区?

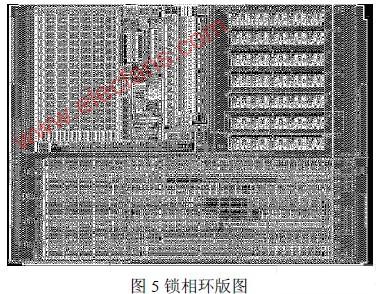

用于零延迟缓冲器的PLL设计

Cypress高性能零延迟缓冲器面向高速通信和消费设备

缓冲器,缓冲器是什么?

缓冲器,缓冲器基本原理是什么?

基于CSMC工艺的零延时缓冲器的PLL设计

使用IDT时钟缓冲器提升应用设计

什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析

如何在TDMoP产品上使用抖动缓冲器来补偿数据包延迟变化

基于 PLL 的零延迟缓冲器的系统应用

基于 PLL 的零延迟缓冲器的系统应用

评论