正在浏览一些旧笔记,偶然发现了我了解死时间的那一天。不,这不是我们都试图忽视的致命时刻;在此期间,在半桥或全桥中打开和关闭 FET 至关重要。那么它是什么,为什么 FET 的开关如此重要?当数字电路遇到模拟电路时,获得您想要的结果总会带来一些乐趣,半桥和全桥也不例外。尽管我将研究这些特定的电路,但可以公平地说,相同的想法也可用于开关任何设备,例如打开和关闭 FET,具有准确的时序和控制。

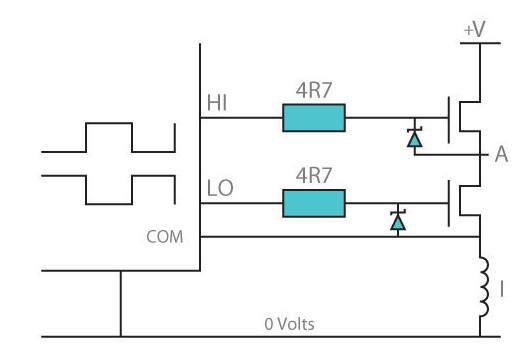

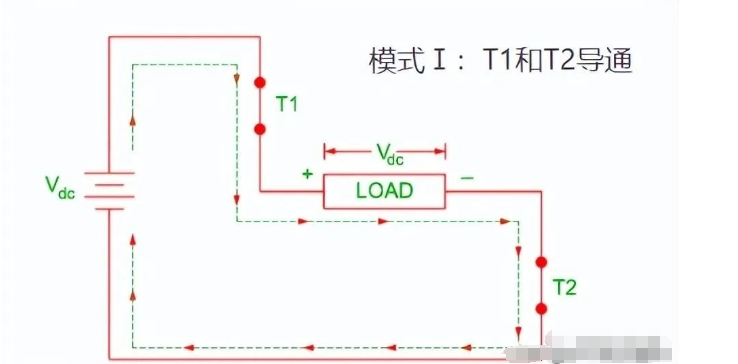

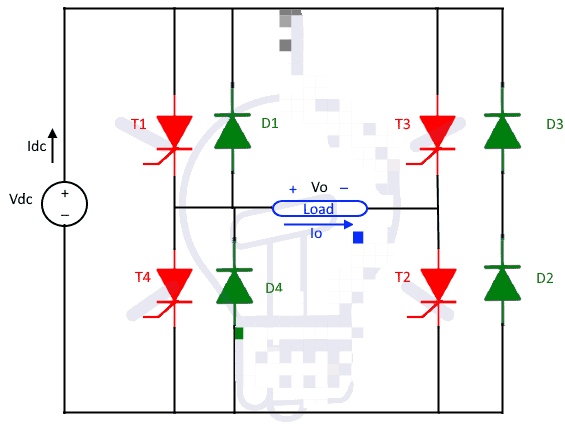

下面我列出了桥梁一侧的基础知识,但删除了一些组件,以便我们可以单独查看主要功能。

驱动IC电路

该电路的工作原理是在操作阶段从 HI 和 LO 输出生成方波。这在理论上意味着一次只有一个设备处于开启状态,并且“A”点将在 0 伏和 + V 之间变化。您会看到有两个电阻连接到 FET 的栅极。这些由数据表根据需要指定。它们限制在驱动器 IC 和 FET 栅极之间流动的电流。这些器件中的栅极包含一个小电容器,它只是 FET 功能的一部分。因此,当栅极电压 (Vgs) 在 0 到 15 伏之间摆动时,该电容器需要充电。然后它需要在栅极恢复到 0 伏时放电。驱动器 IC 可以切换相当高的瞬时电流,但电阻器可以限制这一点。我还添加了齐纳二极管,这是一种很好的做法,因为这可以防止栅极电压超过开关电平(在这种情况下为 15 伏)或产生低于 -0.5 的负电压。最后,我添加了一个电感器 (I),它不是真正适合的设备,而是代表底部 FET 和驱动器 IC 的 0 伏参考之间的 PCB 电感(在本例中,驱动器侧单独连接到底部FET,但并不总是在这种类型的 IC 中可用)。

因此,如果在“A”处没有任何连接,我们应该看到的只是电压的过渡,而没有电流从顶部流向底部。但是,我们有两个 RC 电路,由 FET 中的电容器和影响 FET 栅极的串联电阻器组成。我们看到的是一个设备慢慢打开,而另一个设备慢慢关闭。在中间点,FET 都部分导通,电流将流动。在我当时测试的电路中,桥上有 400Vdc,通过 FET 获得 30 安培的电流持续大约 1nS——不好。这会导致更多的问题,而不仅仅是大电流浪涌和 EMC。PCB 中的大电流和我的隐形电感导致底部 FET 的源极出现电压。这提升了 COM 连接,并且在该设备中具有开始再次关闭 FET 的效果(Vgs 降低)。

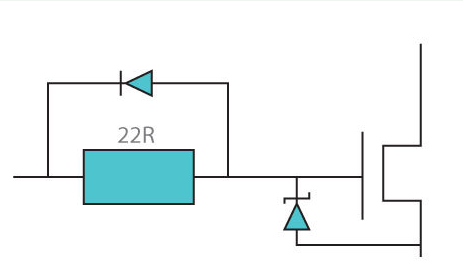

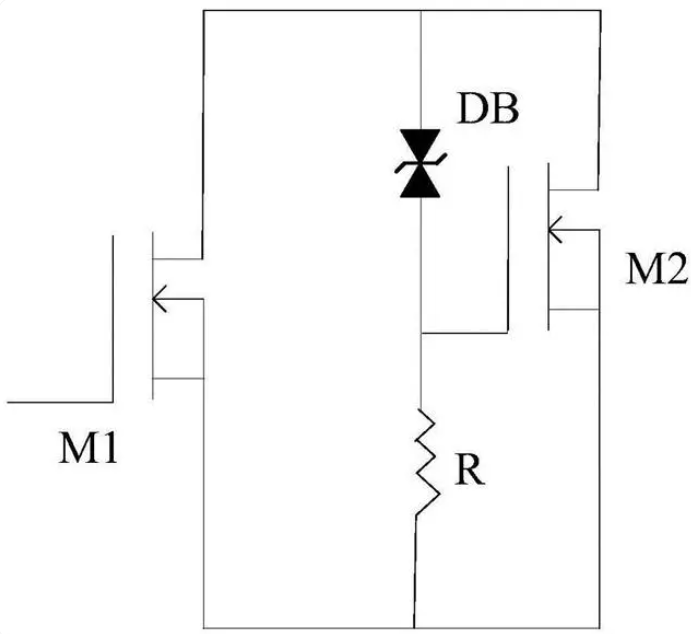

新型 FET 栅极电路

解决此问题的旧方法是在设备都关闭时产生一些死区时间,以防止大电流浪涌。这是通过改变为 FET 供电的电路来完成的。首先,我们希望在接通 FET 时通过增加电阻来减慢 FET 的充电速度 - 在这种情况下,从 4R7 到 22R。然后为了获得真正快速的关断时间,我使用了一个旁路二极管,允许驱动器 IC 快速将 FET 的栅极接地。在某些情况下,如果栅极电流很大,您可能仍然需要一个小电阻,例如 1R 与该二极管串联,但通常仅二极管就可以完成这项工作。在我的电路中,这将分频器的电流降低到 1 安培以下,当时是可以接受的。

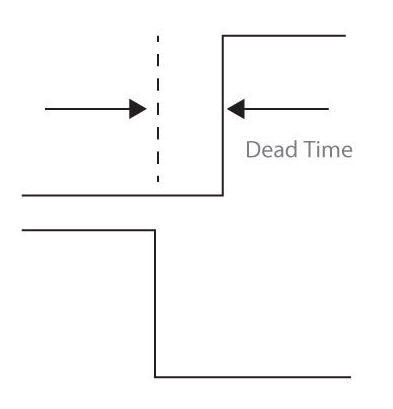

死的时间

正如我所说,这段时间称为“死区时间”,可以减少这种电路中发生的短路效应。然而,时代已经发展,死区时间控制现在已内置到驱动器 IC 甚至微控制器中。在上面的电路中,如果 HI 和 LO 信号在转换之间有一个短暂的停顿,则不难看出,允许控制门的时序和 FET 的开关。死区时间不是对称的,这可以在现代死区时间控制设备中看到。上面的电路在从高到低和从低到高时会有不同的电流浪涌。因此,新设备使用可以单独配置的前置和后置定时器。您可以在下面看到来自 Microchip 控制器的典型时序安排。

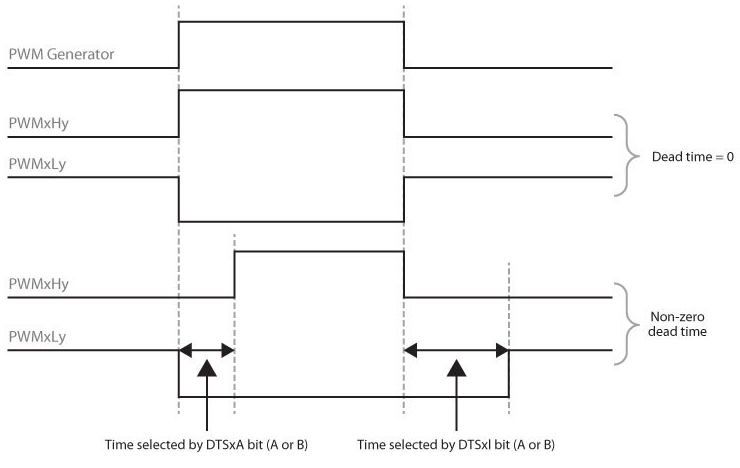

前后计时

在这里很容易看到为死区时间控制电路供电的原始信号(PWM 发生器)。将时间设置为零,高端和低端一起切换。然后调整这些前后时间允许不对称的死区时间。

这允许更有效的控制,并允许您减少电路设计中的损耗。您还可以减少可能影响 EMC 结果的噪音。死区时间和控制 FET 栅极开关可以进行重大改进,现代设备允许越来越好的控制。

编辑:hfy

-

电容器

+关注

关注

64文章

6222浏览量

99632 -

电阻器

+关注

关注

21文章

3782浏览量

62134 -

驱动IC

+关注

关注

9文章

303浏览量

33817 -

PWM发生器

+关注

关注

0文章

14浏览量

8858

发布评论请先 登录

相关推荐

想做一个D类放大器,如何做到不用内部的半桥电路,而使用外部搭载的半桥电路?死区时间如何控制?

使用半桥 DRV89xx-Q1 作为高侧或低侧开关应用说明

半桥驱动器和全桥驱动器的差异

半桥电路与全桥电路的区别

具有可编程死区时间的100-V半桥门驱动器LM5105数据表

浅谈半桥或全桥中的开关 FET 和死区时间

浅谈半桥或全桥中的开关 FET 和死区时间

评论