本应用笔记介绍了 ISLA11xP50 模数转换器 (ADC)。本文的目的是提供有关 ISLA11xP50 输出数据定时和同步程序的基本信息。

使用当前的 FPGA 技术可以轻松地从 ISLA11xP50 ADC 捕获数据。源同步 LVDS 接口以 250MHz 时钟提供高达 500MHz 的 DDR 输出数据。时钟和数据在 ±250ps 内对齐,在 500MSPS 运行时在整个工艺、电压和温度范围内提供 1.5ns 的宽保证数据有效区域。

在内部,输入时钟立即被二分频,以便以输出采样率的一半为两个 ADC 内核提供时钟。即使 500MSPS 输出数据流由两个交错式 ADC 内核生成,输出数据也始终以已知顺序从单个 ISLA11xP50 传送。由于二分频的不确定输出相位,具有对齐输入时钟边沿的多个 ADC 可能没有对齐的输出时钟边沿。CLKOUTP 信号可以在输入时钟的上升沿为高电平或低电平,除非特别强制为已知状态。

ISLA11xP50 包括同步功能,可以更轻松地设计需要同步采样或进一步交错采样的系统。同步可能就像使用单个 ADC 输出数据时钟或 CLKDIVRST 引脚来强制同步一样简单。更复杂的方法可以使用 PHASE_SLIP 寄存器来调整时序。最佳方法取决于许多因素,包括时序余量、FPGA 系列、FPGA 设计工具和印刷电路板 (PCB) 限制。在 500MSPS 操作时,CLKDIVRSTP 建立和保持时序对于某些设计可能具有挑战性。通过门控 ADC 输入时钟以提供额外的裕量,可以有效地放宽这些时序要求。

输出时序

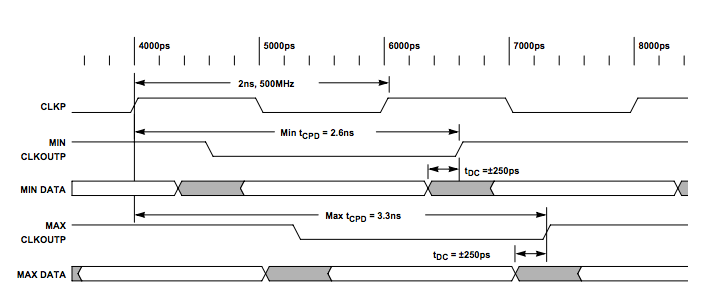

ISLA11xP50 输入时钟和数据通过 ISLA11xP50 以类似的延迟路径传播,以放宽数据捕获时序要求。ADC 输出 DATA 将在 CLKOUTP 信号的 ±250ps 内从一个样本转换到下一个样本;在 500MSPS 时留下 1.5ns 的宽数据有效窗口。CLKOUTP 将在 1.8V 和 +25°C 时从 CLKP 延迟 2.6ns 至 3.3ns,如图 1 所示,或在从 -40°C 至 1.7V 至 1.9V 的整个推荐工作范围内延迟 2.0ns 至 3.6ns +85°C。

内部运作

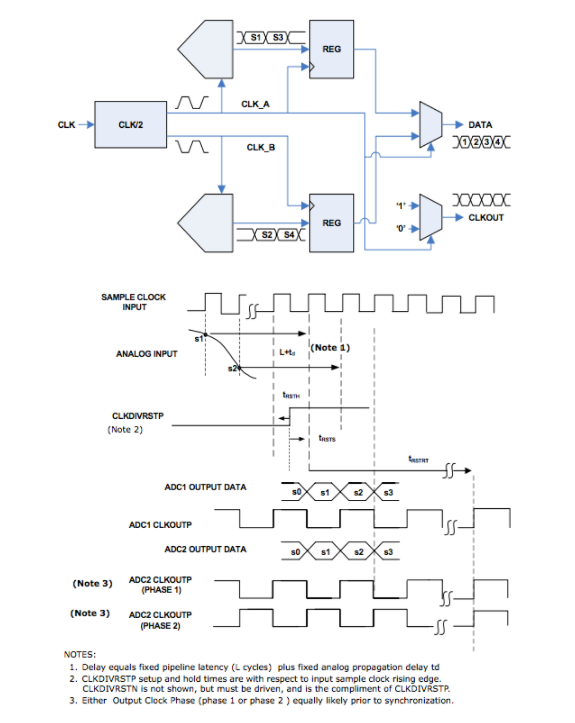

ISLA11xP50 的交错操作需要将 500MHz 输入时钟除以 2,以便每个内核以 250MSPS 进行采样。图 2 显示了 ADC 内部时钟电路的概念图。时钟分频器通常在随机状态下从上电复位中出来,因此输出时钟相位(图 2 中的 CLK_A、CLK_B)是不确定的。在使用单个 ADC 的正常操作中,未知时钟相位无关紧要,输出采样顺序始终正确。同步多个 ADC 时可能不是这种情况。CLKOUTP 相位的不确定性意味着 CLKOUTP 上升沿可能不会跨由同一时钟源驱动的多个 ADC 对齐。如图 3 所示,这种可能的相位差会导致所捕获数据的采样时间和序列出现意外差异。

同步

ISLA11xP50 提供两种机制来控制输出时钟相位:

CLKDIVRSTP 引脚提供了同步多个 ADC 的最简单方法。当 CLKDIVRSTP 在数据表设置和保持时间内设置为高电平时,CLKOUTP 信号将始终被强制为已知相位。将 CLKP 和 CLKDIVRSTP 路由到具有相同 PCB 延迟的多个 ADC 允许所有 ADC 同时设置为相同的采样相位。断言 CLKDIVRSTP 可能会导致内部 DLL 失去锁定长达 52µs。在此 52µs 周期后,可能会捕获有效数据。此过程必须在每次电源循环或 ADC 复位后完成。

可以写入 PHASE_SLIP 寄存器 (0x71) 以有效地反转 CLKOUTP 信号。用户测试模式允许输出一对已知值,但使用这些值来识别时钟相位关系比使用 CLKDIVRSTP 需要更多的 FPGA 代码。与 CLKDIVRSTP 同步后,PHASE_SLIP 寄存器可用于延迟输出数据以进一步交错多个 ADC。

如果 CLKDIVRSTP 需要宽松的建立和保持时间,则可以关闭输入时钟,将 CLKDIVRSTP 设置为高电平,然后重新启用时钟。必须使用无毛刺时钟门控电路以确保可靠运行。

编辑:hfy

-

FPGA

+关注

关注

1638文章

21861浏览量

610091 -

adc

+关注

关注

99文章

6591浏览量

547248 -

模数转换器

+关注

关注

26文章

3253浏览量

127525

发布评论请先 登录

相关推荐

hyper 安装xp,hyper-v为什么要安装xp?

请问多个ADS1262的数据输出如何同步?

XP4302 5V输入单节锂电池同步降压2A充电管理芯片数据手册

XP4302 5V输入单节锂电池同步降压2A充电管理芯片

DRA75xP、DRA74xP信息娱乐应用处理器芯片版本1.0数据表

DRA77xP、DRA76xP信息娱乐应用处理器芯片版本1.0数据表

低电压、5位、自定时、单线输出扩展器TCA5405数据表

用于低输出电压的N沟道FET同步降压控制器LM2742数据表

3-A输出跟踪/端接同步PWM切换器TPS54372数据表

4.5伏至20伏输入,6伏输出同步PWM TPS54550数据表

ISLA11xP50 输出数据定时和同步程序浅析

ISLA11xP50 输出数据定时和同步程序浅析

评论