本白皮书介绍了有关抽取和插值滤波器的新观点。它提供了有关这些滤波器的简要介绍和历史观点,以及信号等待时间的可听性,IIR滤波器的适用性和相位失真的可听性。

引言和历史观点

早期的数字音频转换系统需要非常高级的模拟滤波器,以在A / D转换中提供抗混叠滤波,并在D / A转换过程中提供重构滤波。这些高阶模拟滤波器的一个特征是音频频带内有大量的相移。这些滤波器不仅制造困难,而且过多的相移被认为是与早期数字音频系统相关的不良音质的主要来源。模拟反图像滤镜可去除剩余的图像。对A / D转换也执行了类似的过程,其中模拟抗混叠滤波器被低阶模拟滤波器的组合所代替,对输入信号进行过采样,并使用数字抽取将采样率降低至适当的基频。带率。部分由于与较高阶高阶模拟滤波器的相位响应相关的可听性问题,这些数字内插和抽取滤波器是通过线性相位有限冲激响应(FIR)滤波器实现的。在带内相位响应方面,钟摆从一种极端转向另一种极端,用于转换过程的线性相位FIR滤波器成为“圣地”,并在25年后继续成为行业标准。

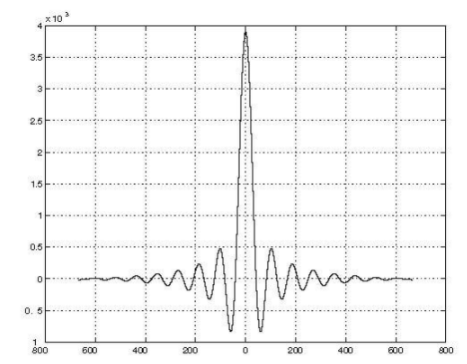

48 kHz采样率下的脉冲响应(X轴,以微秒为单位)

信号延迟或时间延迟的可听性

数字音频系统会引入时间延迟。这种延迟不仅是由于抽取和内插滤波器引起的,而且还由于传输链路和数字信号处理的结果。在大多数应用中,这种延迟是听不到的。但是,延迟是现场声音应用程序中公认的问题。考虑一下表演者通过耳机或扬声器反馈实况混音的情况。如果监听器信号链中有足够的延迟以产生回声的感觉,那么对于艺术家而言,要继续表演是非常困难的,即使不是不可能的。有记录的这种效果,并且很可能大多数人在电话连接不良的情况下都遇到了这种现象。

后退到角落

看来我们已经退缩了。平坦的频率响应和最小的预回声的矛盾要求给A / D和D / A转换器IC的设计人员带来了一系列有趣的挑战,尤其是在44.1和48 kHz时。尽管FIR滤波器被认为是“行业标准”,但它们在计算上效率低下,并且在遇到严峻的经济现实时通常需要权衡设计。“尽管有许多巧妙的方案可以提高计算效率,但在所需响应和抽头数量之间达成折衷并不罕见。折衷方案是在衰减,平坦响应,通带(和衰减区域)中的纹波,过渡带等之间进行权衡。”正确解决这些问题的FIR成本不仅存在问题,而且滤波器还需要额外的抽头,转化为增加的时间延迟。本质上,平坦的频率响应,不存在预回声和亚毫秒级延迟的理想属性与FIR滤波器互斥。

IIR滤波器的适用性

解决这些问题的一种方法是过渡到无限冲激响应(IIR)滤波器。IIR滤波器的计算效率更高,与FIR滤波器相比,它具有更大的处理灵活性。这种效率包括最大程度地降低(如果不能消除)预回波并保持所有采样率的平坦频率相位响应的灵活性。IIR滤波器的另一个好处是极大地改善了延迟特性。具有与FIR相当的频率响应的IIR延迟规范在5到10个采样周期的范围内,或比FIR少75%。

相位失真的可听性

关于阶段的可听性的一个令人困惑的问题是,当实际上应该将讨论作为两种不同的情况时,通常将讨论视为单个主题。相位失真的可听度必须按以下方式进行评估:

通道间相位失真。表征为两个或多个通道之间的相位响应差异

通道内相位失真。通过通道内的非线性相位响应来表征,规定系统内所有通道之间的相位响应均匹配(即通道间失真等于0毫秒)

通道间相位失真

我们使用耳朵接收到的声音之间的幅度和相位关系来定位声音的来源。现代音频系统使用此属性来创建所谓的影像,或更能感知乐器或人声来自与实际扬声器位置不同的位置。通过简单地颠倒原本正确配置的立体声系统的一个声道上的扬声器连接,就可以轻松证明声道间相位失真的可听见效果。成像丢失立即引起注意,即使对于那些不表示标准操作的患者也是如此,但这并没有显示出潜在的影响。测试的结果是,您很难找到有人认为180度的通道间相位失真是可以接受的。

编辑:hfy

-

滤波器

+关注

关注

161文章

7859浏览量

178847 -

扬声器

+关注

关注

29文章

1318浏览量

63215 -

监听器

+关注

关注

0文章

12浏览量

14504 -

IIR滤波器

+关注

关注

0文章

33浏览量

11565

发布评论请先 登录

相关推荐

求助,AD7190关于Σ-Δ ADC其中的抽取滤波器的数据转换问题求解

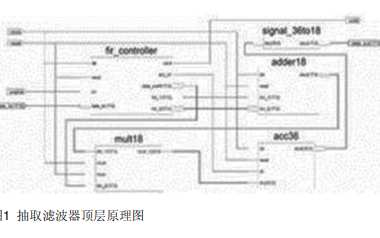

分享:刚完成的FPGA插值滤波器设计

CIC抽取滤波器MATLAB仿真和FPGA实现

基于多核DSP处理器的插值和抽取滤波器的设计

CIC滤波器的优化设计及FPGA实现

高频数字抽取滤波器的设计

FPGA的FIR抽取滤波器设计详细教程

FPGA的FIR抽取滤波器设计教程

关于高频数字抽取滤波器的设计

如何使用FPGA实现FIR抽取滤波器的设计

关于抽取和插值滤波器的介绍

关于抽取和插值滤波器的介绍

评论