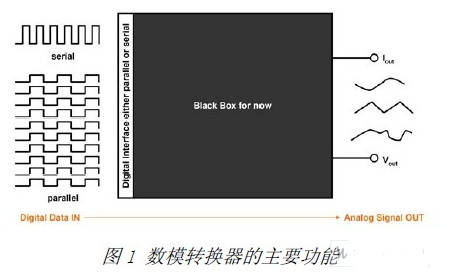

将PWM与较小的R-2R梯形图结合使用可同时改善两者。它显着降低了PWM纹波,并提高了DAC的分辨率。

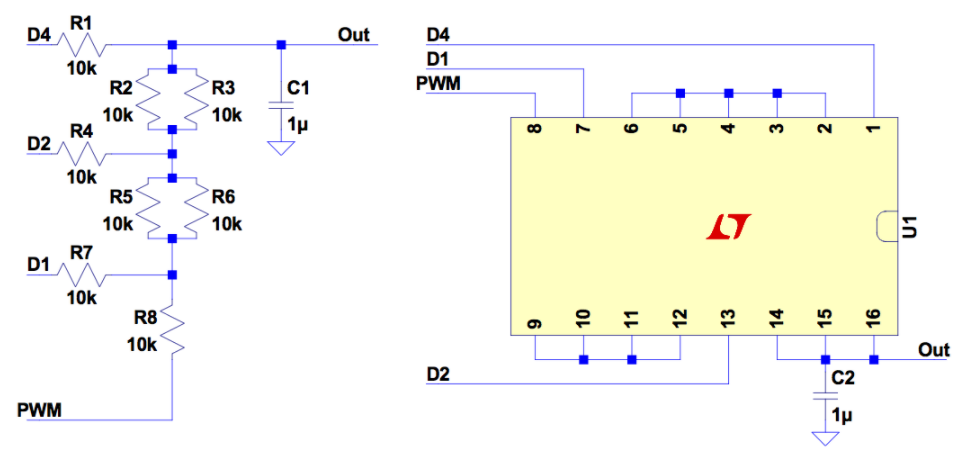

在本设计思想中,一个八电阻阵列和三个输出引脚构成了一个改进的R-2R梯形图(图1)。修改是将底部2R连接到PWM输出而不是接地。

图1 混合PWM / R-2R DAC

梯形图将VCC分为八个切片,PWM填充了从每个级别(0%PWM)到下一个更高级别(100%PWM)的空间。这样可以将纹波减小到八分之一,同时增加了三个额外的高阶分辨率。或者,您可以从原始PWM占空比值的顶部开始获取这三个位,将其时钟速率乘以八。您仍然可以获得8:1的纹波降低,但是增加的时钟速率会将PWM噪声进一步推入滤波器的低地,以实现更大的衰减。

我已经模拟了这种混合方法。

图2 比较/仿真电路

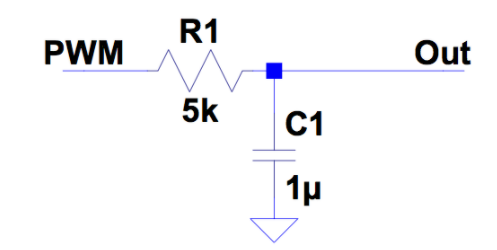

与传统的简单低通滤波器(图2)相比,您应该记住

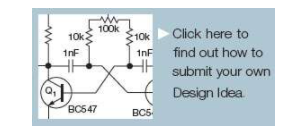

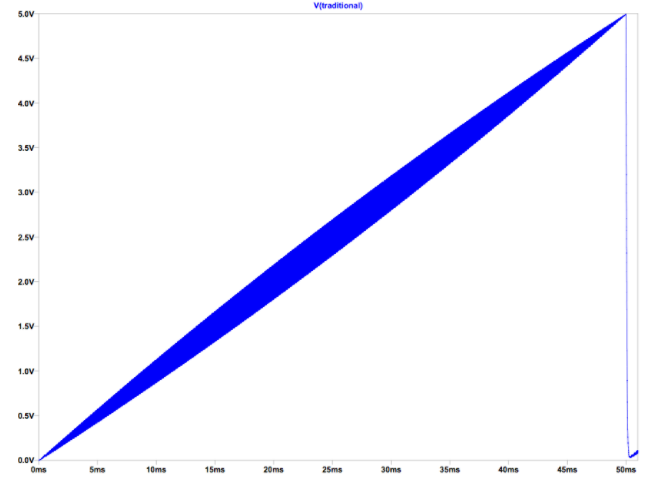

R-2R梯形的输出电阻为R,并且由于我建议将阵列中的两个电阻并联以形成R(对于2R使用单独的电阻),因此10kΩ的阵列会产生5kΩ的输出电阻。这就是我在传统方法中使用的,同时使用了相同的1µF电容器。我将PWM设置为50%的占空比,因为这是最严重的纹波发生的地方。仿真结果(图3)显示了传统方法,纹波约为4mV,而第一种选择(将三个新位添加到原来的八个中)产生了493µV纹波,大约只有八分之一。第二种选择(将PWM时钟增加8,剩下总共8位)仅产生61µV,约为原始值的六十分之一。

图3 仿真结果

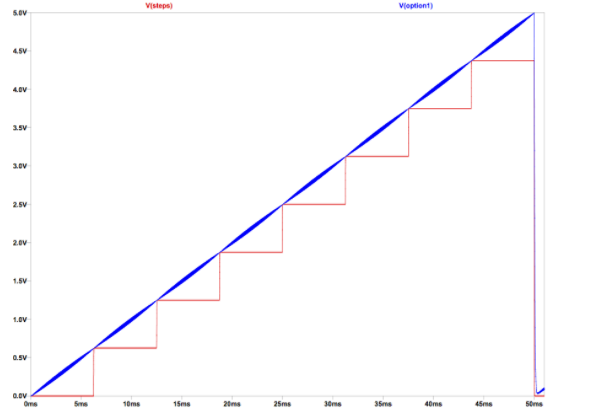

图4a(PWM +低通)和4b(11位混合)是复杂模拟的结果,该模拟将电压从0V缓慢地提高到5V。滤波器中的电容器故意过小,因此我们可以看到此规模的纹波。普通的R-2R梯形图会添加一个阶梯图(4b中的红色),以显示PWM如何从一个电平移动到下一个电平,甚至超出R-2R梯形的顶部直至达到5V。

图4 模拟的基本PWM DAC(fig4a,顶部)和混合DAC(fig4b,底部)的纹波。

这也可以用NCO(数字控制振荡器)技术代替PWM。NCO(向累加器添加一个值并输出进位)相对于PWM具有优势,因为它可以减少50%设置附近的纹波(通过增加转换频率),这是简单PWM最差的地方。

而且这也可以与其他任何DAC一起使用:只需将PWM / NCO /任何信号连接到最低有效位。

测验

现在获得一些测试结果:我正在考虑的电阻器阵列的容差为±2%,但也可以以±1%甚至±½%的精度获得,但是由于我没有这些电阻,因此我只使用了单个1%电阻。我建立TIMER1一个的ATmega328为16MHz为8位PWM运转,和所使用的10位ADC采取一些测量。由于PWM,R-2R和ADC均参考VCC,因此我们可以将其分解,并仅检查从ADC读取的八个电平中的每个值,并将PWM设置为0%和100%。理想情况下,一个步骤的100%输入应等于下一步骤的0%输入(任何ADC读数的警告最多可减少两个,如ATmega328数据表的“ ADC特性”部分所述)。

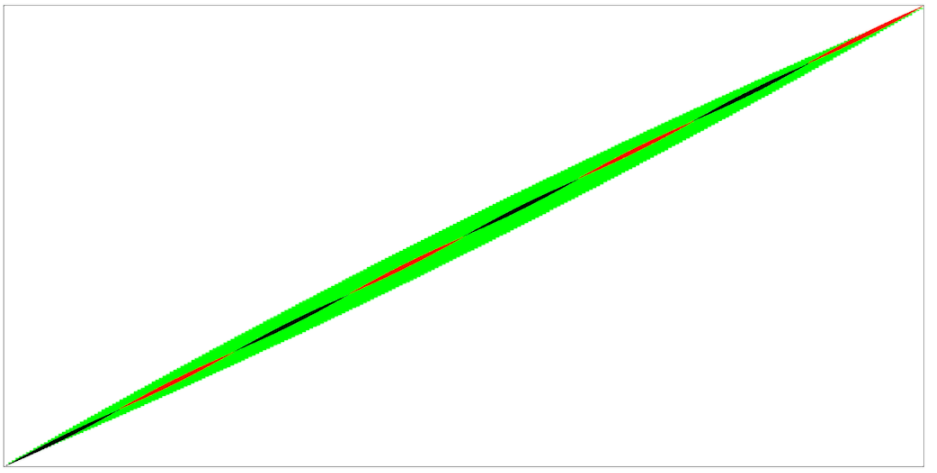

这些似乎是很合理的。然后,我使用了一种绰号为“ Slow-scilloscope™”的技术,该技术利用ATmega328的功能来安排带有计时器的AD转换,该计时器与产生PWM的计时器相同。因此,我们可以测量给定PWM周期内的纹波。图5是带低通滤波器的传统PWM(绿色)和混合电源(黑+红)的合成图。两者都使用过小的电容器,因此我们可以看到纹波。

图5 测量的PWM和混合DAC纹波

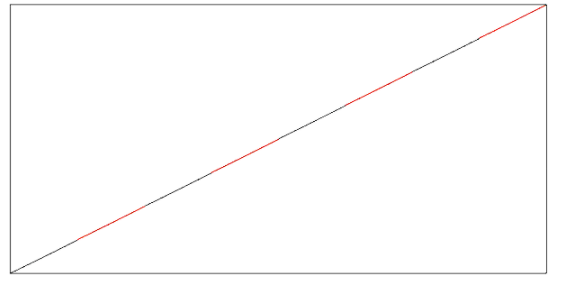

最后,图6是每个混合设置下非同步AD转换的(乏味)轨迹,允许纹波在结果中产生(或多或少)随机变化。这是使用一个较大的电容器以获得更实际的结果。

图6 测得的纹波,混合DAC,最终电容器值。

最后,我们已经看到,根据您的观点,PWM可以填充R-2R DAC步骤之间的空间,或者R-2R梯形图可以大幅度削减常规PWM加低通滤波器的纹波。或两者。

编辑:hfy

-

电容器

+关注

关注

64文章

6217浏览量

99534 -

PWM

+关注

关注

114文章

5181浏览量

213796 -

dac

+关注

关注

43文章

2291浏览量

190975

发布评论请先 登录

相关推荐

CD4046A想锁一个100K的方波信号,R1,R2需要怎么配置?

浅谈电容X5R和X7R介质(材质)的区别

TLV320AIC3204使用IN1L/R输入信号,经过ADC采样,将信号通过I2S和DAC同时在输出,可以实现吗?

TAS5766做L+R单声道输出,DAC-L和DAC-R如何处理较好?

TLV320aic3204提高DAC_R增益后录音效果变差且有杂音的原因?

TAS5431-Q1 IN_P/IN_N内部偏置电压为3V,是否需要控制IN_P输入电压小于3V,否则是否会出现满偏,导致音频失真?

无缓冲R2R DAC的误差计算—使用DAC11001A的示例

飞凌嵌入式-ELFBOARD DAC的基础知识

开尔文法测电阻的r1r2如何选择

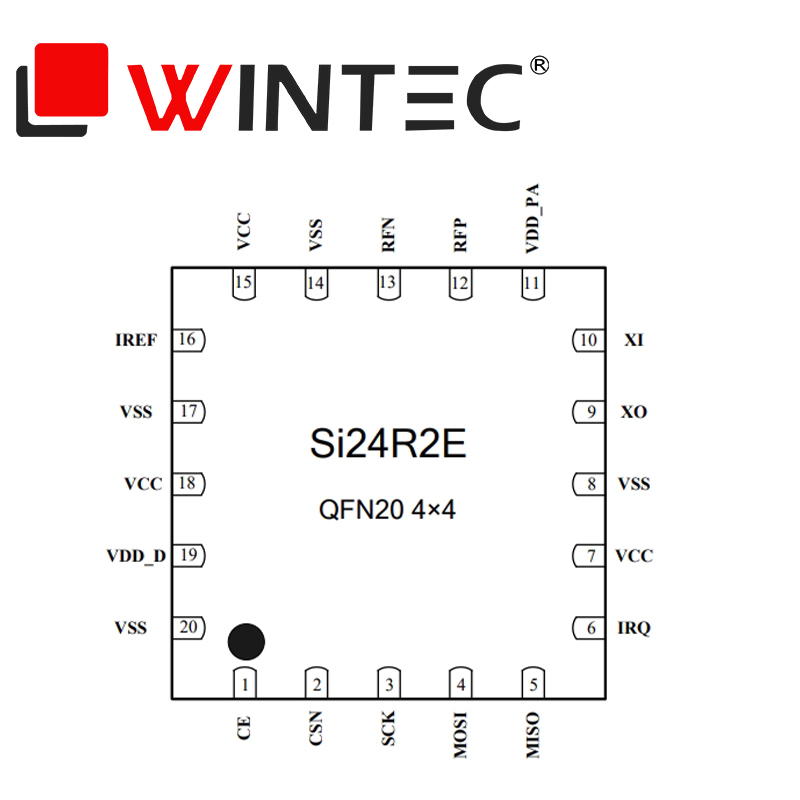

Si24R2E:2.4G有源智慧校园卡管理应用方案推荐

R2R和电阻串DAC架构之间的差异分析

DshanMCU-R128s2 R128 模组

关于混合PWM / R2R DAC的改进方案

关于混合PWM / R2R DAC的改进方案

评论