本应用笔记讨论了测试每个设计(特别是嵌入式系统)质量的最常见事物。它包括常见的错误源以及其他会影响或降低信号质量的因素。还介绍了实现良好数据测量应遵循的技术和程序。更重要的是,它可作为用户使用RIGOL的高效混合信号示波器集合应对嵌入式设计挑战的一种指南。

嵌入式设计,尤其是利用低速串行信号的设计工作,是数字电子设计发展最快的领域之一。大量消费和工业电子产品中的模块,FPGA和处理器之间进行通信的需求正以惊人的速度增长。定制的通信协议和总线的使用对于设计效率和上市时间至关重要,但是存在有时难以分析和调试的风险。在嵌入式应用程序中使用低速串行数据时,最常见的问题来源和类型包括时序,噪声,信号质量和数据。我们将推荐现代示波器中可用的调试技巧和功能,这些功能将使调试这些复杂的系统变得更快,更容易。

错误时间类型

时序对于任何串行数据系统都是至关重要的,但是要找到与组件,传输长度,处理时间和其他变量相关的系统时序限制可能会很困难。让我们从一个简单的16位DAC电路开始。首先,请确保您了解所使用协议的数据和时序规范。它是否在时钟沿对数据采样?当我们仍然期望好的数据时,时钟和数据能相差多远?换句话说:我们是否定义了时钟同步错误预算?一旦了解了这些时序要求,便可以通过实验验证Tx和Rx硬件子系统。现在我们可以分析系统级时序延迟和转换的整体精度,因为我们可以以时间相关的方式直接测量逻辑和模拟通道。

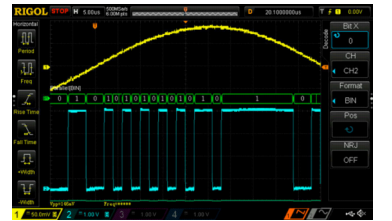

上面显示的是一个简单的示例,该示例测量通道2(蓝色)上的某个位,该位驱动DAC输出,从而在通道1(黄色)上产生正弦波。利用并行总线解码(图1),我们可以快速了解这条单线的过渡情况。但这并不能为我们提供所需的全部信息,因为DAC正在利用许多数据线来设置其输出电平。

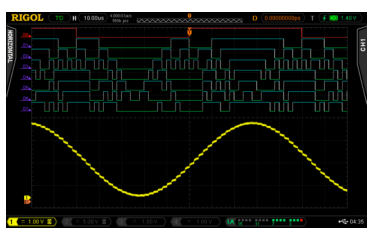

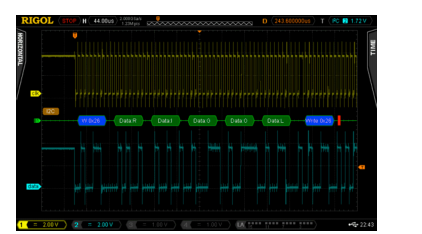

获取更完整的数据需要使用不同的方法。让我们将所有DAC线(图2)移到MSO的数字输入上。现在我们可以看到数字线路如何与DAC输出真正协调。

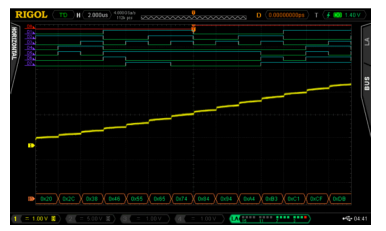

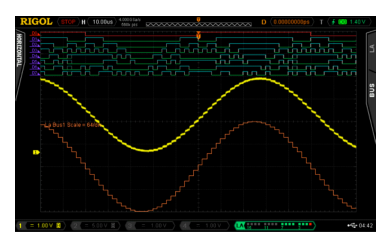

为了进一步研究,我们可以简化解码以显示十六进制值(图3)并放大,以便我们可以查看解码后的数据。另外,如果我们想以图形方式查看总线中的更改,我们可以在Logic Analyzer总线菜单中使用一个称为plot的函数(图4)。

这样可以图形化地显示位模式,以便于进行直观的分析。这是与DAC和A2D一起使用的完美选择,因为如果编码或解码方案出现问题,您可以立即获得反馈。

噪声

正确的串行数据测量中最常见的问题之一是系统噪声的处理。这些测量中的噪声可能来自多种来源,包括接地不良,带宽问题,串扰,电磁干扰(EMI)问题。有时问题出在设备上,但是改进的探测和测量技术也可以显着改善结果,而无需更换被测设备。好的第一步始终是确保我们使用的是最佳测量方法。

我们按照从易到难的顺序解决了这些问题。首先,我们可以看一下我们的探针连接。通常,我们会使用连接在探头上的鳄鱼夹接地带进行接地。假设我们做得正确,但仍然有问题,我们可能需要改用接地弹簧。接地弹簧连接的位置更靠近探头尖端,并显着减小了连接的回路面积。这可以显着改善噪声和信号质量(图5),特别是对于高速信号或对电容或耦合电压敏感的信号。对于这些类型的测量,所有Rigol探头均配有标准接地带和接地弹簧。

如果仍然存在接地噪声问题,请尝试将设备与地面隔离。示波器最好通过插头接地到AC电源接地。如果被测设备或系统的其余部分可以与地隔离,则可以消除接地环路。如果仍然存在接地噪声问题,则可以考虑使用诸如RP1100D之类的差分探头(图6),该探头可以在不参考示波器接地的情况下进行测量。

差分测量可能是清楚查看某些低速串行数据(例如LVDS总线)的唯一方法。这样的总线会故意移动参考线以最大程度地增加带宽并增加通信距离,但可能需要真正的差分探测或使用示波器的多个通道一起才能正确查看信号。Rigol有几种不同的探头类型可用于这些测量,包括RP1000D系列差分探头(通常用于高压浮动应用和RP7150 1.5 GHz差分探头(图7)或高速数据应用)。

讯号品质

监视和提高低速串行信号的质量是调试过程的关键部分。即使不存在噪声,阻抗不匹配,带宽和负载错误等问题也会影响信号质量。既然我们正在仔细研究这些信号的确切性质,那么重要的是验证我们使用示波器进行这些测试的方式。对于信号质量测试,我们将使用模拟通道,因为它们可以最好地查看信号中实际发生的情况,但是我们仍将进行一些解码。这需要一些额外的考虑。为了清楚地看到数据转换,我们绝对应该使用尽可能高的采样率。由于我们需要可视化高频分量,因此应将数字总线比特率的5倍采样视为最小值。以10倍的比特率进行采样应该可以使我们看到任何问题。但是,当我们解码信号时,示波器可能会使用全部存储器数据的子集来处理解码分析。

这一点很重要,因为您不必一定要以太高的速率完成解码。当使用更标称的接收器解码数据时,这可能掩盖您会发现的问题。在Rigol示波器上,解码是在整个采集中散布的1 Mpts内存上完成的。通过设置存储深度和每格划分的时间,用户可以确定他们是希望直接从模拟点还是从子集进行解码。以10倍的比特率进行采样应该可以使我们看到任何问题。但是,当我们解码信号时,示波器可能会使用全部存储器数据的子集来处理解码分析。

这一点很重要,因为您不必一定要以太高的速率完成解码。当使用更标称的接收器解码数据时,这可能掩盖您会发现的问题。在Rigol示波器上,解码是在整个采集中散布的1 Mpts内存上完成的。通过设置存储深度和每格划分的时间,用户可以确定他们是希望直接从模拟点还是从子集进行解码。以10倍的比特率进行采样应该可以使我们看到任何问题。但是,当我们解码信号时,示波器可能会使用全部存储器数据的子集来处理解码分析。这一点很重要,因为您不必一定要以太高的速率完成解码。

当使用更标称的接收器解码数据时,这可能掩盖您会发现的问题。在Rigol示波器上,解码是在整个采集中散布的1 Mpts内存上完成的。通过设置存储深度和每格划分的时间,用户可以确定他们是希望直接从模拟点还是从子集进行解码。当使用更标称的接收器解码数据时,这可能掩盖您会发现的问题。在Rigol示波器上,解码是在整个采集中散布的1 Mpts内存上完成的。通过设置存储深度和每格划分的时间,用户可以确定他们是希望直接从模拟点还是从子集进行解码。当使用更标称的接收器解码数据时,这可能掩盖您会发现的问题。在Rigol示波器上,解码是在整个采集中散布的1 Mpts内存上完成的。通过设置存储深度和每格划分的时间,用户可以确定他们是希望直接从模拟点还是从子集进行解码。

数据

任何低速串行应用程序的关键是能够快速,轻松地查看正在传输的数据。这意味着增加了在示波器上执行嵌入式解码的功能。解码会同时影响示波器的触发和显示。它将解码的总线显示添加到仪器的屏幕。您可以将值解码为ASCII或十六进制,八进制或二进制数据,具体取决于您要查看的内容。现在,您还可以触发这些值,以确保您正在查看最感兴趣的数据包。

寻找

适当的过采样和带宽的关键

如上所述,正确的采样对于进行正确的测量以及完全调试低速串行接口至关重要。模拟信号的一个好的经验法则是您要测量的信号带宽的5倍。这样可以将您的上升时间误差限制在2%左右。要查看有关高频信号分量的最佳细节,请设置您的示波器以使采样率也达到5-10倍。当使用数字信号时,这意味着以一位宽度采样5次。在数字线路上进行采样或用于解码时,过采样的重要性不那么重要,但请设置测量设备,使其与最终使用的LSS接收器相似。这使您有最大的机会专注于可能会导致问题的实质性错误。

接地,噪声和差分信号

正确探测和理解差分参考信号与接地参考信号的使用对于调试很重要。如果您的数据线未接地,请确保了解接地环路和接地耦合噪声对测量的影响。使用适当的探头技术和示波器上的高级降噪功能来限制噪声源。如有必要,将差分探头添加到您的测量系统中以提高

测量质量。

如何最好地查看低速串行信号

有很多方法可以在现代示波器上分析,查看和评估LSS总线活动。最佳方法因要查看噪声,速度或同步的单个位转换而有所不同。是否要查看完整的数据包;或者您想比较较长时间段内的数据包和数据包时序。确保您的基准测试工具可以让您看到所需的一切,并熟悉缩放,记录模式,事件表,深度内存和自动测量等功能,以及在考虑测试计划时它们如何相互作用以及如何在它们之间进行最佳转换。理想情况下,示波器使您能够查看所需的所有结果并快速切换模式以获取更多信息。

结束语

数字数据的嵌入式设计和调试是广泛的消费和工业应用中不断增长的测试要求。拥有正确的混合信号示波器可以使查看,分析和解决包括时序,噪声,信号质量和数据在内的问题变得更加容易和快捷。这提高了工程效率和上市时间。Rigol的支持UltraVision的示波器系列包括从70到500 MHz的混合信号选项,以及此处讨论的方法和测量的标准或可选功能,是功能强大的台式仪器,以前所未有的价值提供了不折不扣的性能。

编辑:hfy

-

FPGA

+关注

关注

1629文章

21736浏览量

603394 -

示波器

+关注

关注

113文章

6246浏览量

184958 -

接收器

+关注

关注

14文章

2472浏览量

71912 -

串行信号

+关注

关注

0文章

26浏览量

8504 -

差分测量

+关注

关注

0文章

5浏览量

5924

发布评论请先 登录

相关推荐

如何使用RIGOL的高效混合信号示波器集合应对嵌入式设计挑战

如何使用RIGOL的高效混合信号示波器集合应对嵌入式设计挑战

评论