目前,在建筑物早期火灾监测和报警上,还是一直沿用有线网络的方式,其线路遍布在建筑内,初装成本高,同时线路本身也是很大的火灾隐患。因而新型的无线火灾监测系统应运而生,该系统安装方便、快捷,且其成本更为低廉,有更大的应用空间。微控制器是火灾监测系统的核心部件之一,通用的微处理器和微控制器不能满足无线火灾监测系统中节点主控芯片低功耗、低成本的要求。

为了掌握无线火灾监测系统的核心技术,建立拥有自主知识产权的软硬件平台,推动我国无线火灾监测系统的发展,有必要开发出针对无线火灾监测系统的微处理器。本文完成了一款专用于火灾检测系统的微控制器芯片的物理设计。

1 SW-A芯片的架构

SW-A芯片是一款基于ARM Cortex-M0的专于无线火灾检测系统的专用数模混合型控制器芯片,总线采用AMBA AHB、APB 双总线架构,工作频率最高可达50 MHz,支持多级内部分频,待机状态下也可以极低的频率运行;内置一个高采样率的12位逐次逼近的8通道ADC,最多可依次对来自8个传感器(如温度传感器、烟雾传感器、光强传感器等)的信号直接进行采样、转换、保存,检测主程序可任意读取目标传感器对应的采样数据进行处理、判断是否发生火灾。

内置18 KBSRAM,可灵活切换作为FLASH、RAM使用,满足火灾监测和简易处理程序的存储。支持ISP(在系统编程)操作和IAP(在应用编程)操作,既便于火灾监测主程序的更新升级,又便于软件编写优化。接口包括工业标准的UART 接口、SSI 通信接口(支持SPI、MicroWire 及SSI 协议),还有3 组(6 通道)PWM,丰富的接口和功能模块使该款芯片在功能拓展方面有较大潜力。

2 SW-A芯片的物理设计

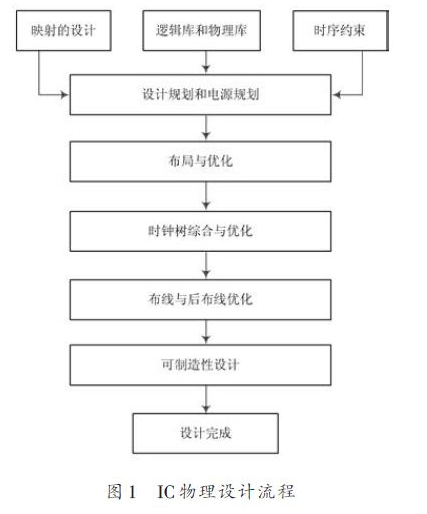

2.1 采用的物理设计流程

SW-A芯片的物理设计借助Synopsys公司的EDA工具IC Compiler 进行,采用IC Compiler 典型的设计流程。基于台积电(TSMC)180 nm CMOS工艺进行。物理设计准备就绪后(设计逻辑库、设置物理库、设置TLU-Plus相关文件以及设置读入的门级网表与标准延时约束),即可开始物理设计,依次完成设计规划(Designplanning)、布局(Placement)、时钟树综合(Clock tree Syn-thesis)、布线(Routing)直至设计完成(Chip Finish)。

2.2 设计规划

设计规划(Design Planning)是芯片物理设计中非常重要的一步;主要包括布图规划(Floorplan)电源规划(Powerplant)。

通常情况下,在布局开始之前,设计者往往需要花费大量的时间来进行布图规划(Floorplan)和电源规划(powerplan),设计规划的好坏直接决定芯片的功耗、标准单元的拥塞的、时序收敛、电源稳定性等。所以设计规划是整个物理设计过程中反复次数最多、手动设计最多的一步。

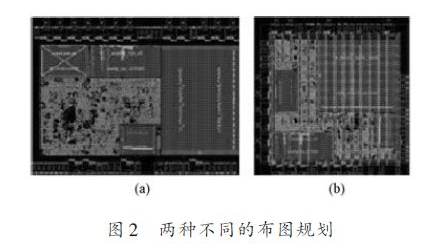

布图规划(Floorplan)要完成IO 排布、PAD 摆放、Macro(包括模拟模块、存储单元等)的定位以及芯片的形状、拥塞度(Congestion)和面积等的设定。作为一款面向用户的控制芯片,IO 的排布必须综合考虑用户的需求与设计的要求,不同功能PAD 的纵横向尺寸也不同。本文将纵横两向尺寸均较大的PAD置于芯片的南北两边,将单向尺寸较小的PAD 置于芯片的东西侧且大尺寸边朝向南北(见图2(a)),相比较于将双向尺寸均较大PAD 置芯片的四周(见图2(b)),这样的设计非常有效的减小了芯片的面积。

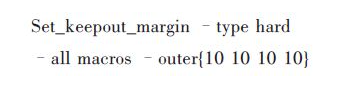

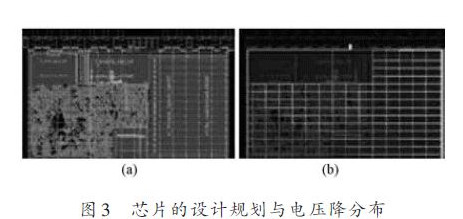

本芯片需要定位的Macro 有SRAM、ROM、ADC 以及ANALOG_TOP,本文综合考虑它们与IO 的位置关系将它们定位于芯片的四周,这样可以芯片中保留成片的空白区域来放置标准单元。为了保证Macro与PAD 及标准单元之间的互联线,在每个Macro的四周这只一个空白区,这个区域内任何情况不允许摆放标准单元。具体命令如下:

本芯片在放置标准单元和Macro 的核心区与PAD之间设计40 μm 的预留区,用于摆放电源环(PowerRing)及互联走线。为防止标准单元重叠放置,用命令可保证标准单元只能置于高度大于10 μm 的通道内。设置好芯片布图规划可使用命令creat_fp_placement进行预布局。本芯片使用TSMC 180 nm 工艺设计生产,要求工作电压为1.8 V,可容忍最大电压波动为±10%,所以本文在进行电源规划时,综合考虑了芯片的供电需求、互联线造成的电压降(IR-Drop)及较小的电源网络面积,设计了两个电源环(Power ring)和纵横各14条电源带(Strap)。经过分析电源网络(Analyze Pow-er Network),本设计最大的IR-Drop 为29.7 mV.图3(a)是芯片的设计规划,图3(b)是芯片的电压降分布图。

2.3 布局

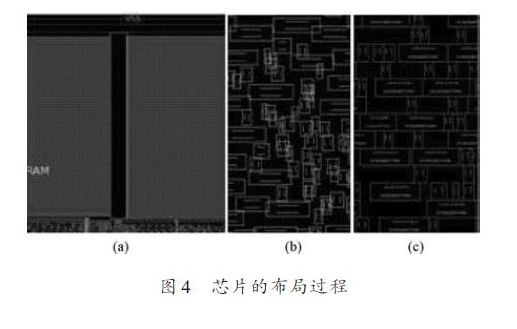

布局(Placement)的好坏是决定芯片物理设计成败的关键。布局的主要任务是完成设计中标准单元的摆放和修复建立时间(setup time)。布局正式开始之前需使用命令check_physical_design命令检查布局准备是否完成,必须保证:所有Hard Macro 和IO 等的位置以固定;设计中所有逻辑pin和物理pin一一对应;所有的逻辑单元都有与之对应的物理单元;设计中所有单元的尺寸都已固定。为了方便互联走线,在开始摆放标准单元之前,可以将芯片内特定区域设置为布局限制区(Place-ment Blockage)。ICC工具多种形式的限制,如禁止粗略布局时摆放标准单元、只允许布局优化时摆放标准单元、只允许布线等;本设计中设置了多处布局限制区,以方便ADC、ANALOG_TOP 等与IO 之间的连线(见图4(a))。

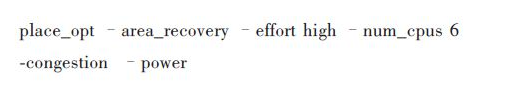

布局准备就绪后可使用命令place_opt配合附加约束进行布局,该命令执行错略布局(coarse place)、高扇出网络合成(high-fanout net synthesis)、物理优化(physicaloptimization)直至合法化(legalization),由前三步确定单元的位置(见图4(b)),通过合法化最终将标准单元正确的摆放在计算好的位置上(见图4(c))。本文物理设计的具体命令如下:

要求工具对除关键时钟路径外的其他面积进行修复,努力程度高,通过选项“-congestion”控制工具尽可能的降低芯片的拥塞度以便利后续布线,通过选项“-pow-er”控制工具优化泄漏功耗、动态功耗并且进行低功耗布局。

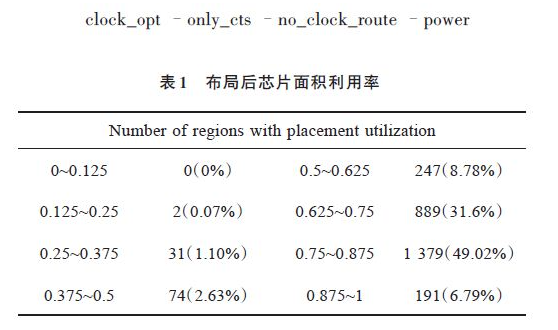

完成布局后芯片的面积利用率如表1所示,拥塞度的集中在0.625~0.875之间,拥塞度适中,既没有因为芯片利用率过低而浪费芯片面积,也不会因为拥塞度过大而导致后续设计困难甚至重新设计。

2.4 时钟树综合

时钟树综合(Clock Tree Synthesis)的主要任务之一就是将时钟偏差控制在可接受范围内,保证芯片高效无误的工作。本芯片的时钟树综合策略如下:时钟树的逻辑综合(clock-cts)、时钟树的物理综合(clock-psyn)以及时钟树的布线(clock-route)。时钟树的逻辑综合阶段只完成两项工作:通过计算各条时钟路径上的延迟,得到需要插入缓冲器(buffer、inverter)的位置及尺寸(由-only_cts命令选项控制);由于时钟网络的功耗占总功耗的比重非常大,所以在时钟树综合时必须进行功耗优化(-power)此阶段并不进行布线。具体命令如下:

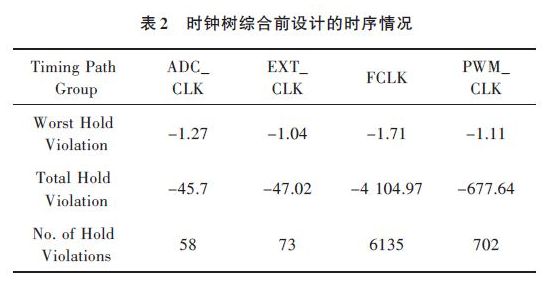

时钟树的物理综合阶段将插入的缓冲器摆放至准确的位置,进行RC提取,参照延迟约束文件(SDC)检查时钟网络的的最大插入延迟、最小插入延迟、最大时钟偏差以及最大转换时间等并对设计中出现hold违反进行修复,为了便利非时钟网络布线,此时需要增加-ar-ea_recovery选项,以减小连线面积,此阶段依然对功耗进行优化。在完成时钟树布线时,本文采用arnoldi模型来精确计算时钟树的延时并15次循环迭代法进行时钟布线。表2是时钟综合前本设计的时序情况,显而易见有多条关键路径并存在较多建立时间违反;完成时钟树综合后再进行时钟检查,未发现时钟违反,表示时钟树综合完成。

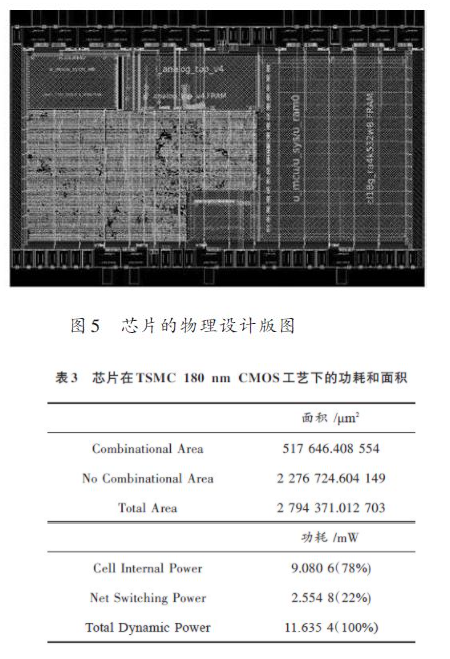

2.5 布线与芯片完成

本文将布线及其优化分开来做,首先在初始布线阶段完成全局布线(global routing)、详细布线(detail rout-ing)和检查与修正(search&repair),然后采用拓扑算法对布线进行优化,同时对电流漏功耗进行优化。为了防止天线效应的发生,在芯片完成阶段对芯片进行了天线效应修复设计,此时芯片中依然存在空白区域,需要填充filer 以满足DRC 的要求。图5 是该芯片的物理设计版图,表3 是该芯片的面积与功耗,可见总面积为2 794 371.012 703 μm2,总功耗为11.635 4 mW.经过仿真后证明芯片于50 MHz时钟频率下正常工作,满足设计要求,证明本次设计是正确有效的。

3 结语

本文基于TSMC 180 nm 工艺完成了一款用于无线火灾监测系统中的微处理器芯片的物理设计,采用不同策略分别完成芯片的布图规划、布局、时钟树综合及布线等设计步骤后得到了该芯片的版图及面积、功耗等报表,物理设计后芯片的各项设计指标均满足设计要求,证明了该芯片物理设计的正确性。

编辑:hfy

-

微控制器

+关注

关注

48文章

7565浏览量

151579 -

ARM

+关注

关注

134文章

9105浏览量

367923 -

TSMC

+关注

关注

3文章

177浏览量

84531 -

微处理器

+关注

关注

11文章

2264浏览量

82535

发布评论请先 登录

相关推荐

微处理器芯片正常工作应具备哪些基本条件?

清溢光电:已实现180nm节点掩膜版量产 佛山基地2025年末迁入设备

嵌入式微处理器的分类 嵌入式微处理器的种类和型号

嵌入式微处理器的定义与发展 嵌入式微处理器种类和型号

嵌入式微处理器的类型与特点 嵌入式微处理器技术的优缺点

嵌入式微处理器有哪几类 嵌入式微处理器包含哪些重要参数

嵌入式微处理器的功能 嵌入式微处理器原理与应用

什么是嵌入式微处理器? 嵌入式微处理器的区别

主流嵌入式微处理器的结构与原理是什么 常见的嵌入式微处理器类型包括

微处理器属于专用集成电路吗对吗

什么是嵌入式微处理器?嵌入式微处理器有哪些?

嵌入式微处理器的原理和应用

基于TSMC 180nm工艺的微处理器芯片的物理设计

基于TSMC 180nm工艺的微处理器芯片的物理设计

评论