随着电信数字载波系统T1和E1的出现,数字重定时器在1960年代引起了人们的关注。这些系统在屏蔽双绞线上传输多条语音电路通道,每隔几千英尺安装一个数字重定时器。它们在当时是先进的,并且使用了与当今高速重定时器相同的技术,包括均衡,时钟数据恢复(CDR),线路编码和成帧。

对于每个序列化器/反序列化器(SerDes)用例,总是存在需要增强覆盖范围的其他应用程序。转接驱动器或转接器芯片的典型应用是:

转接驱动器和转接器比较

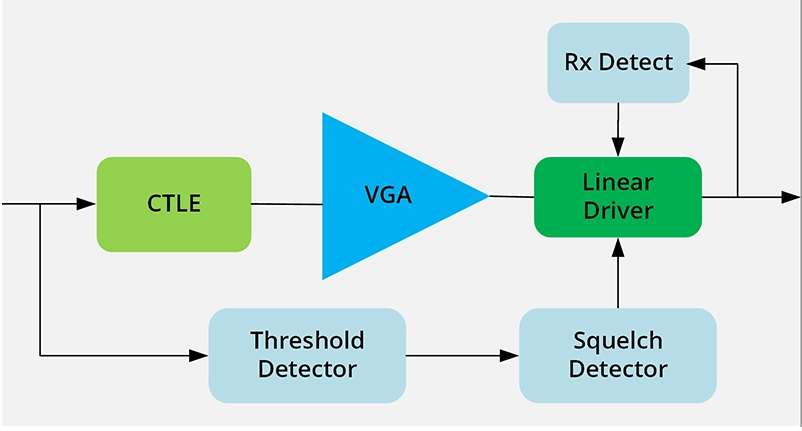

典型的转接驱动器数据路径包括连续时间线性均衡器(CTLE),可变增益放大器(VGA)和线性驱动器。CTLE用于均衡信道中经历的频率相关损耗。VGA用于恢复信号的幅度。线性驱动器用于以正确的阻抗驱动通道。

转接驱动器通常具有输入信号丢失阈值和输出接收器(Rx)检测功能,以及一个静噪检测器,可以以差分方式检测低速通道上是否存在通信信号。图1给出了一个典型的转接驱动器框图。

图1此典型转接驱动器的框图显示了一个CTLE,用于均衡通道中与频率有关的损耗; VGA,用于恢复信号幅度;线性驱动器,用于以正确的阻抗驱动通道。

模拟转接驱动器限制

模拟转接驱动器的三个主要缺点是:

- 转接驱动器会放大信号及其内部噪声。原始发射机在有损信道上发送具有高信噪比(SNR)的信号。转接驱动器中的CTLE和放大器具有各自的本底噪声。当信号被放大时,这两个本底噪声的组合随信号一起增强。当最终的接收器试图恢复数据时,它必须与放大的噪声抗衡,从而限制了转接驱动器的利益。

- 转接驱动程序仅部分清除符号间干扰(ISI)。通道在通带中的频率相关损耗会在多个位时间内抹掉位。CTLE可以均衡一部分ISI,但是CTLE永远无法精确配置以完全纠正所有问题,而且不均衡的通带纹波会留下额外的ISI。最终接收者必须应对这个残留的ISI。

- 转接驱动器不会恢复眼图宽度和相关的抖动。在接收器处保持良好的眼宽对于无差错性能至关重要。多种因素会降低眼图宽度,包括热噪声,偏斜,模拟失配,上升/下降时间失配,端接失配,ISI和电源噪声。转接驱动器的存在进一步降低了这些因素中的大多数,使信号恢复更具挑战性。

结果,无法利用转接驱动器之前和之后的链接的完整范围。在每个地方都必须使用较短的走线长度,以最大程度地减少增加的噪声,残留ISI和狭窄眼宽的影响。由于这些问题,在所有设想的使用场景中,系统开发人员要负担很大的负担,以了解和表征转接驱动程序对最终系统的复杂影响。

有关降低信号完整性的通道损伤的类型以及重新驱动器和重新定时器在纠正它们中所起的作用的更多见解,请参阅《使用以太网重新定时器和重新驱动器保留信号完整性》。

重定时器如何工作

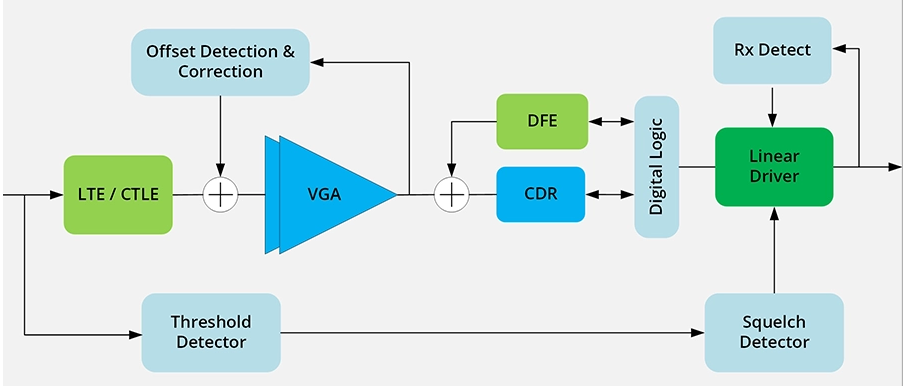

典型的重定时器是一种混合信号模拟/数字设备,它具有协议感知能力,并且能够提取嵌入式时钟,完全恢复数据并使用干净的时钟重新传输数据的新副本。除了在转接驱动器中也可以找到的CTLE,VGA和驱动器级以外,重定时器还包含CDR电路,长尾均衡器(LTE)和判决反馈均衡器(DFE)。

LTE补偿了长期的脉冲响应损伤,DFE充当了非线性均衡器,抑制了由于诸如高频损耗和陷波之类的信道缺陷而导致的ISI。

内部数字逻辑,状态机和/或微控制器管理CTLE,VGA,LTE和DFE模块的自动适配,并实现协议链接训练和状态更新。图2给出了典型的重定时器框图。

图2除了在转接驱动器中还可以找到的CTLE,VGA和驱动器级之外,典型的重定时器还包括CDR电路,LTE和DFE。

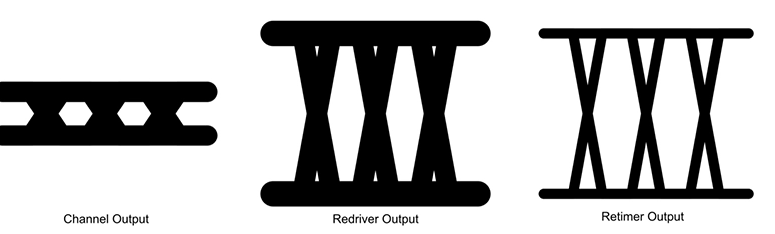

简单来说,转接驱动器仅放大信号,而转接定时器则完全恢复数据并发出清晰的新副本。图3对此进行了说明,并显示了如何通过重新驱动器增强衰减的眼图张开度以及如何通过重新定时器完全重新生成。

图3三个示例-通道衰减的眼(左),转接驱动器后的眼(中)和重定时器后的眼(右)-说明了重驱动器如何增强信号以及重定时器如何重新生成信号。

为了实现其目标,重定时器必须了解协议。重定时器监视通过它的链接配置事务,并在正确的模式下进行设置。在某些情况下,重定时器也参与链接设置操作。由于采用了这些自动化步骤,因此无需手动调整特定的通道,电缆和形状因数,从而使以更高数据速率进行的系统集成变得更加简单。

高速规格的定时器

最近发布了许多高速且难以实现的SerDes规范,包括USB4,PCIe 5.0,CEI-28G和CEI-56G中所包含的规范,以及仍在继续的PCI 6.0和CEI-112G规范。正在开发中。所有这些新标准旨在满足对更高数据吞吐量的需求。

二十年来,八十年代的SerDes及其前身是由光学互联网络论坛(OIF)和IEEE 802.3以太网委员会组成的。每一代厂商都开发了与协议无关的比特级重定时器产品,以使系统制造商能够进一步发展。

这些SerDes和相应的重定时器已在电信,以太网,因特拉肯,RapidIO,串行高级技术附件(SATA),串行附件(SCSI)SAS,光纤通道,InfiniBand和众多专有系统中广泛使用,改装或影响。转接驱动器芯片在OIF /以太网系列生态系统中从未普及,这是因为通常设计更为严格的链接会占用链接余量。

PCI Express(PCIe)是高速串行计算机扩展总线标准。它是用于个人计算机图形卡,硬盘驱动器,SSD,Wi-Fi和以太网硬件连接的标准主板接口。转接驱动器很好地满足了以8 Gbps通道运行的PCIe 3.0规范。PCIe 4.0将速度提高了一倍,达到16 Gbps通道,转接驱动器难以解决该问题,并为系统实现者带来了适度的收益。

2019年5月,PCI-SIG标准组织正式发布了PCIe 5.0规范,数据通道运行速度高达32 Gbps。尽管速度的提高以及对扩展能力的需求增加,但PCIe转接驱动器的道路似乎已接近尾声。当我们前进到即将到来的PCIe 6.0标准时,PAM4的脆弱性甚至使重新考虑驱动程序成为一个难题。

然后是通用串行总线(USB),这是用于计算机,外围设备和其他计算机之间接口的行业标准。USB 1.0于1996年发布,随后是USB 2.0于2000年发布。尽管USB-IF未对转接驱动器进行标准化,但它们在范围扩展和电压兼容性方面所提供的优势使得它们成为必不可少的。

随着2010年USB 3.0的发布,USB中信号完整性的挑战变得更加明显,增强型转接驱动器产品进入市场,以扩展Superspeed 5 Gbps链路的范围。USB 3.1和Superspeed + 10 Gbps链接延续了这一趋势。USB 3.2规范通过USB-C连接器将USB 3.0中的单通道模式扩展为双通道,并进一步增加了转接驱动器的应用程序数量。

在2019年8月,USB-IF正式发布了USB4规范,该规范将链接的性能进一步提高到了20 Gbps通道(2通道上为40 Gbps链接)。20 Gbps信号比其前任产品脆弱得多,因此更容易受到ISI,通带纹波,抖动源,模拟失配,终端失配,线对内偏斜,反射,热噪声和电源噪声的影响。结果,USB转接驱动器的时代即将结束。

更新的高速互连规范将推动新一代的信号调理解决方案。数字重定时器是在保持信号完整性的同时,通过具有挑战性的信道发送超高速数据的关键要素。在高于10 Gbps的速率下,使用转接驱动器面临许多挑战。这是预期重定时器支持并将其写入最新规范的一个核心原因。

总之,信号调理技术(例如重新驱动器和重新定时器)在许多系统环境中很有用。随着数据速率超过10 Gbps,在许多应用程序中,转接驱动器的适用性已经减弱。在OIF /以太网生态系统中,重定时器已成为首选的信号调节器。在PCIe生态系统中,PCI 4.0是转接驱动器的最后一口气,而转接定时器则提供了更好的解决方案。在USB生态系统中,USB4是转接驱动器已成为系统问题的错误答案的过渡点。

支持协议的重定时器解决方案为USB4应用提供了必要的信号完整性性能,并提供了健壮的,无借口的开发路径和经济高效的系统解决方案,可满足消费者的需求。

Brian Holden是Kandou的标准副总裁。

保罗·威尔逊(Paul Wilson)是Kandou产品行销总监。

编辑:hfy

-

pcb

+关注

关注

4319文章

23096浏览量

397800 -

线性驱动器

+关注

关注

2文章

18浏览量

15810 -

定时器

+关注

关注

23文章

3248浏览量

114781

发布评论请先 登录

相关推荐

DS150DF1610 12.5至15Gbps 16通道重定时器数据表

DS280DF810 28Gbps多速率8通道重定时器数据表

DS125DF111多协议双通道9.8Gbps至12.5Gbps重定时器数据表

DS110DF111低功耗、多速率、双通道重定时器数据表

DS250DF810 25Gbps多速率8通道重定时器数据表

DS250DF410 25Gbps多速率4通道重定时器数据表

DS125DF1610 9.8至12.5Gbps 16通道重定时器数据表

DS110DF1610 8.5至11.3Gbps 16通道重定时器数据表

DS250DF210 25Gbps多速率2通道重定时器数据表

DS250DF230 25Gbps多速率2通道重定时器数据表

DS560DF410具有交叉点的56Gbp多速率4通道重定时器数据表

DS160PT801 PCIe4.0、16Gbps、8路(16通道)重定时器数据表

高速数据通道中重定时器的作用分析

高速数据通道中重定时器的作用分析

评论