无论芯片设计工程师有多认真,以及他们使用什么实施工具,验证团队在分解自对准双图案(SADP)设计的签核验证期间将始终遇到设计规则检查(DRC)错误。如果设计是手动分解的,则工程师必须弄清楚需要进行哪些修改,然后在可能的多个分解层中进行更改以解决错误。如果使用设计实现工具自动生成分解后的布局,则校正过程通常需要工程师对目标金属形状进行手动更改,然后重新运行分解过程以确定错误是否已解决(不引入任何新方法)。错误)。两种方法都是迭代且耗时的,

GlobalFoundries和Mentor(西门子业务部门)通力合作开发EDA工具以加快此过程,发现了工具功能,该功能可以自动分解布局,或修改现有的部分或完全分解的布局,同时使用内置的签发DRC规则识别功能错误可视化可修复现有的DRC错误,并避免创建新的错误。在SADP设计中自动修复DRC错误的关键是使工具能够对分解进行细微的改变,从而仅稍微改变晶片上形成的金属形状(与原始绘制的目标金属形状相比)。关键因素是确保这些物理变化均不会影响设计的布局与原理图(LVS)连通性,或将任何通孔连接移至金属,以避免在电路中产生功能或电阻变化。

通过修改分解过程中生成的切割蒙版,可以更改晶圆上金属的形状。这些剪切修改以三种形式发生:剪切滑动,剪切合并和剪切掉落。

切滑

要使用填充/切割SADP分解一组目标金属形状,请在每个目标金属形状线末端的末端放置一个切割。这些切割将轨道分为多个部分-有源目标金属或虚拟金属。在实际设计的实验中,我们发现在确定切口的位置时严格遵守绘制的目标形状会造成许多类型的DRC违规。

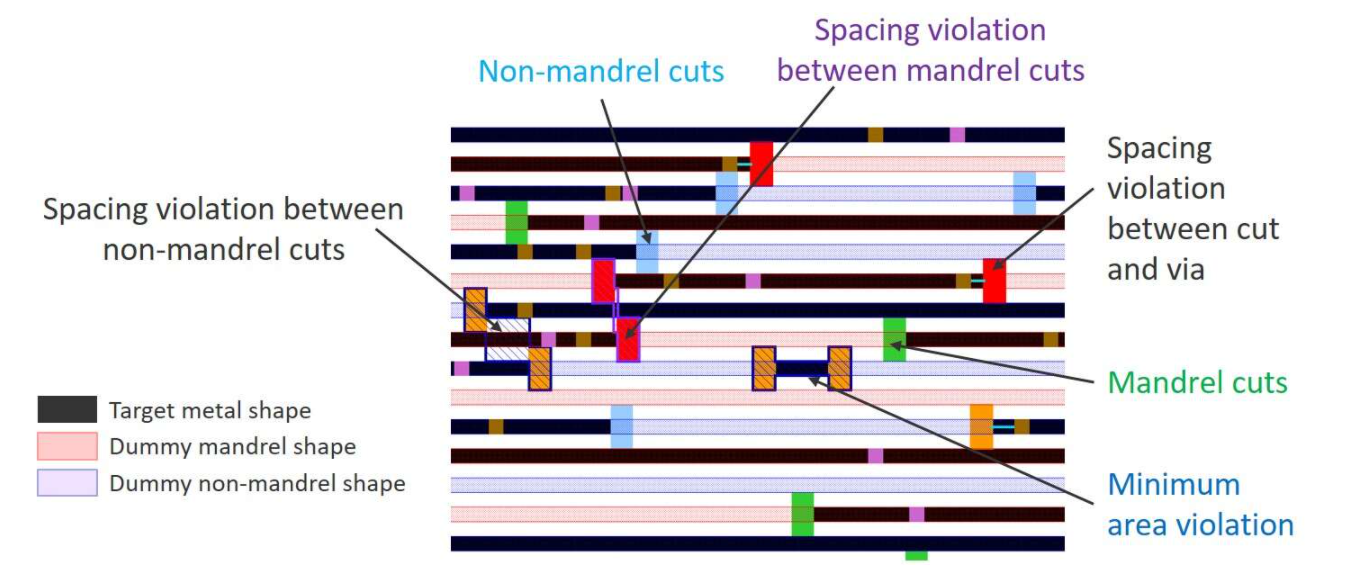

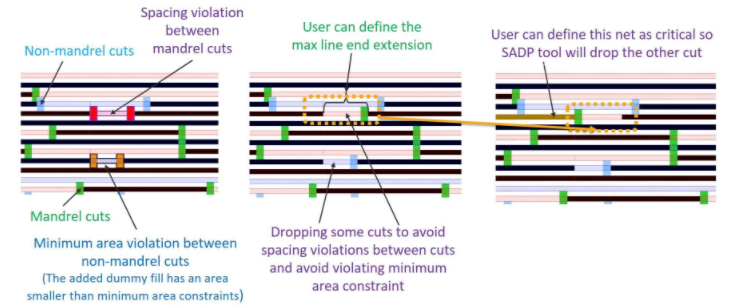

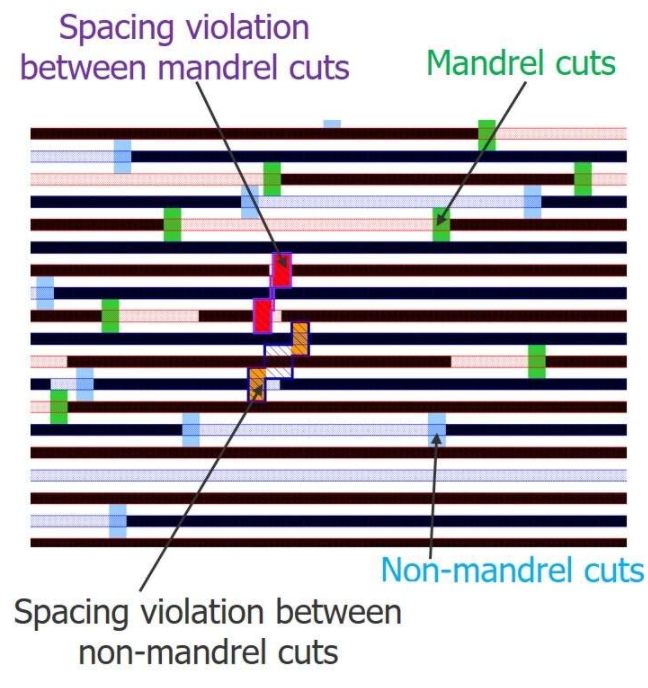

图1展示了将切口放置在目标金属形状的线端时可能发生的四种不同类型的DRC违规:

- 当两个心轴切口之间的距离太近而无法打印在同一面罩上时,就会发生心轴切口之间的间距冲突。

- 当两个非心轴切口之间的距离太近而无法在同一掩膜上打印时,就会发生非心轴切口之间的间距冲突。

- 由于修整靠近通孔的线将无法满足超出通孔的最小金属线端延伸的要求,因此在切口和通孔之间会发生间距冲突。

- 将轨道修整为两个切口之间的一小段时,会产生不符合最小面积要求的金属段,从而导致最小面积违规。

在此过程中,有两种类型的切割:一种是选择性地切割心轴轨道,另一种是选择性地切割非心轴轨道。由于这两种切割类型对特定的轨道类型具有选择性,因此它们之间没有间距限制。但是,每种切割类型在其内部确实都具有间距限制。

图1由线端削减导致的DRC规则违规

您可能会问:“为什么设计实现工具会创建目标金属形状,或者让您创建目标金属形状,当分解时会导致这些违规?”答案本质上是对以下更普遍的问题的古老答案:“为什么设计实现工具会创建未通过签名DRC检查的任何布局,或者让您创建任何布局?”设计实施是一个非常困难的过程,并且第一次从实施工具中生成相对于签到平台的DRC清洁版图的可能性几乎不存在。这就是为什么存在签发DRC的原因,以及它如此重要的原因。

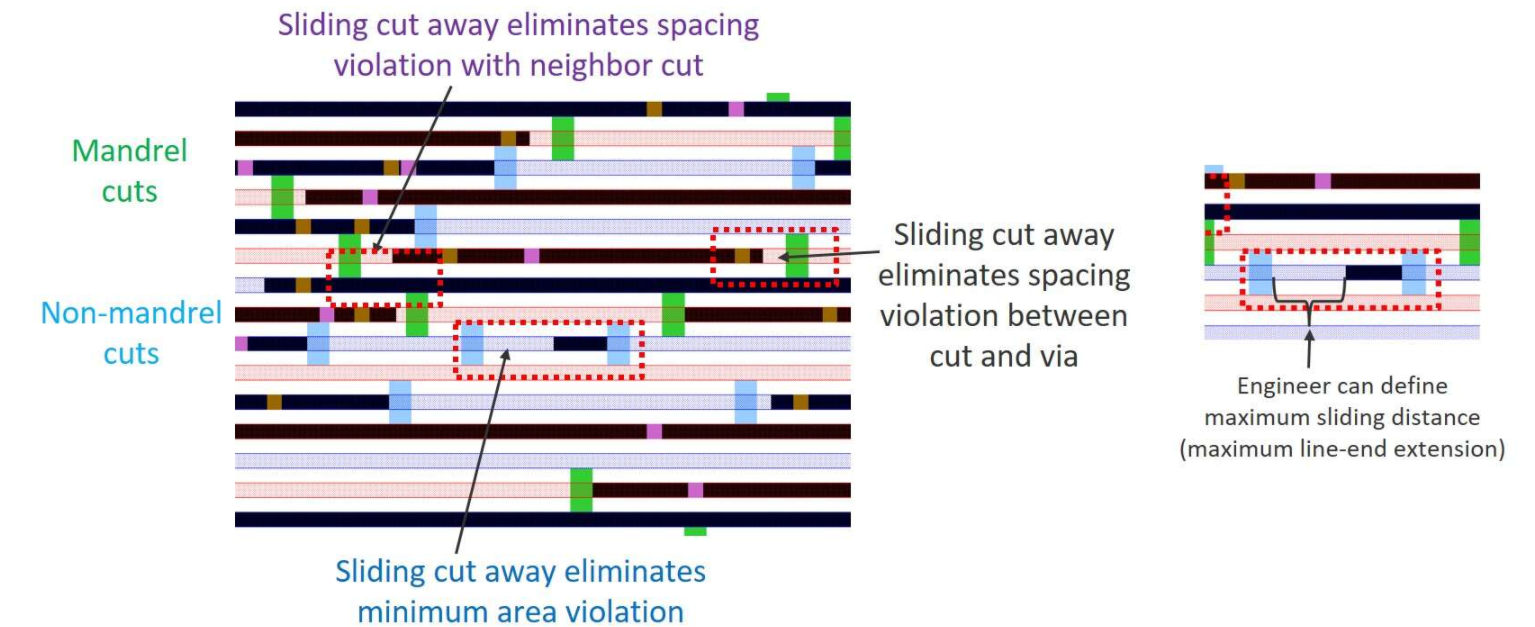

切口滑动的概念是将一个或多个切口的位置从生产线末端移开,以解决违反DRC的问题。构建此类功能的技术挑战是移动切割会更改与所有其他切割的交互。设计师面临的挑战是找到相互作用的多组切割的最佳布局,以解决尽可能多的错误,同时还要尝试最小化对线端扩展的更改。

图2显示了如何使用切割滑动来避免由线端切割引起的DRC错误。某些裁切已从其原始行尾位置转移。将切口从目标金属形状的边缘移开具有在晶片上制造时延伸目标金属线的效果。请注意,通孔没有移动,因此电连接性和路径长度没有变化[8]。这些移动裁切放置的好处在于,现在已经消除了所有四个原始DRC违规行为。

图2由线端切割引起的DRC规则冲突可以使用切割滑动自动修复。

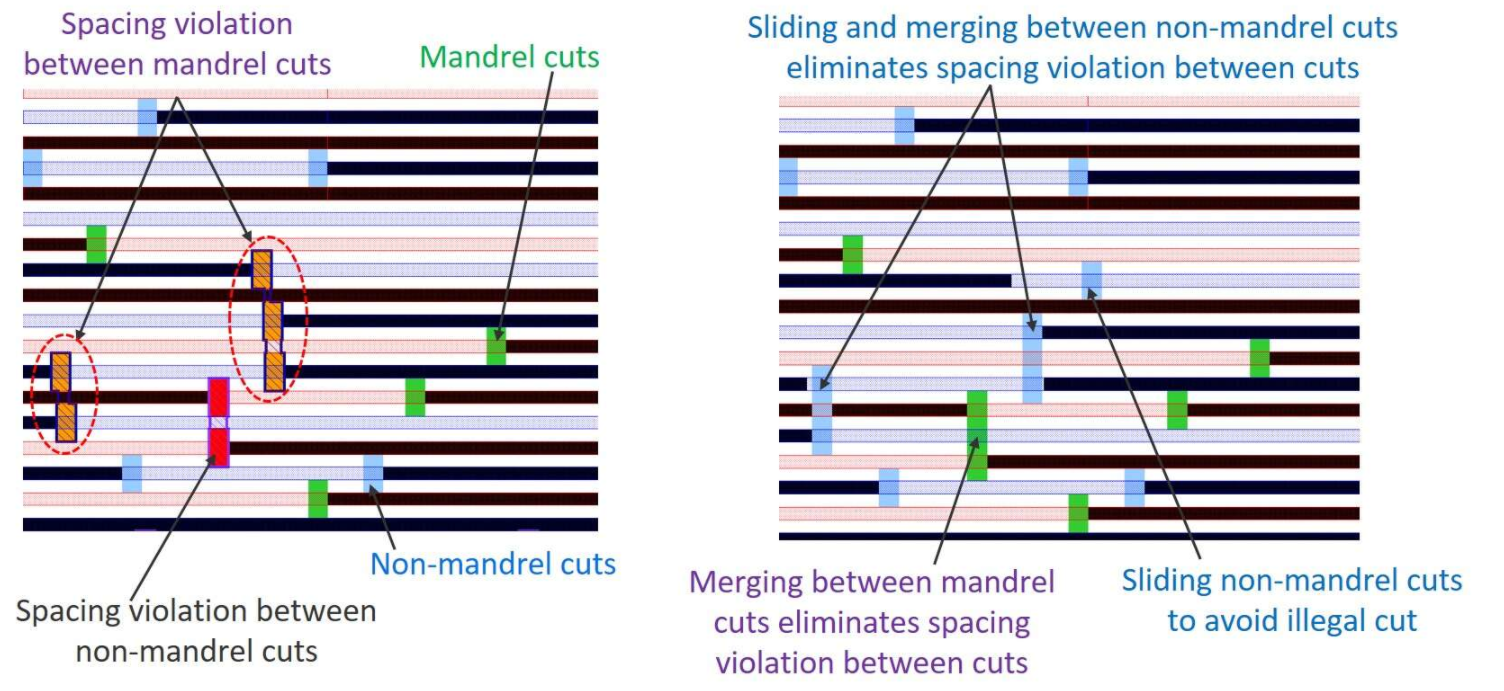

切合并

有时没有足够的可用空间来单独使用切削滑动来满足所有DRC约束。在这些情况下,合并合并可能会提供解决方案。如果切口之间的距离不能足够远,不能满足最小切口间距的要求,则一种替代方法是在垂直方向上对齐两个或多个切口,并延伸其面向的尖端以将它们合并为一个更长的矩形切口。图3显示了具有三个切口间距冲突的布局,可以通过滑动和合并各种切口来解决。

图3使用剪切滑动和剪切合并自动修复DRC规则冲突

对于铸造厂来说,表征制造过程的特性以决定可以切割多长时间以及可靠地进行成像和蚀刻非常重要。分解和自动修复功能使设计人员能够限制可用于解决错误的最大切割长度。

切滴

解决DRC错误的第三种方法是完全放弃切割。最初,这听起来很荒谬。切口将线分成单独的不连贯部分。如果您将两块金属短接在一起,则会遇到各种LVS问题。但是,如果您仔细观察典型的布局,通常会发现两个目标(电活性)金属件之间的间隙太大,以至于有两个切口在它们之间形成了一块假金属。如果您放下这两个切口之一,它只会延长两个线端之一,但仍会使两个活性金属形状保持断电状态。

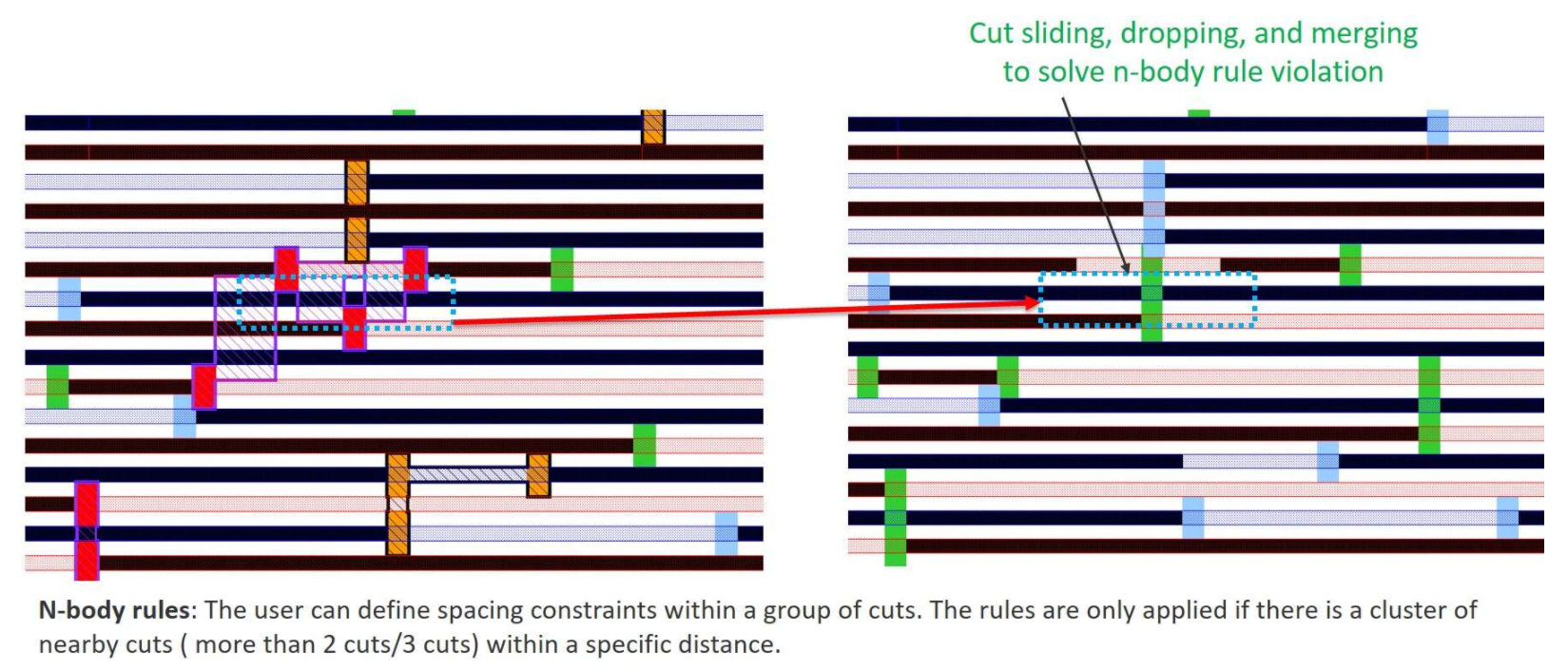

N体DRC规则非常复杂,并且经常在设计实现中引起问题,因为它们涉及仅在三个或更多同时进行交互的切口中应用的约束。图4显示了一个非常复杂的N体DRC规则的有趣示例,该规则通过剪切滑动,剪切合并和剪切掉落的组合得以解决。

图4通过使用剪切,合并和滑动来自动修复高级N体DRC规则冲突

在这些情况下,删除或合并剪切的能力是一个强大的选择,因为它从本质上减少了交互剪切的数量,这可能具有完全消除约束的效果。

限制切割滑动和切割合并

尽管所有这些技术都可以有效解决设计上的DRC违规问题,但我们很快认识到,仅在没有任何类型约束的情况下应用它们是没有意义的。尽管设计更改不会影响LVS连接性或路径电阻,但对电容的影响确实很小。为了解决这些技术的潜在影响,我们共同努力,定义并实施了一系列可以在工具中定义和使用的约束和控件。

第一个约束是嵌入到工具功能中的固有优化目标。它试图最小化所做更改的数量和幅度,同时仍解决所有可能违反DRC的行为。该目标将优化引擎引导至限制更改的寄生影响。

第二个约束是用户可定义的。它使设计人员可以指定任何给定更改所允许的最大行尾扩展量。如果更改会使线端超出指定的限制,则此限制限制了切割滑动(有时是切割掉落)的数量。此约束条件确保没有任何一条线路会经历大量的额外电容。

第三个约束也是用户可定义的,允许设计人员将特定的金属形状指定为关键路径网。在所使用的Calibre工具中,有多种现有方法可以读取此类网络名称信息并得出哪些多边形属于这些网络。SADP工具使用此派生的属于关键网络的多边形集来确保这些优化中的任何一个都不能扩展这些多边形的线端。

图5显示了应用此类约束如何改变工具选择的解决DRC违规的解决方案。这种增加的“智能”功能可以最大程度地减少所做任何更改带来的寄生影响,同时仍可提供令人印象深刻的DRC自动修复结果。

图5应用了各种切割修改约束的自动修复结果

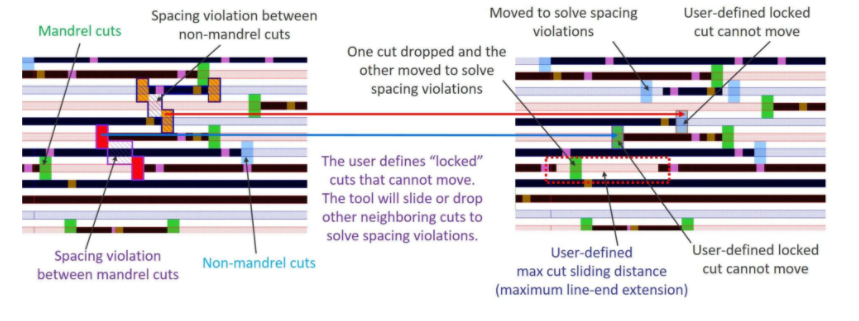

限制这些自动修复优化的另一种更有针对性的方法是使用用户定义的“锁定”剪切。可以提供任何割集(手动绘制或由其他工具生成或先前的运行)作为运行的输入。将这些锁定的切口分配给特定的图层类型,这些类型告诉工具必须使用这些切口,并且必须完全按照绘制的位置放置它们,而其余的切口可以在任何合法位置移动或生成,以满足所有约束并修复尽可能多的DRC违规越好。图6显示了某些DRC修复程序,这些修复程序受某些剪切限制,这些剪切被指定为“锁定”用户剪切。

图6具有用户定义的“锁定”切割的自动修复结果

处理不可修复的错误

不幸的是,尽管采用了这些巧妙的技术,但在不更改活动目标金属以及通过可能影响LVS连接性的位置上进行更改的情况下,并非所有DRC冲突都可以得到解决。图7显示了此类错误的两个示例。在这些情况下,目标形状之间的间隙非常小,以至于几乎没有或根本没有滑动切口的空间,而掉落它们会导致LVS缩短。由于不同轨道之间的这些狭窄间隙未对齐,因此切割合并也是不可行的。解决此类错误的唯一方法是返回设计实现工具并对目标金属形状进行重大电气修改。幸运的是,经验表明,这种无法解决的错误仅占设计实现错误的一小部分。

图7无法自动修复的DRC违规

使用模型流程

事实证明,该自动化工具精通解决SADP问题,但它也必须在实际的设计流程环境中可用。因此,我们的共同开发工作包括大量讨论各种使用模型流程,以及配置平台输入,输出和开关以适应这些流程的最佳方法。

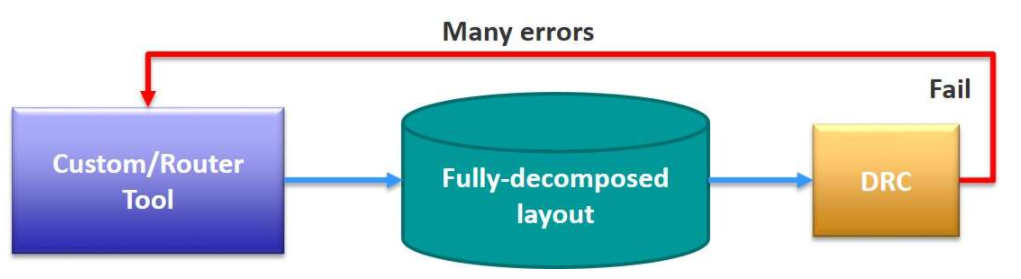

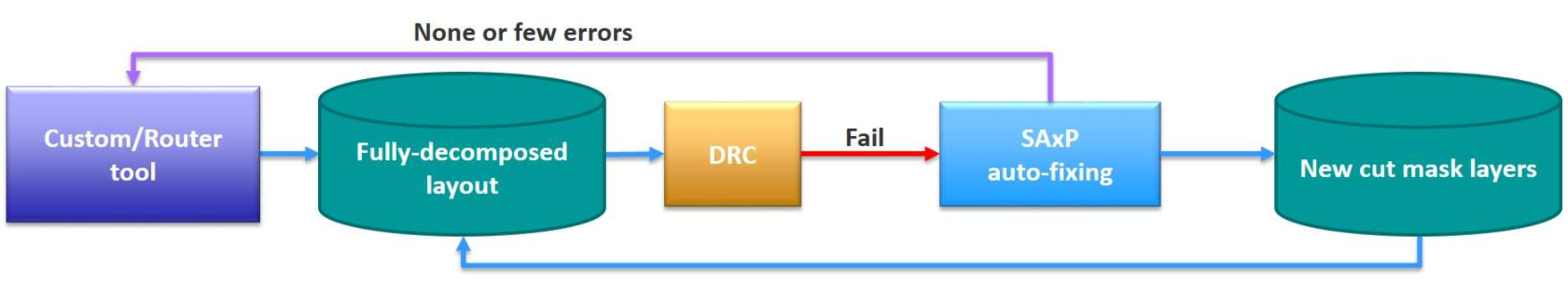

图8显示了传统的设计流程,其中布局在设计实现工具中完全分解。如果签发DRC运行发现违规,则必须在设计实现工具中手动纠正这些错误,然后重复该过程,直到DRC运行干净为止。我们的经验表明,错误计数的潜力很大,导致需要大量的人工和时间才能实现签收DRC清洁版式。

图8传统的手动修复流程用于在设计实现环境中分解的设计。

图9显示了GlobalFoundries和Mentor开发的增强解决方案。可以通过Calibre实用程序平台运行带有DRC违规的分解版面,它将自动修复大多数(如果不是全部)DRC违规,从而产生一组更新的裁切位置,这些裁切位置可以回注(替换原始裁切)到设计数据库。

图9:在设计实现环境中分解的设计的自动修复流程。

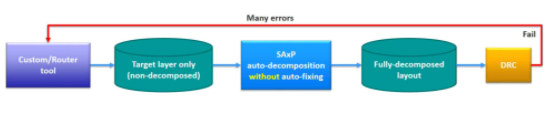

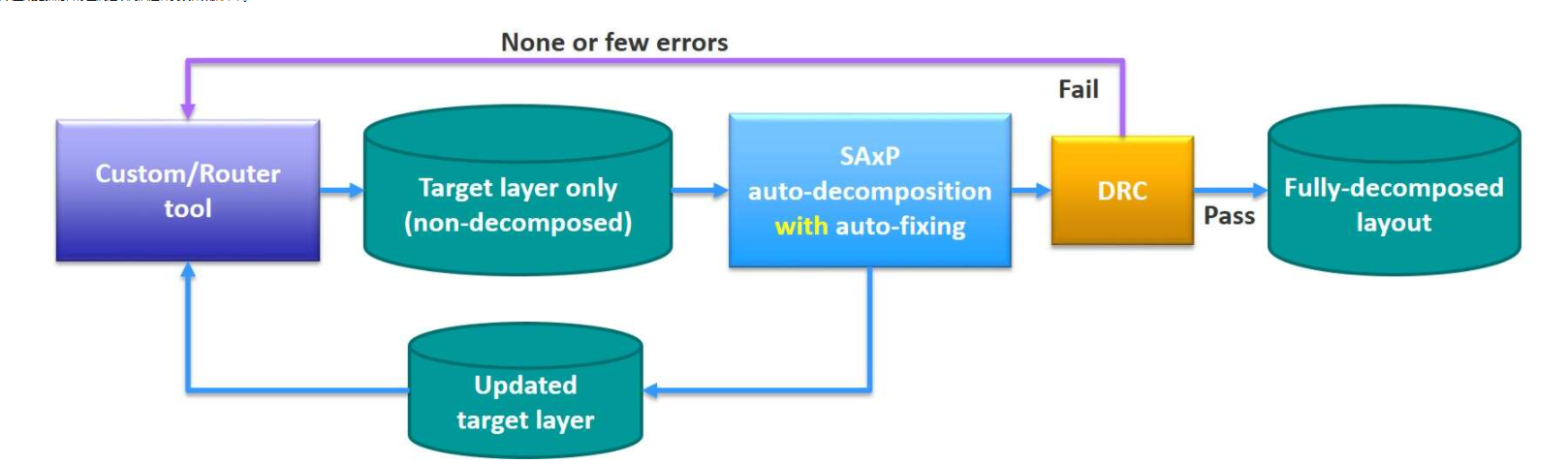

还有另一个现有的使用模型,其中未在设计实现工具内完成分解。在此流程中,Caliber实用程序平台从设计实现工具中获取目标金属,并生成构成分解后的布局的心轴,非心轴和选择性切割蒙版。然后,可以使用DRC验证这些新层,并将其批注到设计实现工具中(图10)。

图10设计的传统流程,这些流程在设计实现工具输出的后处理过程中被分解。

该流程的问题在于,传统上,分解仅限于在目标金属的每条线末端放置切口。经验表明,此限制可能导致许多DRC违规。设计人员必须调试并将这些分解错误转换为目标金属的修改,以期有望解决这些问题。同样,这可能非常耗时。图11显示了增强的解决方案,其中Calibre分解实用程序还结合了自动修复功能。这极大地减少甚至消除了DRC违规,并且可以生成更新的目标金属层以向后注释到设计数据库中。

图11:在设计实现工具输出的后处理过程中分解的设计的自动修复流程。

查找和修复SADP设计中的DRC错误是在流片之前必须完成的几种设计完成活动之一。但是,传统方法需要多个耗时的迭代,并且如果不深入了解SADP流程,对于设计工程师而言可能会面临挑战。创新的EDA工具功能可以自动应用剪切,合并和放下的组合,以修复SADP布局中现有的DRC错误,同时避免产生新的错误。IP开发人员能够自动分解填充/剪切SADP布局,或修改现有的部分或完全分解的布局,同时使用内置的签发DRC规则意识和错误可视化功能来纠正DRC错误,IP开发人员可以减少资源和资源。交付签发DRC清洁SADP设计所需的时间。

作者

- Jeanne-Tania Sucharitaves是GlobalFoundries的软件工程师,在半导体制造工艺方面拥有12年的研发经验。

- 罗伯特·亚内尔(Robert Yarnell)是GlobalFoundries的DRC工程师,致力于持续改进流程和精益生产。

- Sam Nakagawa是GlobalFoundries的副总监,负责领导先进铸造技术的设计支持的研究与开发。

- Rehab Kotb Ali是西门子业务部门Mentor的产品工程师,致力于先进的物理验证技术。

- Shetha Nolke是西门子业务部门Mentor的Calibre物理验证团队的技术营销工程师。

- David Abercrombie是西门子公司Mentor的高级物理验证方法的程序经理。

编辑:hfy

-

芯片设计

+关注

关注

15文章

1021浏览量

54911 -

eda

+关注

关注

71文章

2764浏览量

173334

发布评论请先 登录

相关推荐

如何为不同的电机选择合适的驱动芯片?纳芯微带你深入了解!

深入了解光伏逆变器测试系统

过流保护片是怎样与电池组连接的

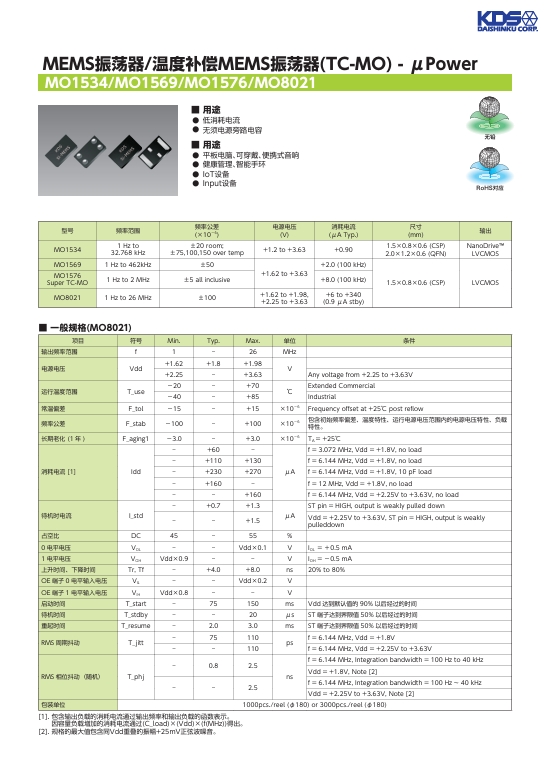

深入了解 MEMS 振荡器 温度补偿 MEMS 振荡器 TC-MO

小熊派官网正式上线 可深入了解小熊派的各款开发套件

深入了解IEEE协会:设备MAC地址申请指南

拆解FPGA芯片,带你深入了解其原理

SOLIDWORKS教育版使学生了解如何加快设计项目的速度

深入了解影响ZR执行器性能的关键因素

深入了解SADP流程加快设计到流片的速度

深入了解SADP流程加快设计到流片的速度

评论