时序就是为了维持数据信号与其参考时钟信号之间的相对位置,保证在时钟上升沿或者下降沿附近的数据能够维持稳定,这样数据就能被有效的读取。怎么让这些时序关系在系统运行中有效的实现呢?PCB设计中,是通过定义时序参数来实现的,下面就来看看这些时序参数的具体含义。

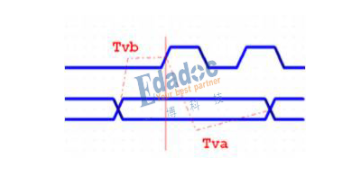

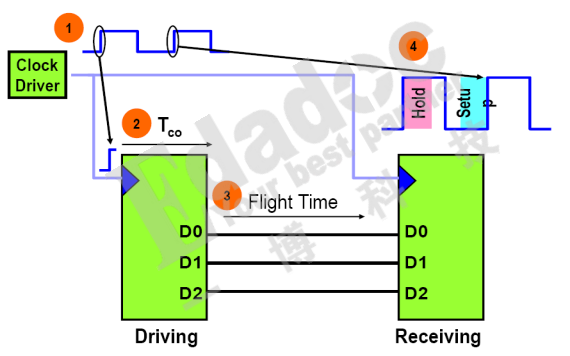

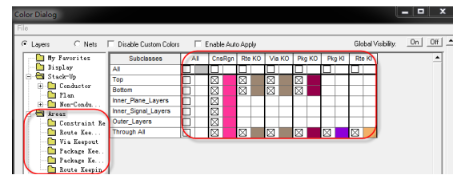

这里作者按照自己的理解把时序参数分成了三类,一类是用来描述驱动端的,一类是用来描述接收端的,还有一类是用来描述传输通道的。对于驱动端,描述它的时序参数是Tco,Tco是指时钟触发开始到有效数据输出的器件内部所有延时的总和。这个参数描述了最开始信号从芯片出来的时候,时钟与数据之间的一个位置关系。对于源同步时序,不是直接用Tco来定义的,而是使用Tvb和Tva,如下图1

图1

图1中,Tvb指的是在驱动端,时钟上升沿之前(before)数据的有效时间;Tva指的是时钟上升沿之后,数据的有效时间。这些参数在驱动芯片手册上可以查到。

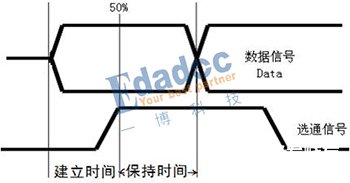

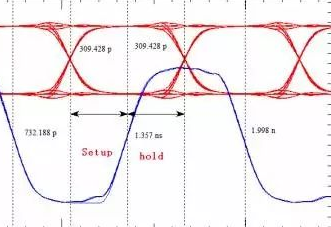

对于接收端,主要是建立时间和保持时间,这两个时序参数是时序分析中提到最多的两个参数,如下图2所示:

图2

看图2,有没有觉得和图1很相似呢,它们都是以时钟信号为参考。对于接收端来说,数据在时钟信号上升沿之前的有效时间称为建立时间,在时钟上升沿之后的叫保持时间。和驱动端对比,它们的叫法不一样罢了,定义方式都是相似的。时序分析的最终目的就是要保证数据被接收端有效的读取,所以我们在评估一个系统的时序是否满足要求,是通过评估建立时间和保持时间的裕量来实现的。

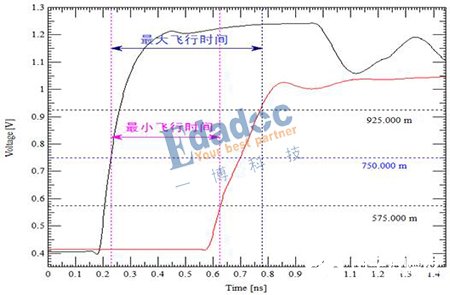

对于传输通道来说,是通过飞行时间来描述的。飞行时间包括最大飞行时间和最小飞行时间。最大最小飞行时间和传输线的长度有关,也和负载的轻重有关,负载较重会导致上升时间变缓,定义方式如下图3

在理解这些时序参数的含义之后,就可以进行时序裕量的计算了。这里以数据信号为例进行说明,我们知道,DDR总线中,数据信号是参考DQS的,在写方向:

Data信号从驱动到接收总的延时为:Tdata=Tco_data+Tflt_data (1)

DQS信号从驱动到接收总的延时为:Tstrobe=Tco_strobe+Tflt_strobe+Tdelay (2)

式中:Tco和Tflt分别代表数据、选通信号在器件的内部延迟和信号传输的飞行时间;Tdelay是指数据信号和选通信号之间的延迟,由系统内延时器件决定。建立时序裕量的公式为:Tsetup_margin=Tstrobe-Tdata-Tsetup(3)

把式(1)和式(2)带入得式(3)得:

Tsetup_margin=Tco_strobe+Tflt_strobe+Tdelay- (Tco_data+Tflt_data)-Tsetup(4)

式中:Tsetup表示接收数据端数据的建立时间,从器件手册上获取;将数据和Strobe信号在器件内的延时差异定义为Tvb,其值从器件手册上获取;

Tvb=Tco_strobe+Tdelay-Tco_data (5)将PCB走线引起的延时差异,定义为Tpcb_skew:Tpcb_skew= Tflt_data- Tflt_strobe(6)将式(5)和式(6)带入式(4),这样可以得到一个简单的建立时间裕量方程:

Tsetup_margin=Tvb-Tsetup- (Tflt_data(max)-Tflt_strobe(min))(7)

使用同样的方法分析,保持时间裕量:

Thold_margin=(Tco_strobe+Tflt_strobe+Tdelay)-(Tco_data+Tflt_data)-Thold(9)

同样定义:

Tva=Tco_strobe+Tdelay-Tco_data(10)

Tpcb_skew=Tflt_data-Tflt_strobe(11)

Thold_margin=Tva-Thold+(Tflt_data(min)-Tflt_strobe(max))(12)

综上所述,我们可以看出,对于DDR的时序来说,影响时序裕量的关键因素是驱动芯片的Tva与Tvb,以及接收端的建立时间与保持时间。我们布线可以控制的只是数据与选通时钟之间的长度差值。数据线与数据选通线长度的差值有正负之分,从(7)和(9)式可以看出,建立时间很保持时间与Tpcb_skew之间的关系,在增大建立时间的时候必然会牺牲保持时间。所以在布线的时候,数据与数据选通即DQ与同组的DQS之间应该保持严格的等长,这样可以减少Tpcb_skew,增大建立时间裕量。

时序问题是很复杂的,文中分析的情况没有考虑Jitter与串扰。我们也很少会手动计算一个系统的时序关系,一般会借助软件分析。

编辑:hfy

-

PCB设计

+关注

关注

394文章

4702浏览量

86580 -

Data

+关注

关注

0文章

63浏览量

38353

发布评论请先 登录

相关推荐

【PCB设计】PCB设计中的过孔分析

应对高速PCB设计的时序问题

PCB中TOP PASTE和TOP SOLDER的区别_PCB层的含义详解

PCB设计有哪些误区PCB设计的十大误区下部分内有上部分链接

PCB设计中的EMC/EMI问题分析

DDR布线在PCB设计中的应用解析

pcb设计中各种不同区域的设计

PCB设计中时序参数的具体含义

PCB设计中时序参数的具体含义

评论