让我们来看看等长对我们信号质量的影响。

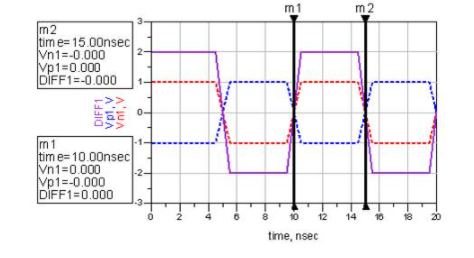

众所周知,SERDES信号都是由差分传输的,也就是说,两根信号线同时传输两个大小相等,方向相反的信号,接收端接收到的信号由两线相减得来。当两根线完全等长的时候,我们看到的波形应该是这样子的:

两次经过零轴的时间差为5ns,刚好是信号的一个UI。

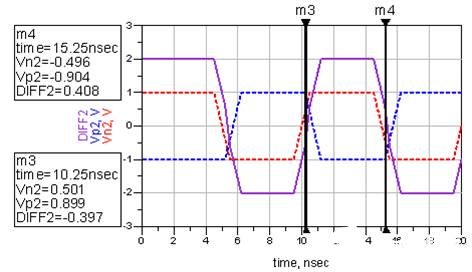

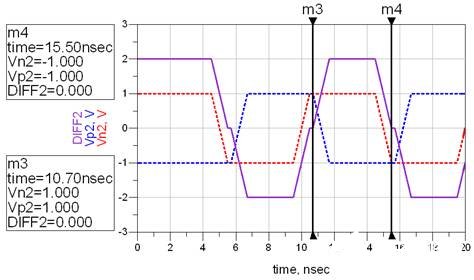

当两线不等长的时候,我们看到的波形是这个样子的:

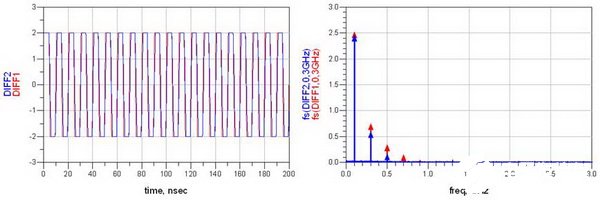

上升沿明显变缓有木有。再将两个对比看看:

图中,蓝色的是N与P不等长的信号,可以看到,当两线不等长的时候,差分信号的能量明显变弱了,那多的能量去哪里了呢?

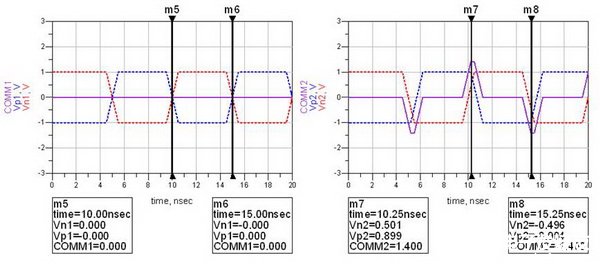

差分对之中除了差模能量之外还有共模能量,差模是N与P之间相减,共模是N与P之间相加。能量总是守恒的,多的能量变成了共模能量继续存在,图片:

如果两线的长度相差再大一些,我们接收端接收到的信号将会变成这样:

可以看到,两次经过零轴的时间由之前的5ns变成了4.8ns。或者说,N与P的长度差,引起了0.04UI的抖动。这时候,串行的Clock recovery该花点心思才能将其时钟解出来了。而且在进行时钟与数据对位的时候,是对在0V这个阶梯的左边还是对在右边呢?这又会引起时序问题的出现。

编辑:hfy

-

波形

+关注

关注

3文章

379浏览量

31537 -

SerDes

+关注

关注

6文章

198浏览量

34899 -

等长

+关注

关注

0文章

4浏览量

7541

发布评论请先 登录

相关推荐

Altium designer 等长布线

一个等时不等长的DDR

Altium Designer如何绕等长线

用allegro使二条时钟线等长的设计置

等长对我们信号质量有什么影响?

等长对我们信号质量有什么影响?

评论