在半导体领域,单个模块中的器件工作频率和晶体管数量随时间增加。在本文中,我们将介绍可以在ASIC的物理设计实现中使用的广为人知的低功耗实现技术。CMOS器件有三大功率损耗:动态功率,静态功率和短路功率。

CMOS器件的总功耗如下:

CMOS器件具有非常低的静态功耗,当所有输入均处于某个有效逻辑电平且该器件未进行开关操作时,就会发生这种情况。

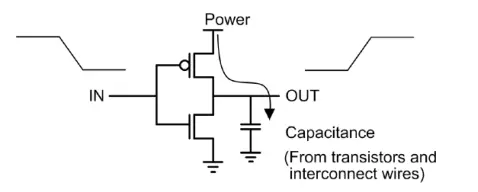

静态功耗是电源电压,晶体管阈值电压和晶体管尺寸的函数。当以更高的频率工作时,动态功耗会极大地影响总体功耗,并由下式得出:

在哪里,

C负载= CMOS的负载电容

VDD =电源电压

F =发生过渡的工作频率

a =开关活动常数

从等式(2),我们可以得出结论,动态功耗与器件的工作频率和电源电压成正比。

现在,第一个组件是设计的频率,但是由于数字设备的速度越来越快,我们无法降低工作频率。因此,我们需要使用时钟网络以节省功耗。为了节省时钟树的功率,设计人员使用了时钟门控技术,其中在时钟门控单元上施加了特殊的使能信号,以打开指定触发器组的时钟,这有助于降低动态功耗。

节省功率的第二个要素是芯片的电源电压。有多种技术可借助电源电压来节省功率。

- 多VDD

- 跨域的杠杆移位器插入

- DVFS(动态电压频率缩放)

- 多Vt

- 电源门控(电源关闭)

让我们详细讨论用电源电压节省功率的实现技术。

1)多VDD

多VDD技术用于节省设计的动态和静态功耗。在此,芯片以不同的电源电压实现。不同的功能块以不同的电源电压运行。我们可以通过减少设计的标准单元和存储元件的电源电压来节省功耗。

在多VDD技术中,根据设计的关键程度定义了不同的电源域。这里,电平转换器用于从低压电源域到高压电源域的信号,反之亦然。在网表级别,将以UPF和CPF电源格式编写设计代码,在此基础上,我们可以开发设计的电源结构。

2)跨域的电平转换器插入

在多VDD设计中,使用了电平转换器。电平转换器是一种数字组件,用于将信号从一个转换为另一电压电平(从低电压电平转换为高电压电平,反之亦然)。

对于在设计中的不同电源域之间插入电平转换器,有一些特殊的放置准则。电平转换器应放置在设计的目标域中。插入电平转换器的一个缺点是-它占用了设计空间。但是,与此同时,插入电平转换器将有助于节省芯片的功耗。

有两种类型的电平转换器。

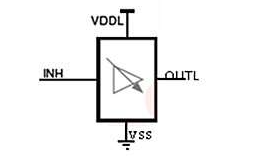

高至低电压电平转换器

它仅引入缓冲延迟,因此对时序的影响最小。下图显示了从高到低的电平转换器。

图1从高到低的电平转换器

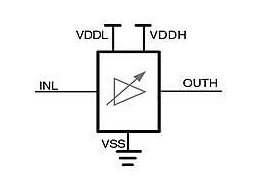

低至高电压电平转换器

低压摆幅输入信号不一定足够强,无法完全导通输入晶体管。这可能导致不可接受的长时间上升或下降时间。这可能会导致更高的开关电流并降低噪声容限。下图显示了从低到高的电平转换器。

图2从低到高的电平转换器。

在放置阶段,从低到高电压电平转换器需要特别注意。

3)DVFS(动态电压和频率缩放)

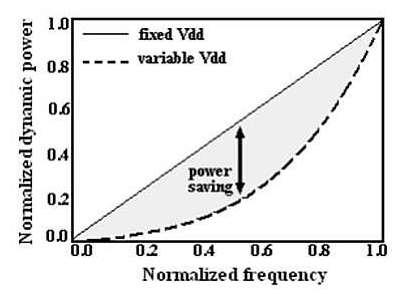

在DVFS技术中,工作电压以及频率会根据设计的不同工作模式动态变化。通过随频率改变电压,我们可以降低功耗。当需要高工作速度时,增加电源电压以获得更高的工作频率,而功耗增加。

动态电压和频率缩放是广泛用于各种计算系统,微处理器等的功耗和能耗降低技术。降低电源电压可以降低功耗,因为电源和电源电压之间存在二次关系。由于此技术同时优化了电压和频率,因此对于静态和动态功耗非常有效。下图显示了通过使用可变电源电压实现的节能效果。

图3通过使用可变电源电压可实现节电

4)多Vt

该技术涉及使用多阈值电压标准单元库来实现设计,以节省设计功耗。库以彼此独立的标准Vt,低Vt和高Vt形式提供。这些库用于功率和时序优化。

物理设计流程中的布线完成后,可以通过在非时序关键路径中进行Vt交换来实现功率恢复,方法是在签约阶段的黄金时段将低Vt单元转换为高阈值电压单元。

近来,多Vt合成流在较低技术节点中变得更加普遍。在ASIC设计流程中,主要的标准Vt库用于初始合成。多个阈值单元用于优化和合成的下一个迭代。

5)电源门控(电源关闭)

通过施加特定信号在特定时间间隔内关闭模块/模块,可以降低CMOS电路的内部泄漏功率。可以通过使用可插入网表的电源门控技术来节省功耗。

在这种技术中,当功能未激活时,这些块被置于关闭模式,并在需要时打开。通过在单元(功率门控器)上施加一些特殊信号(上拉或下拉),可以控制系统逻辑功能的启用和禁用。这些特殊单元(门控)的添加会占用更多的区域。

这些选通器也称为睡眠晶体管,它们用作开关,以切断部分设计的电源并将永久电源连接到电路电源。PMOS睡眠晶体管用作VDD电源的“页眉开关”,而NMOS睡眠晶体管控制VSS电源,称为“页脚开关”。

可以采用两种不同的方式来实现电源关闭(PSO):片上电源关闭和片外电源关闭。电源开关位于片上PSO的SoC中;电源开关在片外PSO中位于芯片外部。

PSO同样可以是精细或粗略的门控,指的是受单个电源开关约束的每个模块的大小。通过精细的电源门控程序,我们可以通过关闭单个模块来节省电源,而无需切断继续工作的不同模块的电源。这将有助于降低CMOS的泄漏功率。利用粗粒度技术,单个睡眠信号可以使整个区域断电。这有助于减少待机模式下的泄漏功率。

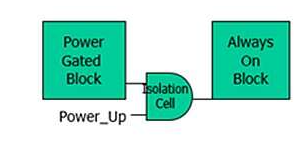

我们需要一个隔离单元来隔离来自功率门控模块的信号,如下图4所示。

图4电源门控块信号需要一个隔离单元

该隔离单元始终是“加电”单元,它可以防止任何未知的逻辑电平到达“始终在线”逻辑。

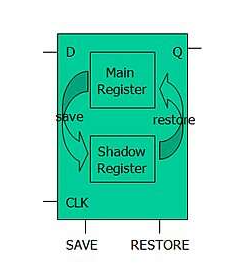

在进行电源门控时,在关闭电源门控模块之前,还需要一个保留寄存器以保存其内容。如下图5所示,保留寄存器除主寄存器外还包含一个影子寄存器。影子寄存器由“常开”电源供电,当“ SAVE”置为高电平时,该电源存储被电源门控的模块的逻辑值。当“ RESTORE”置为高电平时,它将将此逻辑值恢复到主寄存器。

图5保留寄存器包含一个影子寄存器和主寄存器

在本文中,已经讨论了各种低功耗实现技术。采用特定技术取决于设计复杂度和要降低的功耗。在采用它们之前,还需要考虑上述每种技术的时序损失,面积损失和实现复杂性。

通常,多VDD和DVFS技术用于降低动态和静态功耗,而多Vt和电源门控技术主要用于降低泄漏功率。

参考

- 许,《面向编译器的动态电压和频率调节,以降低CPU功耗和能耗》,博士学位,美国新泽西州立大学,2003年

- Diary R. Suleiman,Muhammed A. Ibrahim,Ibrahim I. Hamarash,动态电压频率缩放(DVFS),用于降低微处理器的功耗和能耗

- 低功耗方法论手册学习

Vipulkumar Patel是eInfochips的高级物理设计工程师,在VLSI / ASIC领域拥有7年的经验。

Rakesh Gosai是eInfochips的高级物理设计工程师,在不同纳米技术节点(7 nm,16nm)的ASIC领域拥有4年的经验。

-

CMOS

+关注

关注

58文章

5790浏览量

236603 -

asic

+关注

关注

34文章

1209浏览量

121108 -

电平转换器

+关注

关注

1文章

197浏览量

19695 -

电源电压

+关注

关注

2文章

993浏览量

24249 -

UPF

+关注

关注

0文章

50浏览量

13622

发布评论请先 登录

相关推荐

低功耗处理器的优势分析

如何实现EEPROM的低功耗模式

低功耗模组短信通:短消息发送实例解析

国产化低功耗窄带物联网无线通讯方案_ZETA技术

一款4644芯片低功耗设计思路解析

CPU的低功耗与高功耗的区别

国产蓝牙模组 | 低功耗蓝牙应用

CS32F03X低功耗Deepsleep应用配置

上拉电阻如何实现低功耗设计

OTP低功耗语音芯片的工作原理与产品特性

深入探究LoRa MESH组网技术:构建远距离、低功耗的物联网通信网络

在ASIC的物理设计的低功耗实现技术解析

在ASIC的物理设计的低功耗实现技术解析

评论