在这个围殴开篇的时候征集了大伙的一些问题及最感兴趣的话题,其中最多的是T型拓扑和Fly_by拓扑的应用,那么这一篇就让我们了解拓扑和端接方式吧,同时也将开篇时大家的一些其他问题争取在终结篇给大家答复。

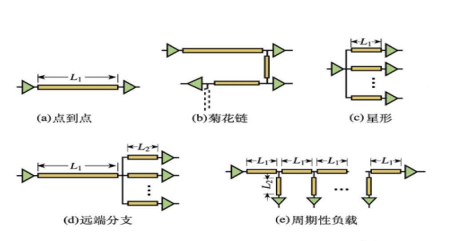

首先,简单总结下各拓扑的应用场合问题。点对点拓扑主要用在时钟及比较单一的芯片连接上,这个谁都会,就两个芯片,当然必须点对点啊!同时与点对点搭配最多的就是源端串联端接,当然也有其他的并联端接。那么点对点拓扑可不可以不用外部端接?当然是有的,如DDR3的数据信号就可以不用外部端接,因为它有ODT(片内端接)。还有一些可调驱动的电路,其他的就比较少了。如果不想加外部端接又要保证系统足够稳定怎么办呢?高速先生的回答是:仿真,仿真,仿真(重要的事情说三遍哈)!另外还有一些经验可以供大家参考,那就是将线路阻抗做小(源端匹配的考虑,一般芯片驱动内阻都是低于50欧姆的)!点对多点拓扑就稍微复杂点,主要看信号速率以及负载数目了。超过100MHz的多负载拓扑及端接方案建议先仿真,一两句话也说不清楚,具体问题具体分析吧。

其次,不同的端接方式有不同的考虑点。

末端并联端接也用的比较多,如前文提到的T点及Fly_by拓扑,其中上拉比较常见,端接电阻通常和传输线阻抗一致,但也有例外,如负载较多的情况下这个阻值还会根据信号质量有一些变化,具体多少最好是通过仿真来确定,最后可以通过测试来验证。

戴维南端接的效果其实和末端上拉是一样的,在早期的DDR2设计上见得比较多,就相当于上下拉端接。好处是不需要额外转Vtt电路,一个电阻接到Vcc,一个电阻接到地,并联之后的效果相当于一个电阻上拉到Vtt。不好的地方就是需要2个电阻,功耗较大,对布线空间本来就很稀缺的设计来说不怎么好实现。通常来说这两个并联电阻的阻值是一样的,如100ohm,这样并联后的等效电阻为50ohm,和我们大部分的传输线阻抗一致,这个在DDR2的设计里面经常是这样配置的。当然还有一些其他的电阻组合,如一些非DDR2的情况,有见过80//120组合的,不管怎么组合,通常的原则是并联后的有效阻抗保持和传输线阻抗一致,另外还取决于两个电阻中间需要的电平的值(分压的原则)。

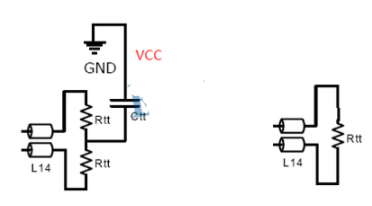

最后来看看AC端接,其实如果有经常做DDRx设计的朋友们对这个端接也是非常熟悉的,如我们的DDRx时钟信号,有时我们使用100欧姆并联电阻端接,有时我们就使用AC端接,两端分别接个电阻再到电容,然后再到Vcc或者地,这个就是我们说的AC端接,如下图所示。

编辑:hfy

-

拓扑

+关注

关注

4文章

341浏览量

29590 -

DDR2

+关注

关注

1文章

100浏览量

41554 -

并联电阻

+关注

关注

1文章

47浏览量

13499

发布评论请先 登录

相关推荐

DDR3采用fly-by拓扑为什么有的采用RTT上拉端接,而有的采用RC下拉端接?

如何选择端接方式

端接的方式和规则

高速PCB的终端端接方式浅析

端接与拓扑竟有这些区别,电子小白收好了!

围绕拓扑结构与端接展开,浅谈对fly-by结构

常用的五种端接方式资料下载

浅谈拓扑和不同端接方式

浅谈拓扑和不同端接方式

评论