十多年来,宽带卫星有效载荷通信系统都是使用数据转换器构建的,这些数据转换器使用低压差分信号(LVDS)数据接口连接到现场可编程门阵列(FPGA)或专用集成电路(ASIC)。在该时间段内,这种组合能够跟上不断扩展的采样率和相应的采样带宽,但是当数据转换器的采样率达到每个转换器每秒约1.6 G采样(SPS)时,达到了上限。新的JESD204B芯片间数据接口标准现在正在获得芯片支持,以实现更高的突破。

设计人员面临的问题是,使用LVDS连接1.6 GSPS的12位数据需要一个具有12条LVDS数据线的800MHz双数据速率(DDR)接口-在很大程度上被认为是可靠关闭LVDS时序的实际上限。与FPGA的接口。在大多数情况下,需要使用模数转换器(ADC)和FPGA之间的两条800-MSPS总线(400-MHz DDR)进行2路解复用的数据流,以放宽时序要求。该方案的代价是通道数和板布线面积的两倍。它还需要紧密匹配电路板布线中所有差分对的布局,这会导致效率低下和过大的电路板布局。节省板载空间对于空间有效载荷非常重要,因为在这种空间有效载荷下每盎司的发射成本很高,而且每平方毫米的板载空间都具有很高的价值。

同时,数据转换器的核心速度现在已经超过LVDS接口速率的能力,并且商业数据转换器行业已很大程度上转向联合电子设备工程委员会JESD204B串行接口标准。为了使有效载荷射频(RF)收发器的带宽增加到LVDS无法承受的范围,航天工业组件制造商将需要使用这种新的标准接口。

什么是JESD204B?

JESD204B使用8位/ 10位编码数据接口在差分通道上将数据芯片串行化。由于书面JESD204B规范的上限是12.5 Gbps的通道速率,因此可以突破宽带通信设计人员正在寻找的信号带宽的下一个水平,而这超出了LVDS。设计人员可以使用该通道速率将许多转换器聚合到一个通道中,也可以采用多通道配置来从一个数据转换器向FPGA传输数据或从FPGA传输大量数据。

由于JESD204B在链路对之间不需要匹配的走线长度,因此设计人员可以优化电路板布线以节省电路板空间,并避免LVDS通常需要的额外布线,以使最短的直线走线与最长的路径匹配。JESD204B规范具有内置的弹性缓冲,以适应走线长度的变化。对于需要同步接收器的系统,JESD204B允许使用一种简单的方法来使用分布式低频SYSREF信号来实现多设备同步。

完善JESD204B生态系统

现在,主要的数据转换器供应商提供了许多使用JESD204B标准的目录(非空间级)产品,并且目录FPGA供应商已经产生了JESD204B知识产权,以保持(并在大多数情况下超过)当前数据的速度能力。转换器。不幸的是,空间级FPGA的SerDes输入/输出(I / O)速度受到限制,由于整个系统带宽无法改善所提供的LVDS,因此减慢了空间应用中从LVDS到JESD204B的过渡。Microchip RTG4和Xilinx Virtex-5QV系列空间级FPGA都具有SerDes最高的加速能力,到现在为止还不到5 Gbps。

如果业界试图在空间级组件中使用LVDS来超越1.6 GSPS,那么它将需要在数据转换器与FPGA之间使用100多对匹配长度的差分连接。但是现在,有了JESD204B,诸如德州仪器(TI)ADC12DJ3200QML-SP之类的设备的数据量ADC仅使用8个差分连接就可以推入已达到6.4 GSPS的状态。该器件通过运行八个JESD204B SerDes通道,每个通道以12.8 Gbps的速度实现6.4 GSPS的12位数据输出。现在可以想象,通过扩展到更多的差分连接,加速链接或两者兼而有之,可以继续提高空间应用程序的数据转换器采样率。这将使通过RF链路往返于卫星的信号带宽和数据速率大大增加。

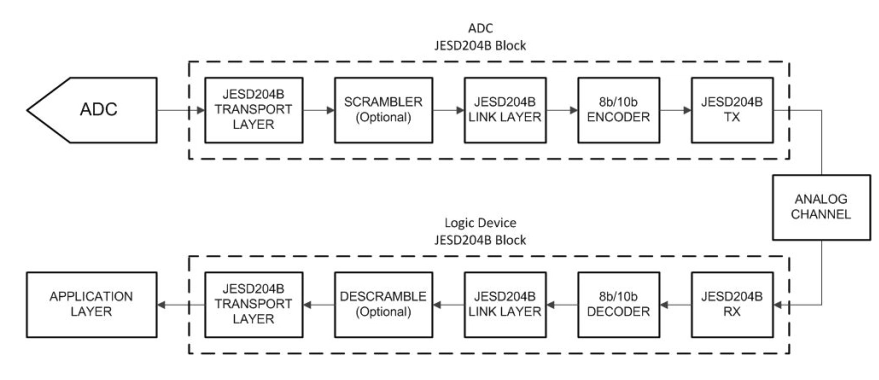

图1显示了标准下SerDes处理的示例。模拟通道代表设备之间板卡的高速数字数据信号。之所以在此处将其称为模拟通道,是因为在板设计中以及用于阻抗匹配时,将12.8 Gbps SerDes链路视为模拟或RF信号。如果没有给予此链接注意,则接收端的眼图将不会张开并对齐以进行正确捕获。JESD204B发送器是串行化后ADC的输出数据,而JESD204B接收器是需要反序列化的FPGA输入(在图1中标记为“逻辑设备”)。

图1此简化的JESD204B接口图显示了从ADC到FPGA的数字链路作为模拟通道,以反映需要将电路板视为信号的电路板布局的需求。

但是,将空间应用中的数据通信转移到JESD204B不仅需要空间级数据转换器,还需要空间级FPGA,它们可以与它们一起工作以提供更高级别的信号带宽。这些设备必须继续提供太空任务所需的闭锁和总电离剂量(TID)功能。

幸运的是,此类设备将很快面市。为了支持完整的JESD204B生态系统,多家FPGA供应商宣布将发布具有更高SerDes速度并支持JESD204B的太空级FPGA。例如,赛灵思(Xilinx)宣布,它将把32种SerDes收发器支持12.5 Gbps的通道速率,将Kintex UltraScale类的FPGA版本过渡到XQRKU060中的空间级。图2是连接到Alpha数据板的ADC12DJ3200QML-SP板的图片,该板包含用于12.5 Gbps JESD204B互操作性测试的Xilinx XQRKU060。

图2连接到Alpha数据空间开发套件(绿色)的ADC12DJ3200EVMCVAL(红色)表明,设计人员可以使用JESD204B的空间级组件。

其他厂商也在效仿。NanoXplore宣布将提供一种太空级FPGA,其NG-LARGE中具有6.25 Gbps SerDes,而NG-ULTRA中具有12.5Gbps SerDes。Microchip宣布将在其太空级RT PolarFire FPGA的变体中支持24个10 Gbps的SerDes收发器。

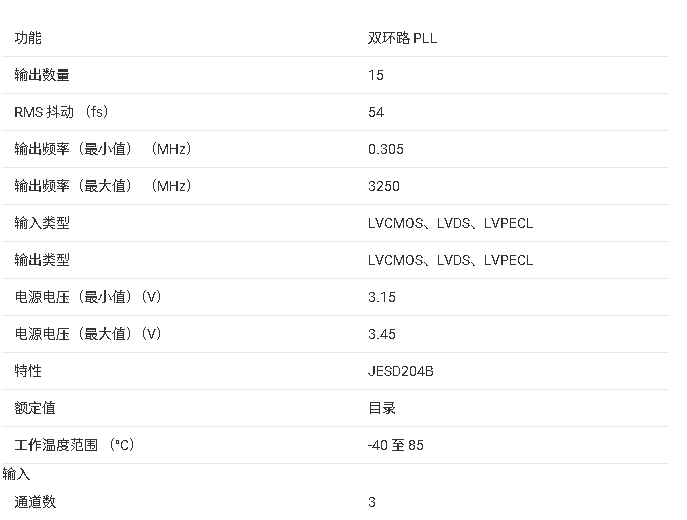

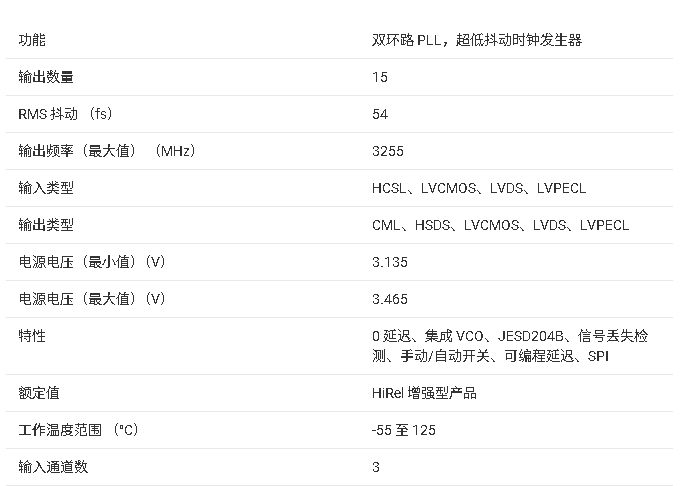

如果没有合适的时钟解决方案将所有组件同步连接在一起,FPGA-ADC系统将无法工作。现在,诸如太空级时钟芯片德州仪器(TI)LMX2615-SP之类的设备可以提供高达15 GHz时钟频率的此功能。

JESD204B辐射特性

有效载荷设计人员在遇到重离子时需要了解使用JESD204B的设备的特性。尽管概率很小,但是串行链接可能会因轨道上的重离子撞击而中断。德州仪器(TI)在2019年核与空间辐射效应会议上发布了JESD204B接口的首个单事件效应表征。ADC12DJ3200QML-SP的结果摘要是:

串行链接始终会在重离子撞击后自动自我恢复。

串行链路的平均恢复时间为1.3 µs,最坏情况下的测量值为11 µs。

但是请记住,这些只是一个示例设备的结果。每个集成电路将具有不同的结果,因此将需要对光束进行仔细的表征,以便根据组件选择,屏蔽环境和工作轨道来确定总体误码率。如果重离子干扰链路,则必须采用具有JESD204B兼容规范的接收器并进行适当的错误处理,以实现快速恢复。

现在已经有了支持空间级组件中的JESD204B接口的数据转换器,FPGA和时钟设备,现在已经建立了一个生态系统,可以在空间中应用该标准。设计人员现在可以开始处理宽带卫星通信和雷达有效载荷中的下一代系统带宽。

菲利普·普拉特(Philip Pratt)是达拉斯德州仪器(TI)面向全球航空航天和国防应用客户的高速数据转换器团队的营销主管。

编辑:hfy

-

FPGA

+关注

关注

1664文章

22537浏览量

640181 -

串行接口

+关注

关注

3文章

524浏览量

45344 -

lvds

+关注

关注

2文章

1245浏览量

70311 -

数据转换器

+关注

关注

1文章

402浏览量

30789 -

JESD204B

+关注

关注

6文章

86浏览量

19969

发布评论请先 登录

AD9083:16通道、125 MHz带宽JESD204B模数转换器的全方位解析

AD9094:8位、1 GSPS、JESD204B四通道ADC的深度解析

AD9528:高性能JESD204B/JESD204C时钟发生器的深度解析

技术文章|高速DAC JESD204接口接收机物理层压力测试(下)

技术文章|高速DAC JESD204接口接收机物理层压力测试(上)

LMK04828 超低噪声JESD204B兼容时钟抖动清除器技术手册

LMK0482x系列超低噪声JESD204B兼容时钟抖动清除器技术文档总结

LMK04616 超低噪声低功耗JESD204B兼容时钟抖动清除器总结

LMK04828-EP 超低噪声JESD204B兼容时钟抖动清除器总结

LMK04832 超低噪声、3.2 GHz、15 输出、JESD204B 时钟抖动清除器技术手册

LMK04368-EP 超低噪声JESD204B/C双环路时钟抖动清除器总结

关于航天工业组件的JESD204B标准快速数据接口

关于航天工业组件的JESD204B标准快速数据接口

评论