关于大家担心的回流路径上的电流交叠在一起是否会有影响,在之前的《回流是如何影响信号的》文章中有过详细的说明。这篇文章就来看看串扰本身的问题。

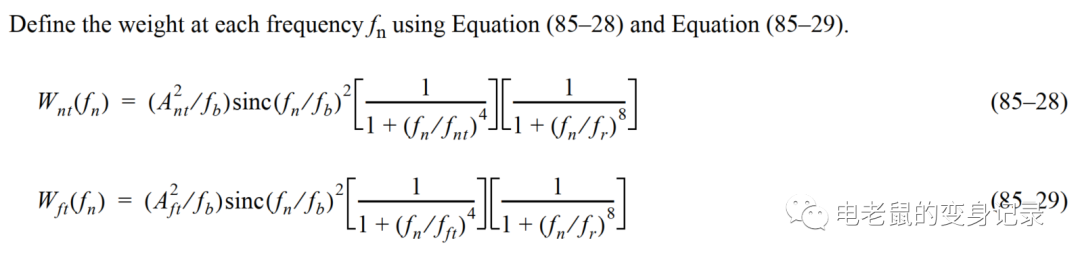

串扰是电磁场的耦合,而信号传输时信号路径与回流路径之间的电磁场并不是辐射场,理想导体中也没有磁场的存在,电磁场在回流平面就到此为止了。如图1中的结构,地平面上深深的蓝色,以及下方地平面中空空如也的白色,也可以看出实际上并无电磁场的穿过:

图1

对图2中这样的结构进行仿真:

图2

测试结果如图3:

图3

一个4端口的S参数,应该有16条曲线才对,而在图中只能看到8条,缺少的那8条线正是串扰指标,由于小于-40dB被隐藏了。而实际上同样的结构也有经过测试验证,测试出来的串扰值大约为-70dB~-80dB,这其实就是仪器的底噪。

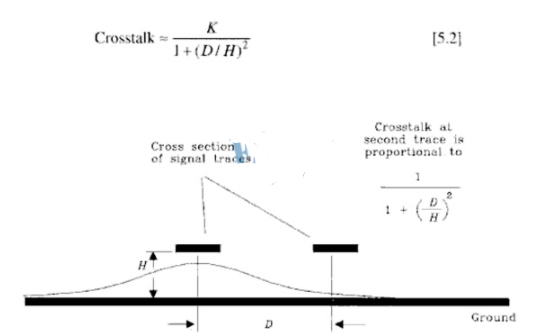

那是不是隔层串扰就完全可以忽略了呢?其实也不是这样的,实际的设计平面通常并不是完整的,会有许多孔将平面给打穿,尤其是在BGA,以及连接器处,那实际上平面两边的走线就如同下面这样的结构。图4中两线距离金属平面都为10mil,中心间距为22.4mil,线宽约为9mil。

图4

该结构的实际测试结果如图5:

图5

这样的一个串扰大小就不能完全忽略了。相当于同层之间中心间距为24mil(2.4H)的串扰大小,如图6:

图6

这样的一个结果,符合我们通常觉得的中心间距相等,串扰大小接近的印象。看来隔层之间,尤其是连接器和BGA位置的串扰是不可忽略需要引起重视的啊。

该测试的层叠如图7:

图7

各层之间的间距都为10mil,所有信号层之间都有地隔开,与我们通常做的背板设计比较相似。

编辑:hfy

-

BGA

+关注

关注

5文章

588浏览量

52027 -

串扰

+关注

关注

4文章

196浏览量

27888 -

S参数

+关注

关注

2文章

148浏览量

47950 -

电磁场

+关注

关注

0文章

806浏览量

49580 -

信号传输

+关注

关注

4文章

502浏览量

21180

发布评论请先 登录

一文解析串扰技术问题

一文解析串扰技术问题

评论