Vref偏移对DDR会造成什么影响,其中有比较重要的一个点就是会影响setuptime和holdtime,这两个参数和Vref又有什么关系呢,还有JEDEC中讲的derating又是什么东西呢?

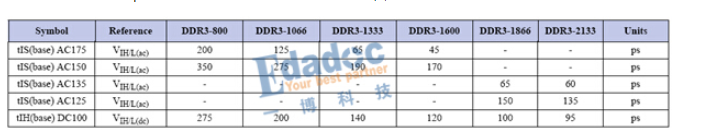

setuptime和holdtime对我们判断时序裕量是一个比较关键的数值。一般JEDEC里面会对于setuptime和holdtime做比较详细的描述,如下图所示,

从上图中,我们可以看到几个比较关键的点,为什么是tIS(base)和tIH(base),还有标题中指明for 1V/ns,又指代的什么意思?为什么tIS参考的是VIH/L(ac),而tIH参考的是VIH/L(dc)呢,AC和DC的区别又是什么?一个小小的参数表格,包含的意义却涉及很多内容。

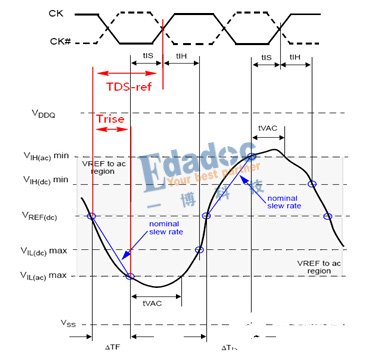

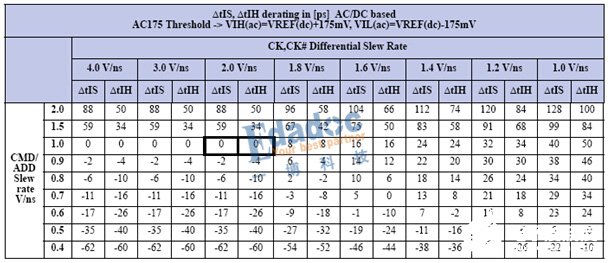

首先,我们计算建立时间的margin的时候,都是由UI/2-建立时间,实际上此时的建立时间是tIS(total setup time)= tIS(base)+derating, derating是对建立保持时间基准值的修正。对于tIS的定义,为什么会需要用到derating这个参数呢,这实际和规范中tIS(base)的定义方式相关。如下图所示,建立时间等于TDS-ref(在ref处的建立时间)减去Trise(Vref到VIH AC的时间)。规范中的基准值是预减去了这个Trise的,这个预减去的值是特定slew rate为1V/ns时的值,若判断门限是AC175,则预减去175ps。当slew rate等于1V/ns时,derating为0,不需要调整;当slew rate大于1V/ns(更快)时,从Vref到Vih(ac)所需的时间就少,预减多了,要补回来,所以取值为正;当slew rate小于1V/ns(更慢)时就预减少了,所以取值为负。

至于建立时间和保持时间的参考电压值不一致,主要是因为AC和DC的代表的意义不一样,AC指由高低电平跳变时需要的参考电压,DC则指保持所在电平时的阈值电压, tIS是以数据从前一状态变化为当前状态的时刻开始算起,对应于状态变化过程,要确保电平已变化到规定电平,所以以更为严格的AC参数作为参考;tIH描述的是数据从稳定到状态转换的时间,对应于电平稳定的过程,而电平一旦建立后,发生状态转换的门限电压值是参考DC,所以tIH也以DC参数作为参考。

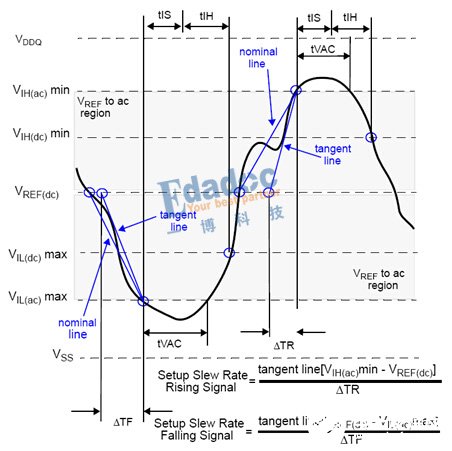

信号的波形很多情况都是不完美的,也许有回沟,也许会有台阶,如下图所示,这种情况下,skew rate就不能用下图所示的nominal line,而应该选取tangent line。

编辑:hfy

-

DDR

+关注

关注

11文章

717浏览量

65655 -

波形

+关注

关注

3文章

381浏览量

31703 -

JEDEC

+关注

关注

1文章

36浏览量

17493 -

IVREF

+关注

关注

0文章

5浏览量

1446

发布评论请先 登录

相关推荐

INA849仿真输出电平不在VREF的静默电平,有近1V的偏移,是什么原因引起的?

DDR2设计原理 DDR2 design

无法设置属性VREF

怎么将FPGA vref引脚连接到DDR参考电压

OMAPL138 DDR2读数据偏移2个字节

金士顿:DDR2/DDR3价格可能会继续上涨

DDR4伪漏极开路驱动器及对接收器的功耗和Vref电平而言的意义

75uV输入偏移电压会影响您的电路吗?

内置VREF的灌电流/拉电流抗辐射加固型3A DDR终端稳压器TPS7H3301-SP数据表

内置VREF的灌电流/拉电流抗辐射加固型3A DDR终端稳压器TPS7H3301-SP数据表

Vref偏移对DDR会造成什么影响?

Vref偏移对DDR会造成什么影响?

评论