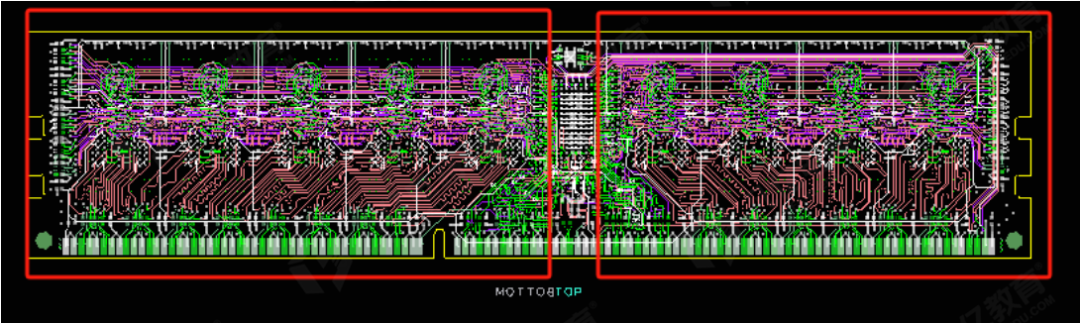

通常,DDR设计完成之后 ,对信号质量并没有一个完全确定的概念,需要我们通过仿真和测试的手段去判断和验证。而此时,往往我们拿到的就是一个波形,测试波形或者仿真波形,该如何去判断其信号质量,参照的标准又是怎样的,就是我们需要去考虑的重点。

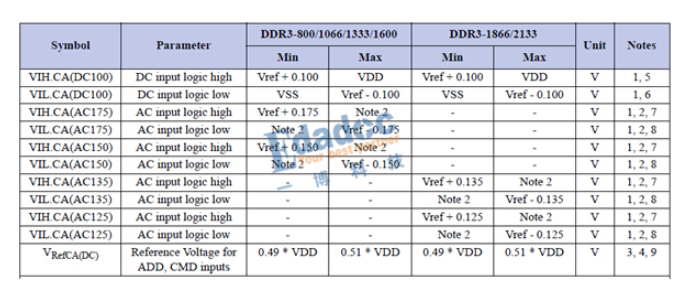

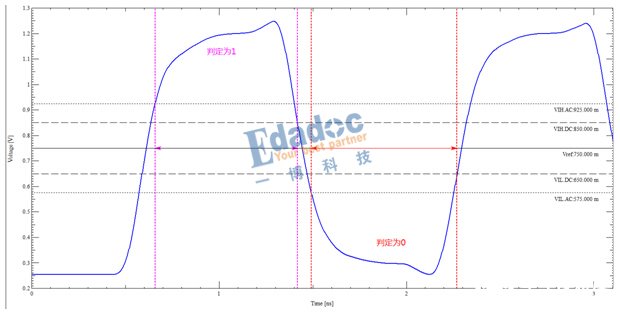

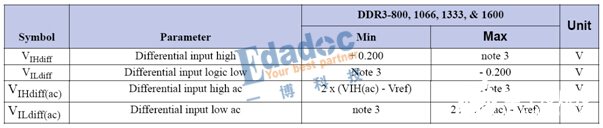

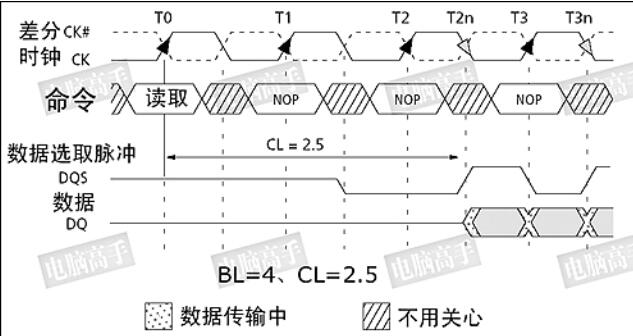

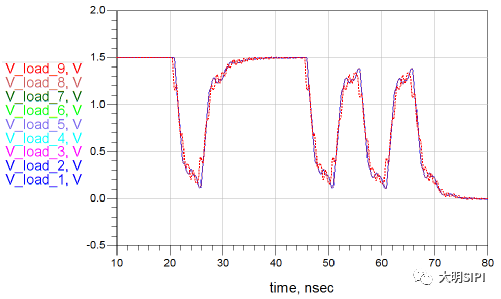

DDR信号是数字信号,表现为0、1两种形式,一般看到的波形都是类似于正弦波的样式,什么时候判定为1,什么时候判定为0呢?每一个信号都是以电磁波的形式进行传输,因此一定具有相应的幅值,所以判定方法肯定是当幅值高于某一个值时,判定信号为1,低于某一个值时,判定为0。而判定的依据——某一个值就是可以从JEDEC中找到的。如图一所示,是DDR3地址命令信号的AC、DC标准,对应相应的速率,就可以在波形上面标注出相应的VIH和VIL。当幅值范围为VIHAC(min)~VIHDC(min)时,判定为1,当幅值范围为VILAC(max)~VILDC(max)时判定为0,如下图二所示

图一

图二

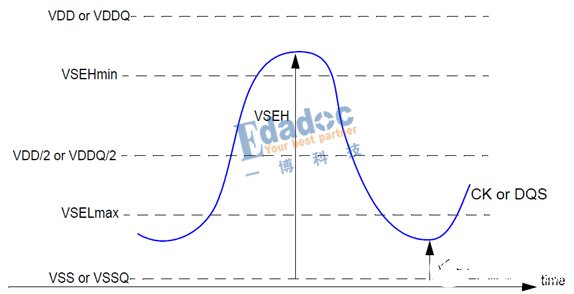

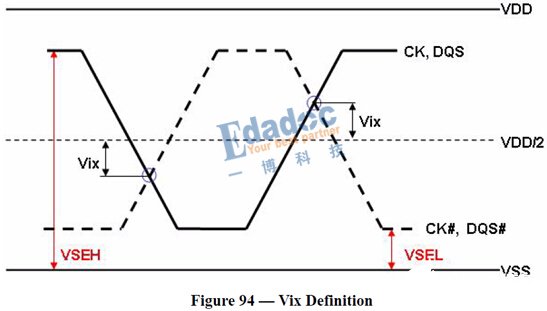

对于做为差分线的CK信号和DQS信号而言,判定的要求又分为单根和差分模式,单根模式的判定标准和地址数据线基本一致,如下图三所示。它的判定标准只有VSEH和VSEL。实际这两个值对应的就是VIH.AC和VIL.AC。

图三

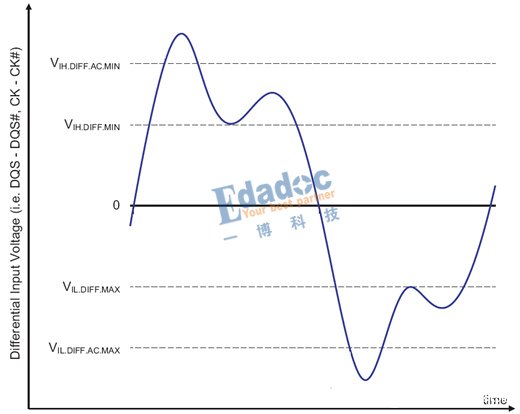

差分模式如图四所示,数据见表格。

图四

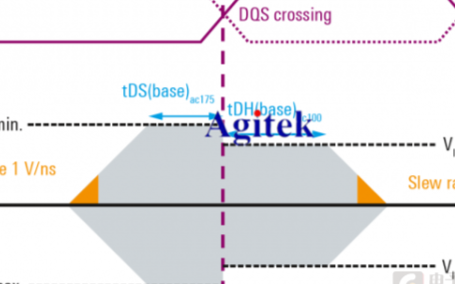

而且同时对两个单根的交点也有一定的要求,如下图五所示,两个单根的交点位置要在VSEH和VSEL之间,否则的话差分模式下,正半周期和负半周期可能会有比较大的一个比例差异。

图五

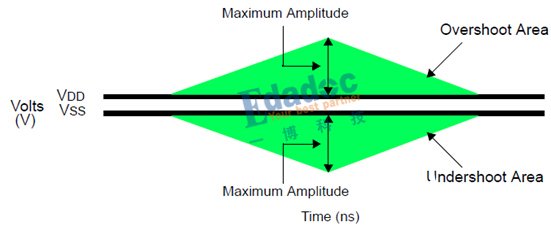

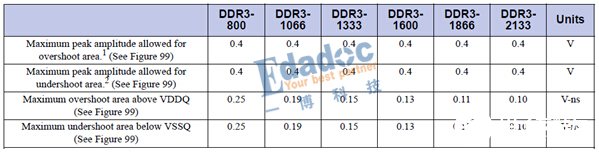

对信号幅值的要求不仅仅在这一个方面,幅值太小,会让芯片无法识别信号,那么幅值越大,岂不是对于信号的判定越有利。其实不然,一般的芯片都会有一个耐压值,高于该值,对于芯片的使用寿命会有一个较大的影响,所以,可以看到JEDEC中,还有一个Overshoot和Undershoot的概念,下面是DDR3对于信号这方面的一个要求,图六中是对Overshoot和Undershoot一个面积区域和具体的数值的定义,即最大值的范围在VSS-0.4~VDD+0.4之间,斜率按照相应的速率查找,其中斜率的定义对于数据线和地址线是有区别的,要用到的时候,在JEDEC中查找即可。

图六

这些都是对DDR信号最基础的认识,只是基于幅值方面的一些要求。

编辑:hfy

-

DDR3

+关注

关注

2文章

282浏览量

42821 -

DDR

+关注

关注

11文章

724浏览量

66173 -

电磁波

+关注

关注

21文章

1478浏览量

54322 -

JEDEC

+关注

关注

1文章

37浏览量

17605

发布评论请先 登录

相关推荐

过孔STUB长,DDR信号“强”?

关于DDR3信号扇出和走线问题解析

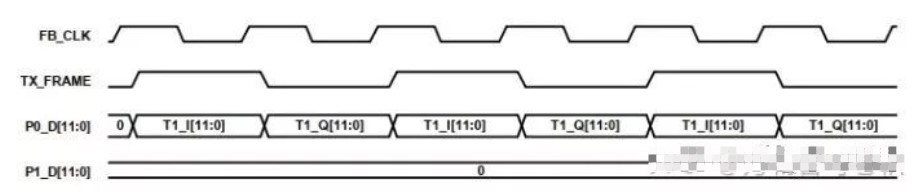

DDR工作原理_DDR DQS信号的处理

DDR高速信号线的布线原则和技巧

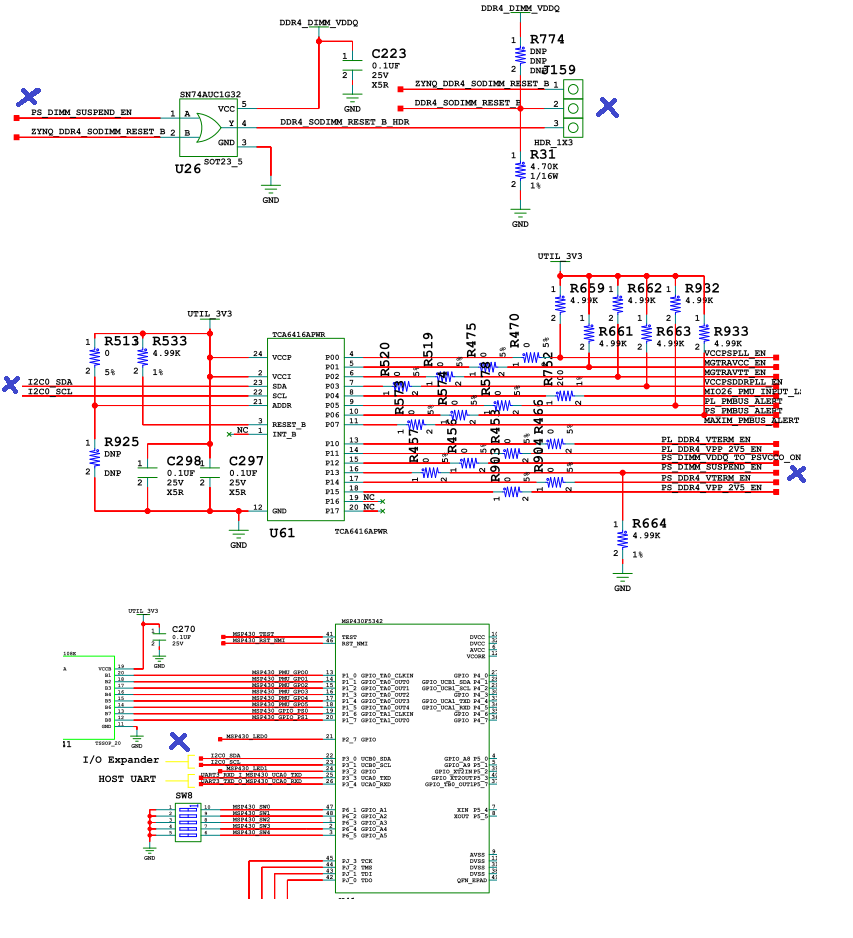

ZCU10中MPSoC对DDR复位信号设计

如何选择DDR的拓扑结构?怎样去改善信号质量呢?

DDR4通道中过孔 stub对信号质量的影响分析

如何去解决LVDS差分接口的DDR信号问题

改善带有ECC奇数负载的DDR2信号质量的方法

关于DDR信号的如何去判断信号质量?

关于DDR信号的如何去判断信号质量?

评论