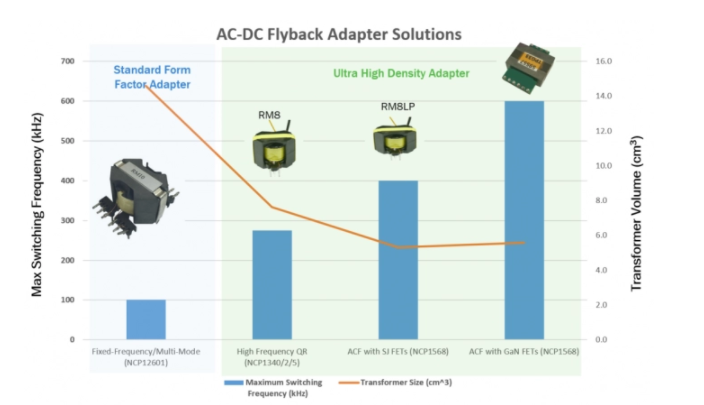

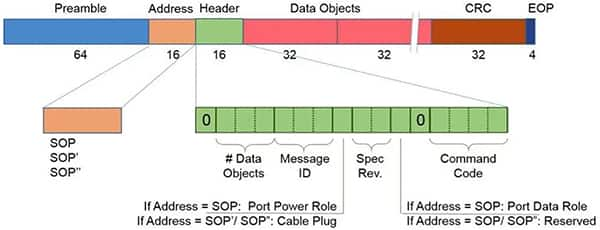

诸如USB-C PD 3.0 100 W可编程电源(PPS)之类的新兴应用推动了对更小,更紧凑的开关模式电源(SMPS)外形尺寸(通常称为超高密度(UHD))的需求。如您在图1中所见,提高开关频率可以减小变压器的体积,从而有益于UHD,但是更高的开关频率会增加功耗,从而需要不断发展的反激式架构。

约100 kHz的固定频率/多模式反激式开关驱动标准SMPS适配器中的较大变压器。移植到准谐振(QR)反激会使开关频率增加到〜280 kHz,从而将变压器减小到较小的RM8尺寸。采用有源钳位反激式(ACF)可使您达到〜450 kHz,从而实现了外形较小的RM8LP变压器。最后,用氮化镓(GaN)代替硅结(SJ)FET可实现> 600 kHz的开关,甚至更小的变压器体积。

图1增加开关频率可减小变压器体积,但更高的开关频率会增加功耗。资料来源:安森美半导体

反激式介绍

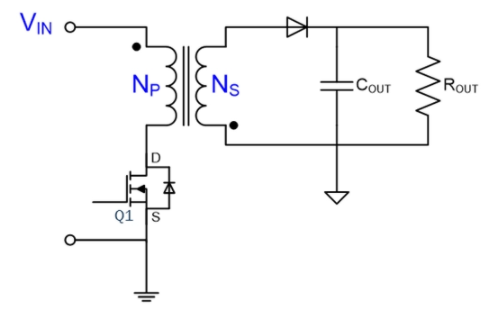

反激是低功率和中功率AC-DC转换器的一种流行拓扑,主要是因为它的低成本和易用性。反激式假定为DC输入,并在次级侧包含一个变压器,一个电源开关(Q1)和一个二极管(图2)。变压器(点表示初级侧与次级侧异相1800)是一个耦合电感器,只有在关闭电源开关时,能量才从初级传递到次级。

图2反激式拓扑在次级侧包括一个变压器,一个电源开关和一个二极管。资料来源:安森美半导体

反激操作

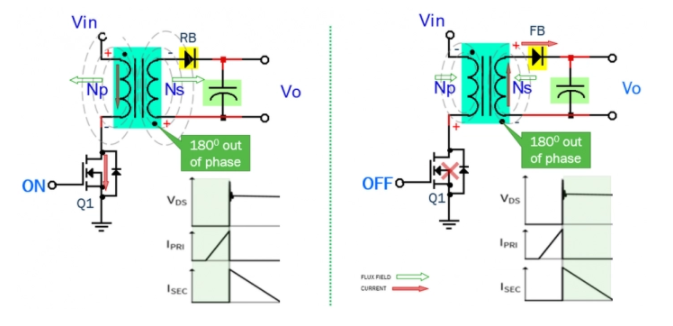

当电源开关(Q1)接通时(图3左),电流从Vin流出,导致能量存储在初级侧和次级侧(磁通场扩展)电感器中。电流不会流过次级,因为二极管由于180º的反相而反向偏置。

当电源开关关闭时(图3,右),初级和次级磁通场都开始塌陷,初级侧的极性发生变化(反激作用),现在电流在次级侧流动,因为二极管正向偏置。

图3此图显示了电源开关打开(左)和关闭(右)时的反激式操作。资料来源:安森美半导体

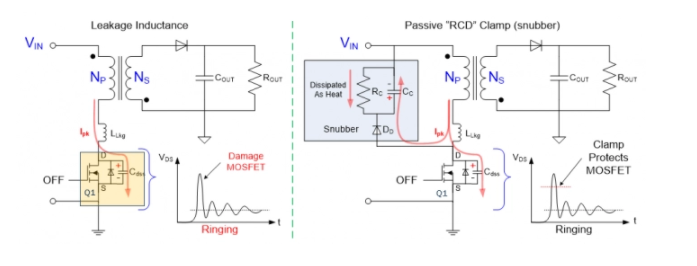

反激式漏感

不幸的是,当电源开关(Q1)关断时,初级侧漏电感(LLkg)与电源开关的漏源电容Cdss相互作用,导致VDS出现过多振铃,从而损坏MOSFET(图4,剩下)。可以添加一个称为缓冲电路的无源电阻电容二极管RCD钳位来保护MOSFET(图4,右)。缓冲器将LLkg能量从MOSFET漏极移动到缓冲器电容器(CC),并通过RC散发热量。缓冲器不能提高整体反激效率。

图4添加RCD缓冲器可保护MOSFET。资料来源:安森美半导体

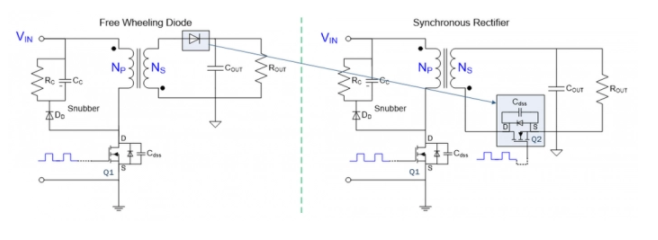

次级侧的同步整流器

用MOSFET(图5中的Q2,右)替换“续流”二极管(图5,左)可提高次级侧效率。MOSFET的RDSON耗散的功率比硅二极管(0.6V正向偏置)甚至肖特基(0.3V)二极管低得多。

图5在次级侧添加SR MOSFET可提高效率。资料来源:安森美半导体

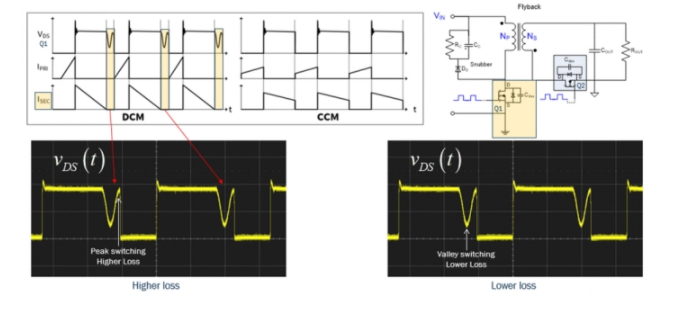

谷切换和准谐振反激

在次级侧电流(ISEC)达到零或不连续模式(DCM)之后,由于励磁电感和开关节点电容之间的谐振,Q1电源开关VDS可能会出现振荡(图6)。这些振荡形成谷。QR开关将寻找最低谷点,以便下次打开电源开关。简而言之,在峰值期间打开Q1会增加功耗,而在谷值期间打开Q1则会降低功耗。

图6电源开关可能会出现谷底开关振荡。资料来源:安森美半导体

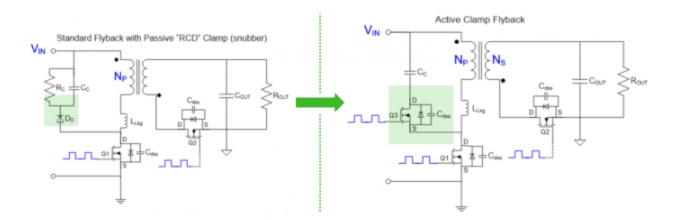

主动钳位反激

用MOSFET(Q3)替换钳位二极管(图7,左)可以提高效率(图7,右),并保护电源开关(Q1)。

图7ACF架构提高了电源效率。资料来源:安森美半导体

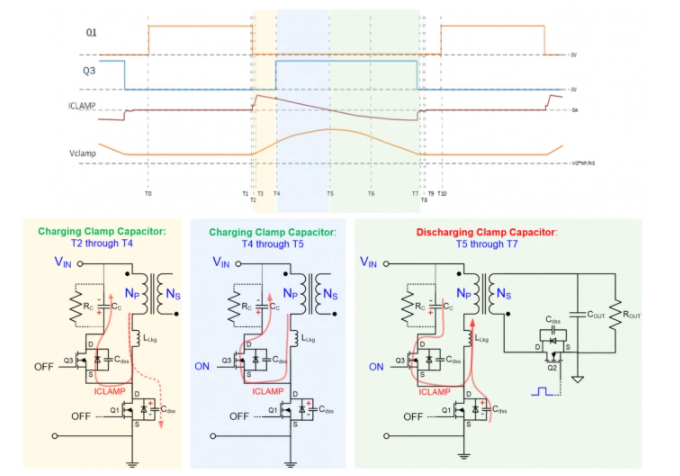

ACF体系结构可以将泄漏电感循环回负载。参考图8的相对时序图,电源开关(Q1)在T0接通,在T2断开。在T2处,漏电感(ICLAMP)开始流过有源钳位(Q3)体二极管,从而给钳位电容器(VCLAMP)充电。在T4,Q3打开,继续VCLAMP充电。在T5时,ICLAMP变为负值,现在VCLAMP通过Q3将漏感放电回到负载,直到T7。

此相对时序图显示了图8ACF泄漏电感的循环。资料来源:安森美半导体

从T9到T10,有源钳位(Q3)在下一个Q1接通时间内将VDS稳定在0V,这称为零电压开关(ZVS)。如果在ZVS,则FET电容为零。因此,导通开关损耗为零,从而产生更高的效率。这是一种软开关形式,也有利于EMI。

ACF的缺点

ACF有两个缺点。再参考图8,从T5到T7的相对时序,当ICLAMP变为负值时,磁通密度增加,导致有源钳位铁芯损耗比图4的RCD缓冲器稍高。在Q1关断时间内缠绕;这增加了初级绕组损耗。

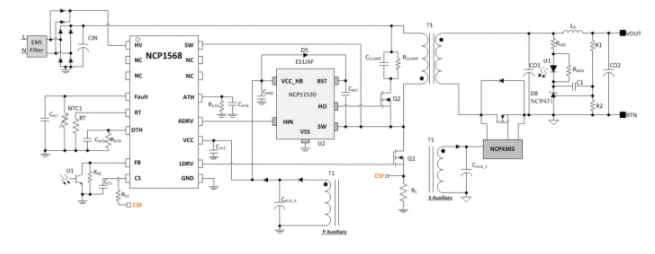

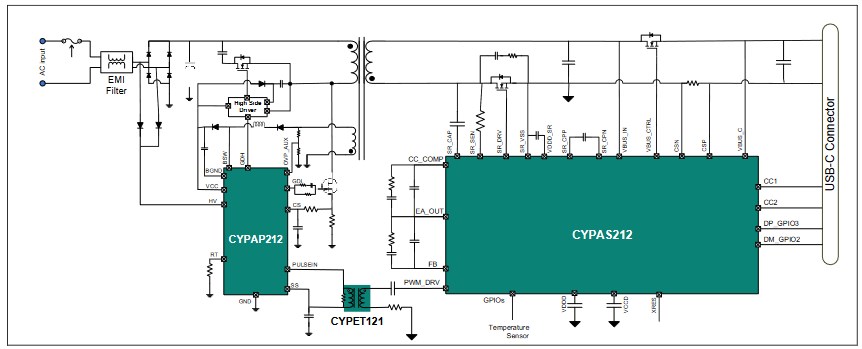

安森美半导体的NCP1568是高度集成的AC-DC脉宽调制(PWM)控制器,旨在实现ACF拓扑(图9),从而使ZVS能够用于高效,高频和高功率密度应用。不连续传导模式(DCM)操作可在待机功率<30 mW的轻负载条件下实现高效率。

NCP1568 LDRV输出能够直接驱动市场上大多数超级结(SJ)MOSFET,而无需外部组件。ADRV驱动器是5V逻辑电平驱动器,用于将驱动信号发送到NCP51530等高压驱动器。高压驱动器应具有较小的延迟,并适合高达400 kHz的工作频率。

图9NCP1568 ACF驱动超级结MOSFET Q1。资料来源:安森美半导体

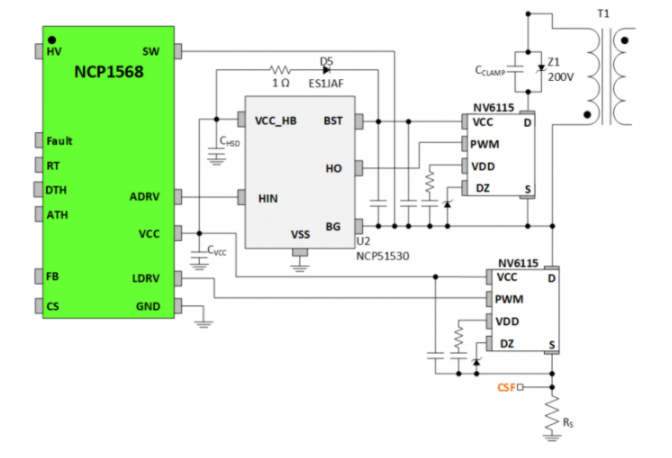

ACF驱动GaN

交换用于GaN晶体管的SJ MOSFET可以实现更快的开关频率,这主要是由于GaN的寄生电容较低。当然,GaN的成本要高于SJ FET。Navitas Semiconductor的NV6115驱动器GaN单个组合接受来自12V或5V驱动器的输入信号。驱动器调节已在GaN内部完成。图10的配置显示了来自NCP1568和NCP51530的驱动信号足以满足系统需求。

图10 NCP1568 ACF驱动NV6115 GaN功率晶体管。资料来源:安森美半导体

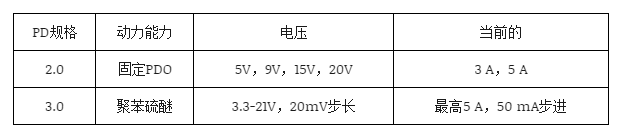

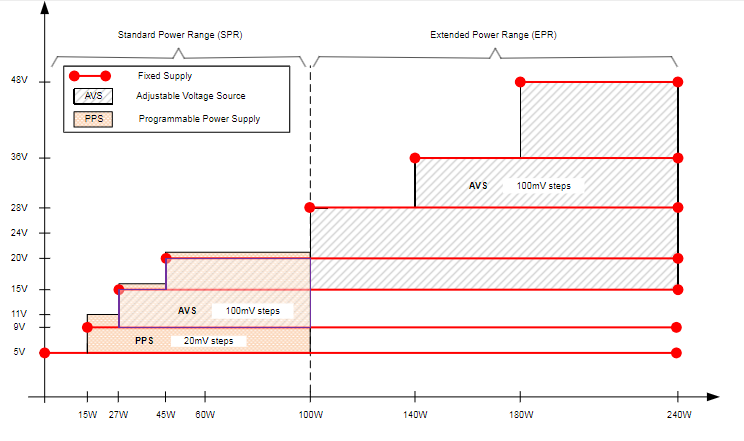

USB-C供电2.0与3.0 PPS

USB-C PD源最多可以播报七个电源数据对象(PDO),用于将源端口的电源功能公开给支持PD的接收器。PD 2.0 PDO是固定的,而PD 3.0 PDO是从3.3V到21V的可编程电压“范围”(20mV步进)设置,以及高达50A的电流设置的可编程“范围”(以50mA步进)(表1)。PPS的优势在于该源可以提供更精细的电压/电流粒度,从而提高USB-C源和宿之间的效率。

表1 USB-C PD 2.0与3.0 PPS

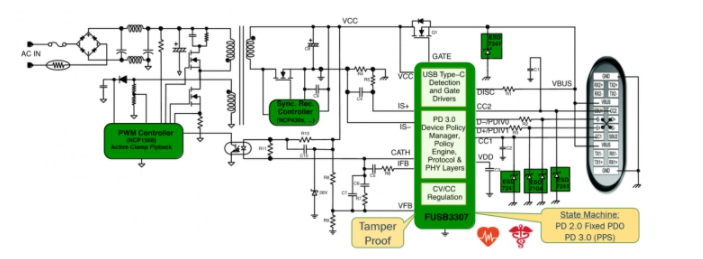

所述FUSB3307是一个完全自主PD 3.0 1.2版和C型V1.3,100W,源控制器能够提供从3.3-21V(20mV的步骤)VBUS和至多5 A(50毫安步),最多共七个固定和PPS PDO。FUSB3307是一款不含MCU的低成本硬件状态机解决方案。无需开发固件,就可以加快产品上市时间,以提供防篡改的全功能解决方案。

FUSB3307控制通过光耦合器的CATH引脚电流,向初级侧控制器提供反馈以调节VBUS电压。

图11 FUSB3307 PD 3.0 PPS控制器是一种防篡改的全功能解决方案。资料来源:安森美半导体

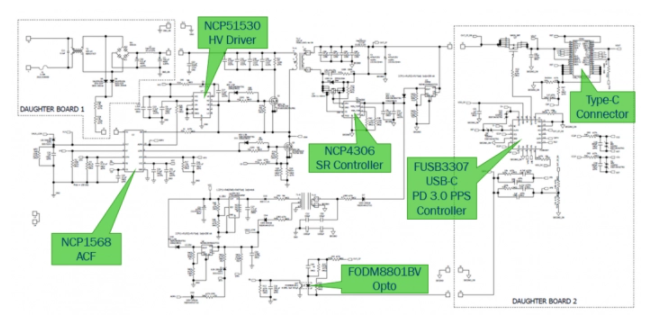

图12示出了29 W /在3,60瓦ACF参考安森美半导体设计与USB-C PD 3.0和PPS。NCP1568 ACF(U2)通过NCP51530(U7)3.5 A,700V半桥驱动器控制SJ电源开关(Q1)和SJ有源钳位(Q2)。NCP4306(U5),7A(漏极),2A(源极)栅极驱动器用于同步整流器控制。FUSB3307(子板2的U1)是基于状态机的USB-C PD 3.0端口控制器,可通过FODM8801BV(U8)光耦合器控制NCP1568 FB输入及其CATH输出来调节VBUS(5-20V)。

图12该60 W USB-C PD 3.0 PPS参考设计包含NCP1568 ACF,NCP51530驱动器,NCP4306控制器,FUSB3307控制器和FODM8801BV光耦合器。资料来源:安森美半导体

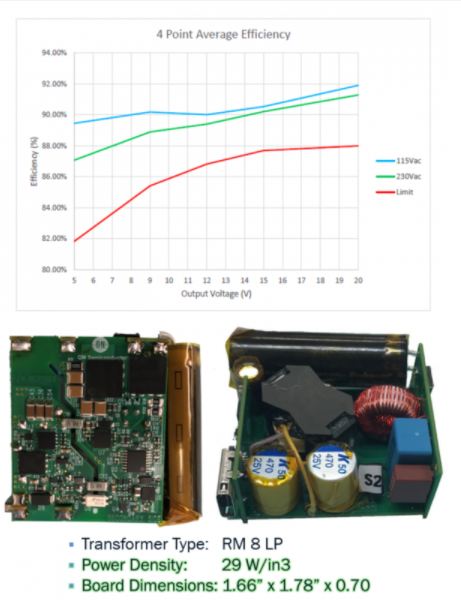

图13的4点平均效率图的每个数据点捕获以下四个额定功率输出的平均效率。使用超级结MOSFET可以达到25%,50%,75%和100%的频率,最高开关频率为450 kHz。可以看到,从5V输出到20V输出4点平均的NCP1568 115 Vac(蓝线)和230 Vac(绿线)远高于要求的能源部(DoE)VI级最低限制(红线) 。

图13该4点平均效率图显示NCP1568超过了DoE Level VI的最小限值。资料来源:安森美半导体

许多应用都对UHD电源提出了很高的要求,包括100 W USB-C PD 3.0 PPS。ACF是在成本和UHD性能之间实现最佳平衡的首选架构。这是因为在不增加GaN成本的情况下,可以达到29 W / in 3的功率密度,最高达到92%的4点效率。并且,如果应用允许更高的成本和更高的效率,那么ACF还可驱动GaN,以实现更高的效率和更高的功率密度。

鲍勃·卡德(Bob Card)是负责安森美半导体美国高级解决方案集团(ASG)的市场经理。

编辑:hfy

-

变压器

+关注

关注

159文章

7449浏览量

135119 -

驱动器

+关注

关注

52文章

8209浏览量

146231 -

开关电源

+关注

关注

6457文章

8325浏览量

481651 -

USB-C

+关注

关注

2文章

372浏览量

34073

发布评论请先 登录

相关推荐

使用LMG3622EVM-082 65W USB-C PD高密度准谐振反激式转换器

USB Type-C® 和 USB Power Delivery:专为扩展功率范围和电池供电型系统而设计

使用UCC28782EVM-030 65W USB-C PD高密度有源钳位反激式转换器

使用LMG3624EVM-081 65W USB-C PD高密度准谐振反激式转换器

使用LMG3626EVM-074 USB-C PD高密度准谐振反激式转换器

usb-c和type-c的接口可以混用吗

140 W超高功率密度USB-C EPR适配器,采用ZVS反激式转换器和PFC +混合反激式控制器

如何通过最少的编程工作将 USB-C 设备的传输功率迅速提升到 100 W

USB-C PD 3.0设计实现更高的效率和更高的功率密度

USB-C PD 3.0设计实现更高的效率和更高的功率密度

评论