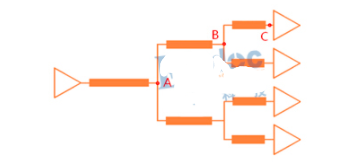

T拓扑不仅仅可以叫树形拓扑,他还有另外一个马甲,叫等臂分支拓扑;望文生义,这个拓扑的重要一个要素就是分支等长,其实也就可以看出这个拓扑估计是天秤座的。

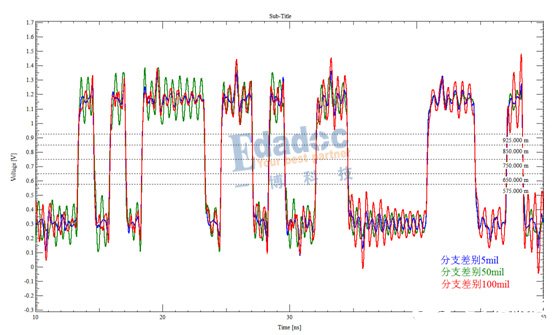

T拓扑对于分支等长很敏感,分支不等长的情况对于波形有什么影响呢?T拓扑本身就是一堆的阻抗不连续,反射不仅存在于每个分支内部,还会在分支之间影响,因此各分支接收端的波形会有比较大的反射振铃。然而,当T拓扑完全对称即两分支等长的话,两边接收端的反射波形会有重叠,并且大小相等,方向相反,自然而然,重叠部分的影响可以消除。从下图可以看出,当等长控±5mil时,波形比较好,当两臂的误差到50mil时,振铃就比较大了,所以T拓扑对于分支的等长是比较敏感的,分支等长是T拓扑比较重要的一个设计规则。

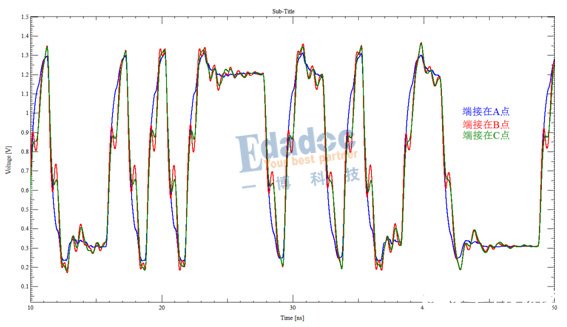

T拓扑本身的反射很多,要怎样来得到漂亮的接收波形呢?主要有两种措施,源端串联和末端并联。T拓扑经常在DDR中应用到,对于比较高速率的DDR信号而言,串联端接会使上升沿变缓,所以这个一般不常应用到,主要应用的是并联端接。但是说好的末端并联端接,到了T拓扑似乎位置变成了中间,为什么会有这种变化呢?如下图,是端接放在不同位置上得到的波形:

再次强调一下T拓扑是一个有强迫症的结构,对于对称美有着最极致的要求,如果不对称,单分支加端接会比不加端接的影响更大,如果每个分支都加端接的话,首先布局会需要更大的空间,其次作为起主要作用的电阻,是有直流功耗的,如果每个分支都加的话,功耗就太大了而且发热也是不可想象的,一级T拓扑还好说,两级,三级呢。..。.所以,端接放在A点附近是各种情况综合考虑的结果,所谓“权衡的艺术”。这就造成了T拓扑不能太多级,所以到DDR3的时候,Fly-by赛高,他拯救了layout工程师。

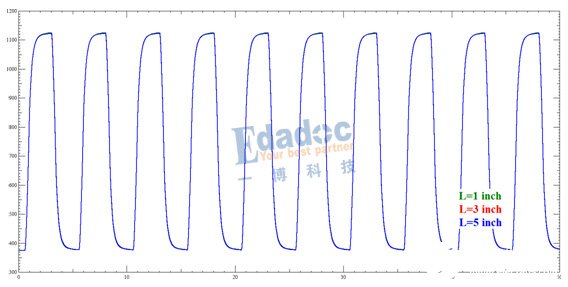

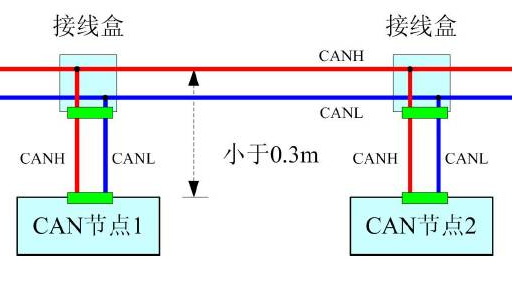

讲到并联端接的时候,就想到以前看到过很多guideline,讲到DDR走T拓扑的时候都有一个要求,就是上拉到T点的线长不能超过XXX的长度,最少的是0.1inch。但是端接是为了阻抗匹配的,线的阻抗和线长关系不大啊,为什么要对线长做限制呢?仿真结果表明,影响微乎其微。

大胆的猜测一下这些guideline出现的原因,如左图所示时,L的长度对接收端的波形有影响,L越小,端接效果越好;如右图所示时,L的长度和接收端的波形影响不大,所以这种情况下的并联端接不需要考虑L的线长影响。

guideline中直接将左右两种并联端接一概而论,所以会有L线长的限制。

编辑:hfy

-

拓扑结构

+关注

关注

6文章

326浏览量

39480 -

波形

+关注

关注

3文章

383浏览量

31745

发布评论请先 登录

相关推荐

新手请教关于T型接点等长问题

Altium designer 等长布线

一个等时不等长的DDR

AD中关于绕等长的方式与方法

ddr3菊花链拓扑结构是什么

关于一个一个等时不等长的DDR设计

【驱动】一种中断接收的不等长不规则uart数据机制

T拓扑,分支不等长对于波形有什么影响?

T拓扑,分支不等长对于波形有什么影响?

评论