对于许多应用而言,下一代IC封装是在缩小整体封装尺寸的同时实现硅缩放,功能密度和异构集成的最佳途径。异构异构集成提供了增强设备功能,加快上市时间和提高硅产量弹性的途径。

已经出现了多种集成技术平台,可以对成本,尺寸,性能和功耗进行优化,以满足移动市场,汽车,5G,人工智能(AI),增强现实(AR)和虚拟现实( VR),高性能计算(HPC),物联网,医疗和航空航天。

编者注:本文是AspenCore特殊项目的一部分,该项目是一系列探索高级IC封装的相互关联的文章。

但是,这些包装对于传统的包装设计工具和方法提出了独特的挑战。设计团队必须共同努力,以验证和优化整个系统,而不仅仅是单个元素。传统的IC封装基板设计通常与基于小型层压板和/或积层的PCB非常相似。它通常由传统的PCB制造商制造,并且通常使用改进的PCB工具进行设计。

相反,当今的高级封装使用的制造技术,材料和工艺与硅铸造工艺越来越相似,因此需要一种新的方法进行各个级别的设计和验证。

设计团队必须克服的第一个挑战之一是基板的精确聚合(可以是有源和无源的)以及分立器件。这些基板和设备来自多个来源和供应商,最有可能以多种(通常是不同的)格式提供。

考虑到多种数据源和格式,很明显,需要一个全面的验证流程-该流程负责装配级的物理验证,以及更深入的系统级电气,压力和可测试性验证。还需要能够提供快速,准确和自动化流程的设计工具,以确保能够满足市场进度和性能预期。理想情况下,这些流程提供围绕整个异构包装组件的3D数字模型或数字孪生模型构建的单个集成过程。

这些下一代IC封装需要一种下一代设计和验证解决方案,该解决方案应包含并支持:

- 数字样机

- 多域整合

- 可扩展性和范围

- 精密制造交接

- 金色签到

- 虚拟样机的数字孪生

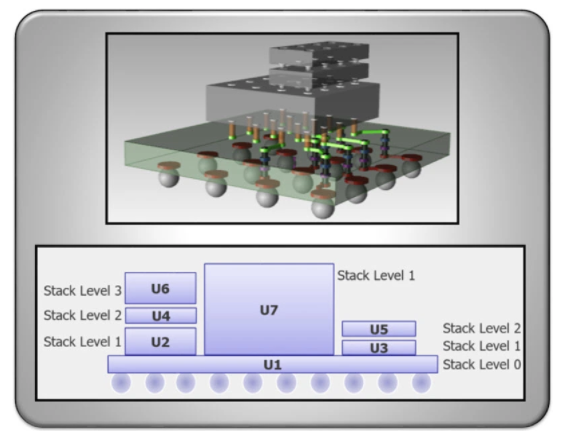

建立2.5D / 3D异构装配的数字孪生虚拟模型可提供包括多个设备和基板的完整系统的全面表示。数字孪生可以从基板级设计规则检查(DRC)开始自动验证异构组件,并扩展到布局与原理图(LVS),布局与布局(LVL),寄生提取,应力和热分析,最后进行测试。

图1真正的3D数字孪生虚拟原型是整个设备的蓝图。资料来源:Mentor Graphics

模型构建要求具有将来自不同来源和不同格式的数据聚合为适合驱动验证和分析的内聚系统表示的能力。理想情况下,这是使用LEF / DEF,AIF,GDS或CSV / TXT文件等行业标准格式完成的。功能也应该以一种自动识别设备和基板接口的方式存在,而不必实例化伪组件。这允许多设计者异步设计和验证。反过来,当所有组件都完成并集成时,这又确保了整个系统的成功。

数字孪生方法的主要好处之一是,它是在设计层次结构的每个级别上推动完整的物理和电气验证的黄金参考。这样就消除了使用多个静态电子表格来表示引脚和连接信息的麻烦,而用Verilog格式的完整系统级网表代替了它们。

原始数据的保存和重用(例如设备的Verilog描述)是关键。发生翻译或转换(例如原理图或电子表格)时,最大的风险来自于。如果这样做,“数字线程”将立即中断,并且连接错误的风险将急剧上升。

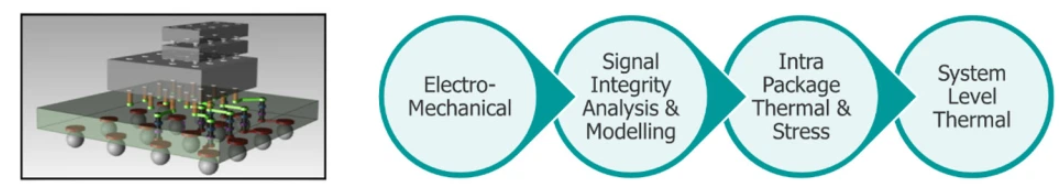

多域整合

数字孪生方法还可以实现多域和跨域集成。要将更复杂的高级IC封装更快地推向市场,需要高度集成的设计和验证-从电子基板设计到机械封装散热器和PCB安装硬件,包括电气,散热,测试,可靠性等方面的相互关联,当然,可制造性。如果没有系统级的设计和验证方法,工程师就有可能经历昂贵的重制甚至更糟。

电气和机械信息的同步对于确保将包装放置在机柜或整个系统中时不会发生物理违规至关重要。在设计期间进行增量数据交换对于确保ECAD-MCAD兼容性和增加首过成功率至关重要。它还有助于创建更可靠的设计,同时提高生产率并缩短上市时间。

IC封装设计人员和定制散热器设计人员都必须可视化,探索和优化集成,这一点非常重要,理想情况下,这是一个异步过程,可以最大程度地减少跨域中断。

图2数字孪生方法可实现多域和跨域集成。资料来源:Mentor Graphics

封装设计与机械/热设计之间的同步也是首次成功的重大挑战。异质的多基板封装表现出多种芯片-封装相互作用,其中最大的之一是热量的散热,尤其是这种封装中典型的非线性产生的热量。

热管理的一种典型方法是使用散热器进行热传递和散热。但是,散热器的设计才是最好的。为了使散热器高效有效,必须与包装一起设计和模拟散热器,而不是事后才想到的。以3D方式设计整个封装可确保有效地实现热传递,而不会造成重大的设计折衷。

图3这是一个由数字孪生驱动的集成散热器设计。资料来源:Mentor Graphics

2.5D和3D堆叠都可能产生各种意外的物理应力,例如安装过程中的基板翘曲和凸块引起的应力。设计人员必须能够分析布局,以解决由此类芯片-封装相互作用及其对器件性能的影响所引起的压力。一旦封装即将实现,就可以导出准确的3D封装热模型,以将其包含在详细的PCB和整个系统的热分析中。这样可以对系统外壳进行最终调整,并可以优化自然冷却和/或强制冷却。

先进的IC封装给信号完整性工程师及其设计工具带来了许多新挑战。裸片直接安装在衬底上,因此有可能将衬底布设到管芯上的再分布层布设耦合。封装不再是在金属层之间具有易于建模的简单过孔的简单平面层结构。取而代之的是,可以有多种材料和特性完全不同的基材。分析可以成功用于许多与信号和电源完整性相关的项目。

此外,还有许多项目很难模拟。这些通常属于电磁干扰(EMI)类别。尽管可以分析和模拟这些由返回路径造成的EMI问题,但这样做通常没有任何效果。例如,在走线穿过平面裂缝的情况下,仿真设置和运行时间将非常可观,并且所有工程师都将了解到,这种情况很糟糕,应该避免。

通过在设计过程中基于软件的自动化,基于几何的检查和检查,可以最好地识别这些问题。这些通常可以在几分钟内完成设置和执行,并明确标出问题区域以进行补救设计。这种“向左移动”的方法可避免从一开始就产生问题,从而使EMI分析更多地是验证签核步骤。

2.5D和3D异构设计通常使用硅通孔(TSV),硅通孔是延伸通过管芯或基板以连接正面和背面的长通孔。这些TSV允许管芯和基板堆叠并直接互连。但是,除了它们自己的重要电特性外,TSV还对附近的设备和互连的电性能产生间接影响。

为了准确地为2.5D / 3D异构系统建模,设计人员需要从这些2.5D / 3D元素的物理结构中提取精确电气参数的工具,然后将这些参数输入行为仿真器。利用完整封装组件的3D数字孪生模型,设计人员可以准确地提取这些2.5D和3D模型的寄生特性。一旦使用适当的方法和过程正确提取了元素,就可以将它们组装到系统级互连模型中并进行仿真,以分析性能和适当的协议合规性。

可扩展性和范围

异构封装技术的设计,制造和组装更加复杂,可能会限制除领先的半导体公司及其尖端设计之外的所有公司的可用性。幸运的是,设计和供应链生态系统可以在使此类技术实现民主化方面发挥强大作用,使所有设计人员和公司都可以使用它们,就像硅代工厂界使用工艺设计套件(PDK)所做的那样无处不在。

自动IC验证由代工厂创建的设计规则驱动,并在PDK中提供给设计公司。EDA工具供应商根据这些规则对工具集进行了验证,以确保其验证工具能够产生经过验证的,可重复的,签核的质量结果。封装装配设计套件(PADK)的目的与PDK相似,它使用确保整个过程一致的标准化规则来促进可制造性和性能。

显然,PADK必须同时包括物理验证和提取签核解决方案,并且还应解决热和/或应力签核解决方案。所有这些过程都应独立于用于创建装配体的任何特定设计工具或过程。此外,完整的PADK必须在IC和封装域中均能正常工作,这意味着流程必须支持多种格式。最后,所有这些验证过程都必须由包装组装/ OSAT公司进行验证。

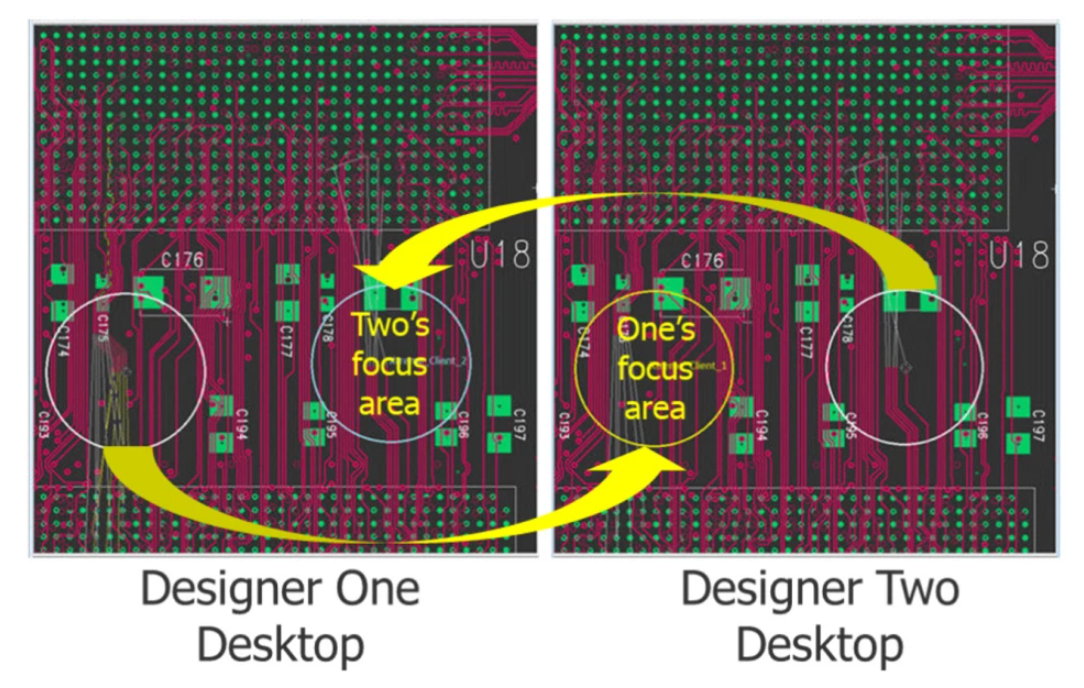

先进IC封装的规模和复杂性给设计人员和设计进度带来了直接压力,而这往往会不断延长。并发团队设计是一种新兴的流行管理方法,其中多个设计师可以同时在本地或全球网络上从事同一设计工作,但仍具有可视化所有设计活动的能力,而不必忍受任何繁重的设置或流程管理。

图4多用户并发设计可以缩短设计周期并优化资源。资料来源:Mentor Graphics

编辑:hfy

-

虚拟现实

+关注

关注

15文章

2287浏览量

95026 -

IC封装

+关注

关注

4文章

185浏览量

26720 -

人工智能

+关注

关注

1791文章

47225浏览量

238319 -

增强现实

+关注

关注

1文章

712浏览量

44947

发布评论请先 登录

相关推荐

新质生产力材料 | 芯片封装IC载板

芯片封装的核心材料之IC载板

普莱信乔迁新址,聚焦先进封装设备国产化

什么是IC封装?

2024年全球先进封装设备将同比增长6%至31亿美元

半导体组装封装设备市场遇冷

224G 系统需要多大的 ASIC 封装尺寸?

适用于蜂窝和PDA应用的单线高级电池监控IC bq2023数据表

探索高级IC封装设计的相互关联(上)

探索高级IC封装设计的相互关联(上)

评论