作者:MOHAMMED TAWFIK ABDELHAFEZ

曾几何时,您学习了电路理论,并学到了许多分析电路的技术。两个著名且类似的技术是节点电压分析和网格分析。在节点电压分析中,首先选择一个成为参考节点的节点。假定该节点具有绝对零电势,我们通常将其称为“接地”节点。

只要您不关心电路与其他对象之间的电压关系,就不会发现此假设有害。许多子电路之间共有的节点通常是数学上简化电路分析的一个很好的选择。

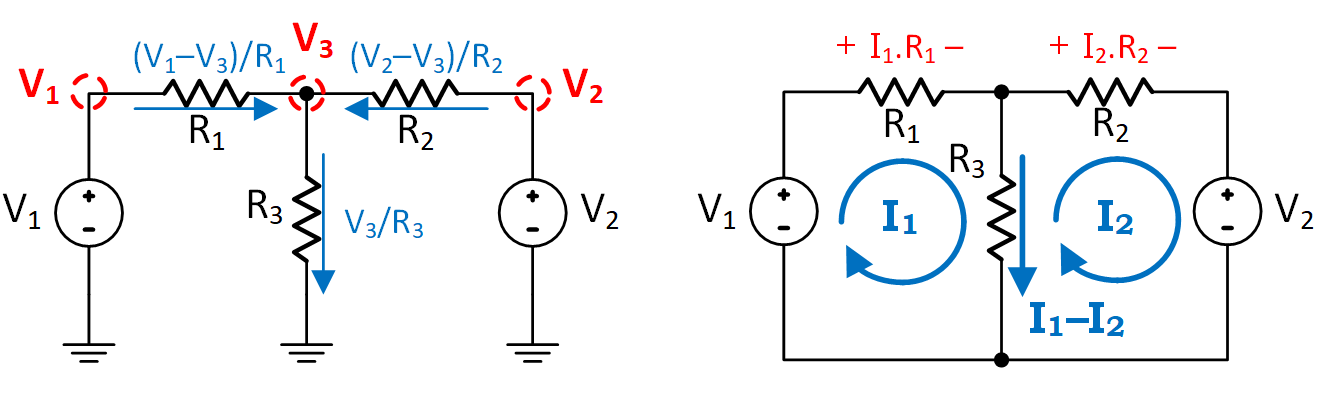

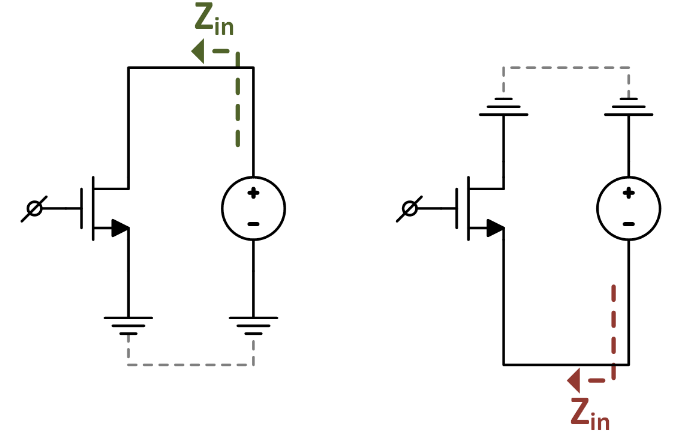

当我们学习电子电路专业课程时,通常会忘记许多电路分析技术,例如叠加,戴维南等效项,诺顿等效项和网格分析。我们主要关注一种技术,即节点电压分析(图1)。

图1节点电压分析通常简化了电子电路的分析。左侧是节点电压分析的示例,右侧是同一电路的网格分析。

经过多年作为学生和工程师的专注之后,您可能会忘记电路理论中的一些基本概念。这是致命的错误观念渗入我们的思想的时候。

常见误解

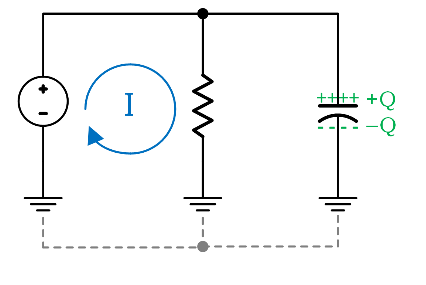

地面节点通常被认为是所有电荷的物理墓地,但事实并非如此。地面节点仅仅是我们个人选择的节点。除了通常与许多子电路通用外,它没有什么其他的特殊之处。成为公共节点不会增加特殊的物理属性。接地节点上唯一存储的电荷是电容器的负极板电荷,电容器的一个端子接地。所有其他电荷在电路中循环,并且永不停止(图2)。请记住,所有电流都在一个回路中流动,电荷返回其源极。

图2电流电荷循环循环。接地节点上唯一存储的电荷(–Q)是属于接地电容器的电荷。

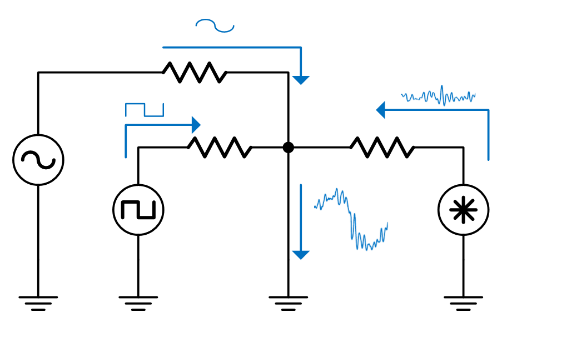

地面节点是避开噪音的避风港。但是,大多数不同的噪声电流都通过接地节点(图3)。然而,仅对于设计良好的接地轨而言,轨的阻抗可忽略不计,从而使整个轨上的噪声电势差几乎为零。

图3不同的信号电流和不同的噪声电流通过接地节点。至少在直流电路分析中,接地轨的低阻抗是保证轨中任何两个物理点之间的电势差可以忽略的唯一保证。

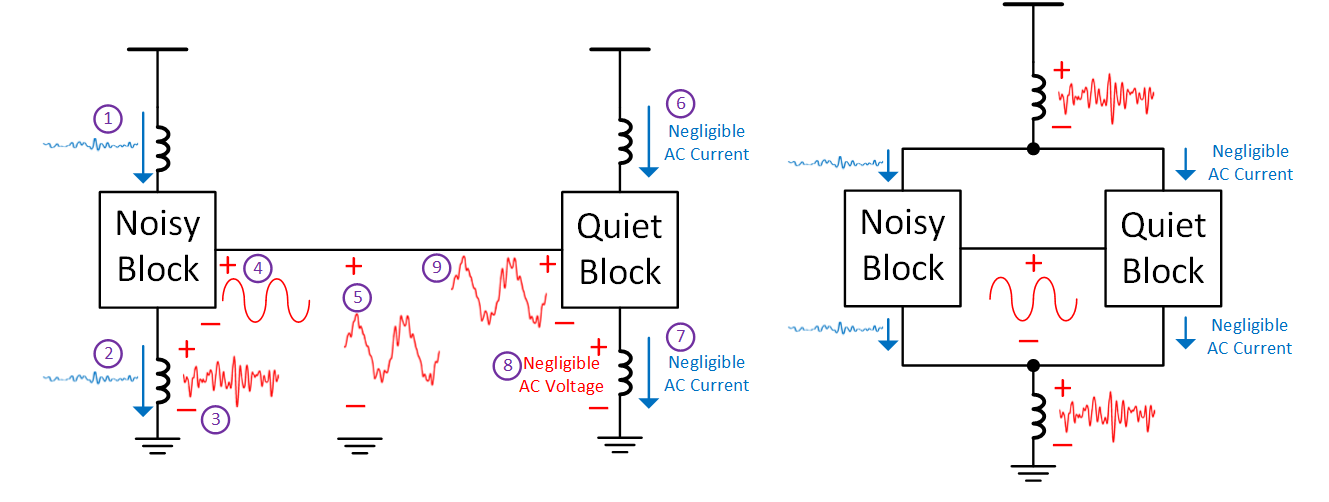

人们普遍认为,将两个相互影响的域的接地垫分开可以保护安静的域免受嘈杂的域的影响。这可能是RF工程师可能在不知情的情况下犯下的最严重的罪行之一。接地焊盘的分离在许多情况下可能会导致从噪声域输出到安静域输入的严重噪声耦合。您可能会发现这种反常理,但是当使用键合线绘制完整的电路(直至PCB层)时,这一点变得很清楚,如图4所示。当所有MOS体连接器都连接到专用接地焊盘时,也会发生类似的动作。

图4当接地焊盘如左图所示分开时,从一个域传输到另一个域的信号可能会变得非常嘈杂。分析步骤以紫色圆圈标记。另一方面,如右图所示,合并域后,信号将安全传输。但是,如果静音块的PSRR较差,则可能会受到影响。

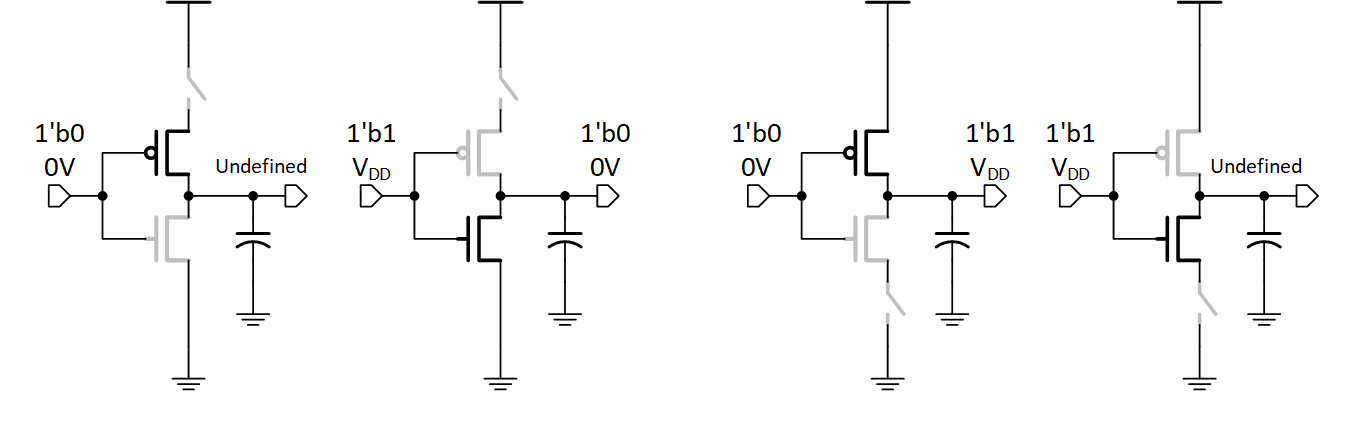

在具有功耗意识的数字设计中,浮动输出不仅与断开接地路径相关,而且还与断开电源路径相关联(图5)。物理设计偏好通常倾向于切换接地路径。这是因为在相同的导通电阻下,将使用面积小于PMOS器件的NMOS器件。

图5当电源或接地关闭时,不可避免的情况会导致输出电压不确定。不确定的输出电压取决于存储在负载电容器上的最后一个工作输出状态,电源与地的截止电阻之间的比率以及不同结的泄漏电流。

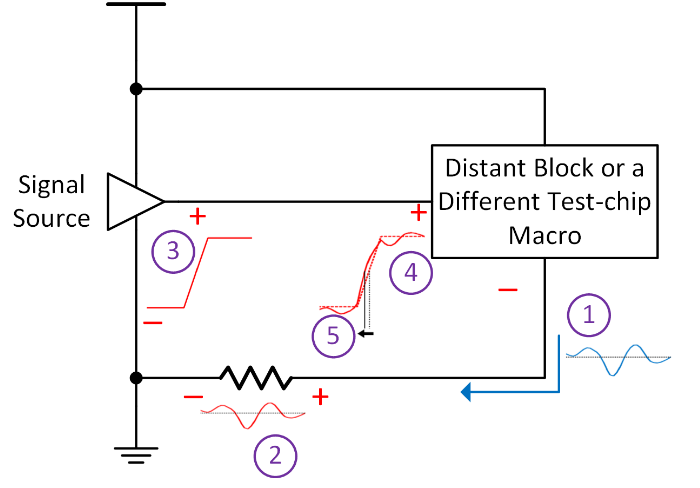

接地轨和电源轨似乎与时序收敛无关。定时关闭与不同的信元延迟和不同的信号沿有关。当接地轨具有相对较高的阻抗时,在电源轨和接地轨之间会产生相当大的IR降,这会降低有效电源电压,从而增加CMOS单元的延迟。此外,即使电源线上的平均IR降微不足道,开关噪声电流也会在接地电源线上产生明显的瞬态噪声电压。因此,如图6所示,到达距信号源较远的门的信号沿可以有效地“移动”时间[1]。时移取决于瞬态噪声的大小和极性。对于高上升/下降时间信号,这种影响变得更加明显。

图6按照紫色圆圈中的索引分析步骤,瞬态电源/接地电流曲线在接地点会产生相似的电压曲线,这会影响信号沿的有效到达时间。大量增加本地去耦电容器以吸收交流电流曲线并降低电源/接地轨的阻抗可以缓解该问题。

分开还是不分开?

这是一个棘手的问题。需要详细说明的一个重要项目是接地垫的分离。上一节可能给人的印象是,接地焊盘分离是一种不良的设计实践,尽管在许多芯片中这可能是常见的实践。通常,设计具有低电阻和低电感的单个统一接地连接要好于设计多个接地轨,而这些接地轨具有相互影响的相互作用域之间复杂的返回电流路径以及载有高频电流的大面积环路的磁耦合的麻烦。

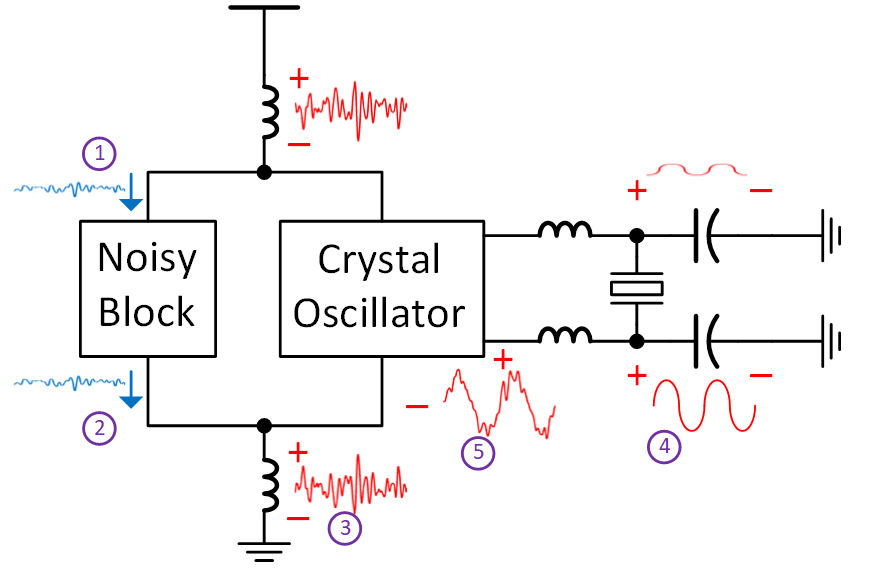

但是,在特殊情况下,您不能避免接地垫分离。例如,假设您有一个晶体振荡器和一个嘈杂的数字模块,它们都共享一个接地焊盘,如图7所示。数字模块从电源汲取噪声电流,该噪声电流通过接地轨和接合线返回。因此,接地键合线上存在明显的电压毛刺。由于该键合线与晶体振荡器的接地点共用,因此噪声电压毛刺将有效地添加到晶体振荡器内部节点处的晶体纯正弦电压。

图7按照紫色圆圈中的索引进行的分析步骤,带噪块会间接在接地线两端生成噪声电压。由于晶体实际上是一个非常尖锐的带通滤波器,因此在振荡期间,其每个端子上都存在纯正弦电压。但是,晶体振荡器的内部节点会感测到接地线两端的纯电压和噪声电压的叠加。

在需要分离的情况下,请执行以下操作:

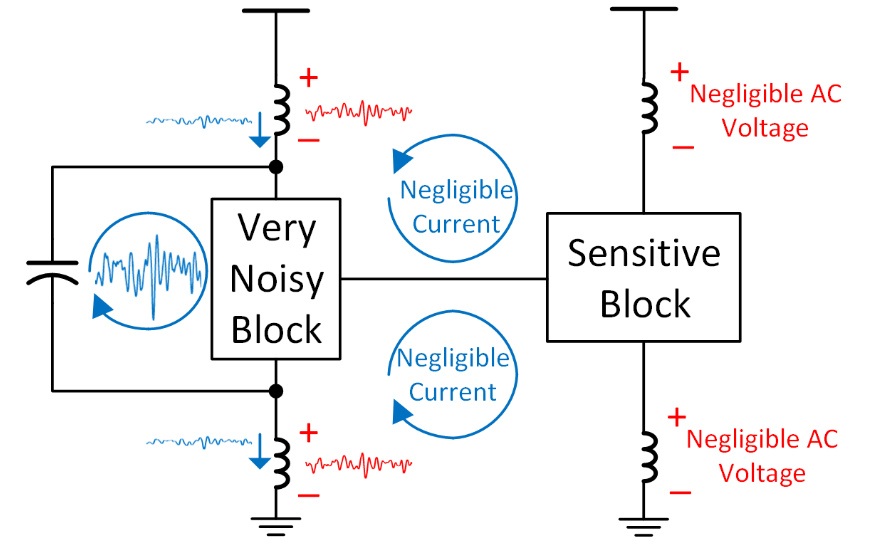

尽可能在噪声块周围放置多个去耦电容器(图8)。这减少了有噪声的电源电流在硅外部的传递,从而最小化了在块状导轨及其输出上产生的噪声电压。

最小化噪声块与其他块之间的电气交互作用,或仅使传递的电流最小化。为此,请在噪声域中使用具有较高输出阻抗的驱动器,而在安静域中使用具有高输入阻抗缓冲器的驱动器。

图8噪声块处的去耦电容器吸收了流经电源和地的大部分AC电流曲线。从噪声域到敏感域的传输电流最小化,可确保噪声的传输最小化。

接地节点仅仅是定义的节点,仅有助于电路分析。所有电流均以环路传播,并且不会在接地节点处停止。

要预见并解决与地面相关的问题,只需简单地描绘出具有所有物理连接的完整电路,而无需定义接地节点。可视化不同的电流回路和公共路径。

在做出统一或分离不同区域的接地垫的设计决定之前,请仔细研究预期的增益和潜在影响。

这是一个练习。图9的左侧显示了一个具有有限漏极阻抗的简单NMOS电流源。电源电压源看到的低频交流阻抗是多少?

图9接地节点的定义是否会影响输入阻抗值?

答案很简单。现在,让我们在电路上保持物理上相同,但是选择NMOS漏极作为接地节点,而不是NMOS源极,如图9的右侧所示。阻抗会保持不变吗?永远不要让地面躲避您。

参考

Maxim Integrated Application Note#4345,“接地良好,数字为模拟”

Mohammed Tawfik AbdelHafez是Si-Vision技术团队的高级首席工程师。

编辑:hfy

-

节点电压

+关注

关注

1文章

20浏览量

1986

发布评论请先 登录

相关推荐

电路分析技术之节点电压分析

电路分析技术之节点电压分析

评论