首先看一个真实的故事:H公司的某网络产品,PCB一直在A板厂生产,产品测试一直没有什么问题。量产的时候,由于供应链需要双供应商备份,就尝试找了B板厂进行生产。结果产品测试的时候,发现B板厂的有部分板子调试不正常。

A板厂的板子一直没有问题,产品的其他条件也都没有变化,B板厂的板子有部分调试不通。这个证据简直是太充分了,B板厂百口莫辩,赔偿损失,并被打入冷宫……

直到有一天,A板厂的某批次板子也出现了部分调试有问题。H公司的研发人员才重视起来,进行了认真的排查。最后发现一个最有可能的原因:

A板厂对这个产品的阻抗管控,在进行补偿的时候,一直以来都是负补偿,也就是说最终的阻抗偏向于负公差,阻抗值偏低。而最近这一批次,阻抗管控的时候偏向了正公差,阻抗值偏高。A板厂想着反正都是在10%的误差范围以内,都是符合要求的。再对产品的信号质量进行严格测试发现,产品的裕量本身就非常小。就像下图的男子,稍有偏差,可能就要掉进水里。

我们设计的目标,是要提高产品的裕量,从而保证产品的可靠性。就像在康庄大道上开车,安全可靠。

看一个阻抗偏差的例子:

DDR4地址信号

最差颗粒结果

这个案例的整体裕量很大,10mV的眼高差异,不到40ps的眼宽差异,相对裕量来说都是很小的偏差。但是想想第一张图片的那个“一苇渡江”,如果项目本身裕量不足,或许小小的偏差就掉进河里了。设计要保证足够的强壮性,才能抵御生产所必须的偏差。

凡是生产、必有偏差

我们经常会听到产品公司的设计人员对生产提出很多要求,比如以下都是本人亲历的问题:

1、 我的板子,能不能按阻抗偏差+-5%来进行管控?(我听到过最严格的要求是+-2.5%)

2、 线宽的蚀刻公差,能做到1mil吗?不是正负哦,是总共的偏差1mil

3、 总板厚的偏差,能不能做到+0,-2.5%?

4、 ……

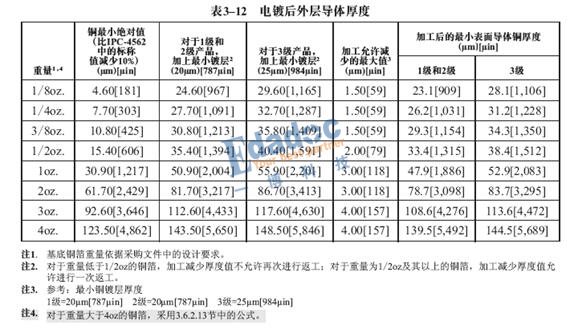

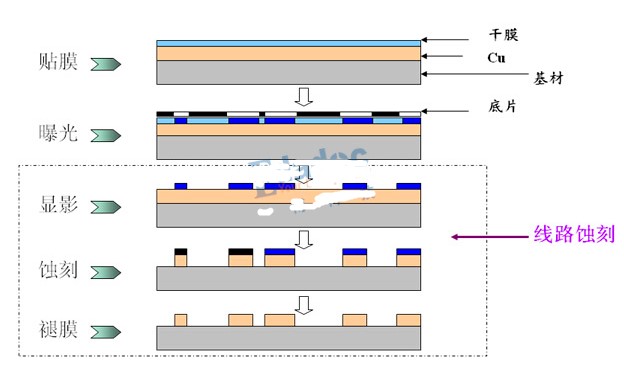

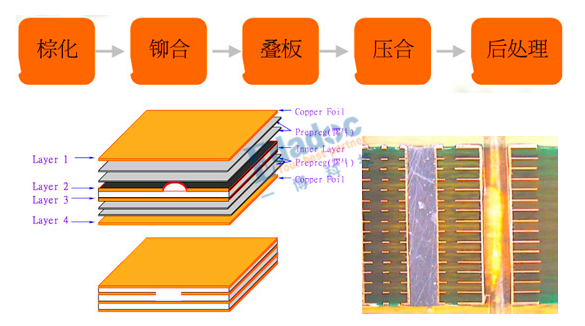

每次我都要不厌其烦的解释,板厂制板,是物理和化学的过程,制板工艺这几十年来并没有本质的变化,还是蚀刻,压合,钻孔,电镀……这些机械的过程都会有偏差。还记得我们去年的话题吗?为什么常规阻抗控制只能是10%的偏差?这是有很多其他偏差累积在一起的结果:

1、 板材来料本身的偏差

2、 PCB加工过程的蚀刻偏差

3、 PCB加工过程层压带来的流胶率等偏差

4、 高速的时候,铜箔的表面粗造度,PP的玻纤效应,介质的DF频变效应等

大家应该也还记得那张著名的偏差正态分布图:

按照10%来进行阻抗偏差的管控,最符合正态分布的智慧,在成本和性能之间取得最佳的平衡点。

当然高速先生的观点是:

1、当设计裕量足够的时候,我们要尽可能考虑满足生产的要求,这个就叫DFM。

2、设计遇到瓶颈的时候,生产就要来帮忙,尽可能攻克难关,这叫制造升级

3、当设计和生产都遇到天花板的时候,这就是产业升级的驱动力了

比如数字信号相对比较低速的时候,我们设计要给生产留出充足的空间,可以走很宽的线,很大的间距。随着高速设计的到来,我们开始管控阻抗。由于板厚,层数的限制,阻抗线有时候需要走得很细,驱动板厂提升工艺。随着串行总线的速率提升,损耗成为管控的对象,板厂也开始引进DeltaL等技术来评估损耗,对阻抗的管控要求开始来到7%,未来或许会到5%。随着速率突破25G28G,来到56G的时候,生产的小偏差,都会带来性能的大变化,于是整个产业都来到升级换代的边缘。

下面是我抛砖引玉,放上一些生产加工偏差规范:

编辑:hfy

-

阻抗

+关注

关注

17文章

934浏览量

45776 -

数字信号

+关注

关注

2文章

940浏览量

47487 -

DDR4

+关注

关注

12文章

317浏览量

40634

发布评论请先 登录

相关推荐

为什么常规阻抗控制只能是10%的偏差?

为什么常规阻抗控制只能是10%的偏差?

评论