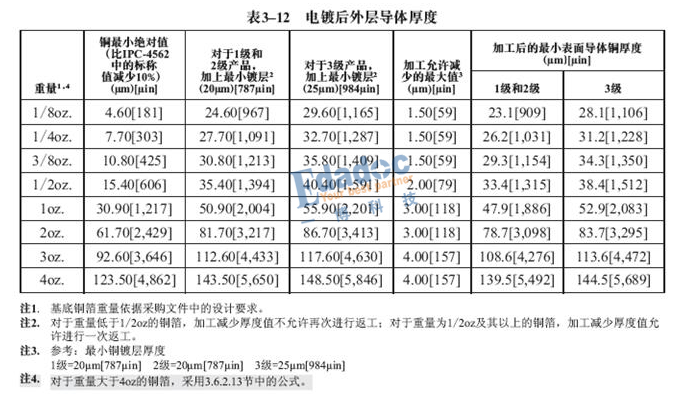

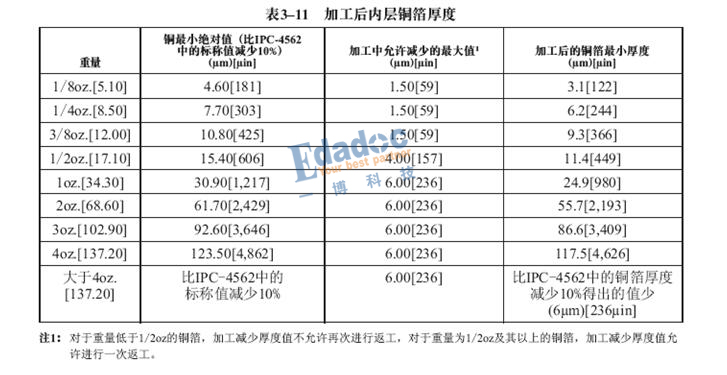

我引用了IPC对铜箔厚度偏差的定义,我们来回顾一下:

提取内层0.5oz的数据来简单做个描述:这也是多层板层叠中的常见内层厚度

内层0.5oz的铜箔正常厚度是0.7mil(17um),也是见到有人用这个厚度来做仿真和设计的。也有的公司会选择0.5oz的铜厚是0.6mil(15.4um),这是IPC允许的铜的最小值。但是还有一个加工中允许减少的铜厚是4um,加工后允许的铜箔极限最小厚度是0.45mil(11.4um)。

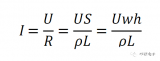

我们都知道,铜厚变化,首先会影响阻抗,然后会影响载流能力、压降、电流密度等指标,那我们来看看影响到底有多大?

内层铜厚偏差对性能的影响

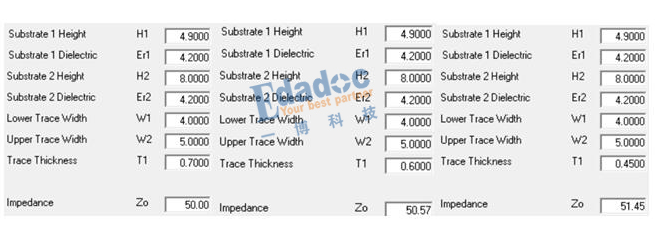

先看看阻抗:影响小于±1欧姆,不算太大的影响,并且这个影响是在整体阻抗10%的偏差里面的,设计中我们可以忽略不计。

再看看载流的影响:我们找了一个实际项目,0.5oz铜分别按标准值(0.6mil)与加工最小值(0.45mil)设置的仿真结果对比

0.5oz铜厚设置为0.6mil时:

用电端电压:839mV

VRM端输出电压:890mV

回路直流电阻:8.98mΩ

0.5oz铜厚设置为0.45mil时:

用电端电压:838mV,看起来压降变化不大

看起来压降和VRM端输出电压变化不算太大,但是直流电阻差值随铜厚变化1.78mΩ,所以压降的变化是引入远端反馈的结果,直流电阻抬升明显,还是有一定隐患。

同时看到电流密度的变化,影响会更大:

0.5oz铜厚设置为0.6mil时的电流密度,最大在120A/mm²左右

0.5oz铜厚设置为0.45mil时的电流密度,最大在160A/mm²左右

直流电阻抬升,电流密度变大,加工误差的影响不可忽略。回顾我们上一个话题开始的故事,可能PCB板厂的加工都在行业规范允许的误差范围,但是最终导致影响到产品性能,这本质上是设计裕量的问题。凡是生产,必有偏差,PCB设计裕量要预留出生产允许的偏差。

编辑:hfy

-

阻抗

+关注

关注

17文章

995浏览量

49559 -

多层板

+关注

关注

3文章

195浏览量

28750 -

PCB设计

+关注

关注

396文章

4944浏览量

96043 -

IPC

+关注

关注

3文章

384浏览量

55121

发布评论请先 登录

厚铜PCB设计这个问题一定要注意

通宵加班设计的储能板不能用?厚铜PCB设计这个问题一定要注意

PCB孔铜厚度标准及成品铜厚构成

为什么要使用厚铜板?厚铜PCB有哪些优势?

PCB设计中铜厚和线宽的选择

铜厚、绝缘层、结构……哪些因素影响铜基板价格?

PCB铜厚不达标怎么办?从测量到成因分析

Bamtone班通:国产在线铜厚测量优选方案

内层铜厚偏差对性能的影响

内层铜厚偏差对性能的影响

评论