每年拿到DesignCon的文章后,弱水三千,我们不会只取一瓢,习惯上就会过一遍每一篇slides(为什么先是看PPT?也没什么,主要因为快……)

但好像你去商场买东西一样,会发现琳琅满目的商品,不一定每一款都适合你。同样文章也是各个小领域都有涉及,我们主要还是关注和我们相关的。之前我们bruce也发过观后感啦,在我们熟悉的PCB的大领域里有高速方面的56/112G的发展,有PCIE的,有DDR方面的,有对铜箔粗糙度,材料方面的研究。

除此之后,作为高速先生的我,很惊讶的发现了居然还有不少关于仿真的文章。实际上在短暂的惊讶之后,又感觉一切也是顺其自然,我们以前老是说仿真的意义是在于你不能凭经验和理论去预测信号的趋势和走向的时候需要去做的。

我们也在很多场合里说过,很多信号其实是不需要进行仿真的,因为我们可以预测到它最终的设计是能够满足要求。然而去到了25G,56G以上这个范畴后,我们也很难去拍脑袋就说这对走线一定OK。细微的设计忽视和加工误差都会是成功与失败的临界点,因此仿真技术的发展就变得不那么意外了。本期我先和大家分享一篇仿真的文章,个人认为是比较经典和实用的。本人也尽量为大家把这篇有点烧脑的文章解读得通俗易懂一点哈!

这篇文章的名字就如下图所示啦!应该可以翻译为一步步(手把手)教你学会如何进行仿真测试校准,提高我们的仿真精度。

其实它的下面还有一个小标题,可能更能说明这篇文章要讲的是什么。

主要研究如何进行25G-NRZ/56G-PAM4高速链路的仿真测试的校准拟合。

首先看看它要进行仿真测试的东东是什么?如下所示:

链路包括了从主芯片的pin到PCB走线到连接器的footprint再接上连接器,然后再经过cable在远端的SMA头,划分开来就是如下图所示的几部分:对于传输线和BGA,连接器结构,其实我们需要用不同精度的仿真工具和建模方法去执行,如下图。

其中连接器的模型和cable的参数都是通过厂商拿到,我们主要做的部分是前面的BGA,走线和连接器footprint的仿真。

大家觉得难度如何,频域校准时域校准哪个比较难?频域的插损,回损,模态转换呢?

首先本文也有做一些仿真前各项校准难度预期,如下图,看看和大家想的是不是一样哈。

的确,频域和时域各有不同的难度系数,频域的插损和时域的TDT总体来说容易点,频域的回损和时域的TDR(也就是阻抗)稍难,最难的是频域和时域模态?get到了吗??没get到也没关系,下面会详细解释为什么难度不一样。

我们先说结构相对简单的传输线,加工因素方面会把PCB走线变成梯形的样子,我们称为蚀刻因子,这个对于我们去建模有一定的难度,不太容易得到等效的线宽。同时加工还存在流胶的影响,介质厚度会和设计值不同,我们如何去等效?

至于传输线的建模仿真,我们是用单极点模型(容易建模,但高频精度差)还是多极点模型(建模复杂)?对铜箔粗糙度我们是使用huray模型还是hammerstad模型也是很困扰的事情。

那回损方面呢?为什么会比插损难校准呢,主要就是因为BGA和连接器的过孔,我们知道加工有钻孔公差和背钻的stub公差,8mil的孔加工完不会就是8mil,你设计时是想让过孔没有stub,但是加工出来会有2-12mil。另外走线的蚀刻因子也不好估计。

加上前面说的传输线的蚀刻因子和介质厚度的流胶,可能你的测试结果会像下面这样。

这样的情况,你的仿真又应该怎样去校准呢?

另外下面这一点,我们很少去关注,那就是器件输出的工艺温度的不同也会影响阻抗。

所以,可能不同批次生产出来的这条链路,它们的TDR测试可能会是下面的曲线:

另外模态转换的校准为什么最难,看下图框框你就会明白,走线的拐弯,绕线补偿,地过孔的对称都不容易百分百去模拟,因此很难把共模和差模转换校准好。

所以很明显我们要解决的问题是下面这样:

那我们要做些什么去实现这一切呢?

我们可能需要去调节我们粗糙度的模型参数:

也可能需要根据PCB厂家反馈或者切片去得到实际的叠层来确保加工后的传输线的阻抗:

也可能需要根据实际的测试方法去修正我们建模端口的添加方法:

甚至我们还需要判断下厂家提供的连接器和cable的模型是不是就真的和测试情况一样:

然后完成上面的一切之后,你会发现你的校准精度可以做到非常高:

好,大概把这篇文章的精华分享完了,可能有部分人还没想明白,到底做这么一个仿真测试校准意义在哪呢?我们都喜欢举一反三,实际上每款设计,高速链路都不会是一样的,而且速率越高,设计对信号影响越大。如果我们先把这个“一”做出来了,以后大家想去搞自己产品的“三”就会很容易,同时我们这个“一”是得到测试的验证,精度是非常高的,那么对于你们在前期如何规划自己的“三”也会有极大的信心。

编辑:hfy

-

pcb

+关注

关注

4333文章

23223浏览量

401854 -

连接器

+关注

关注

98文章

14824浏览量

137781 -

走线

+关注

关注

3文章

117浏览量

24034 -

仿真测试

+关注

关注

0文章

92浏览量

11392

发布评论请先 登录

相关推荐

客户&案例分享 | LDA Technologies 通过Samtec AcceleRate® 线缆实现100 G+传输速率

AMD Versal自适应SoC GTM如何用XSIM仿真和观察PAM4信号

400G QSFP-DD ER4 光模块概述

明明我说的是25G信号,你却让我看12.5G的损耗?

设计仿真 基于VTD的AR-HUD仿真测试解决方案

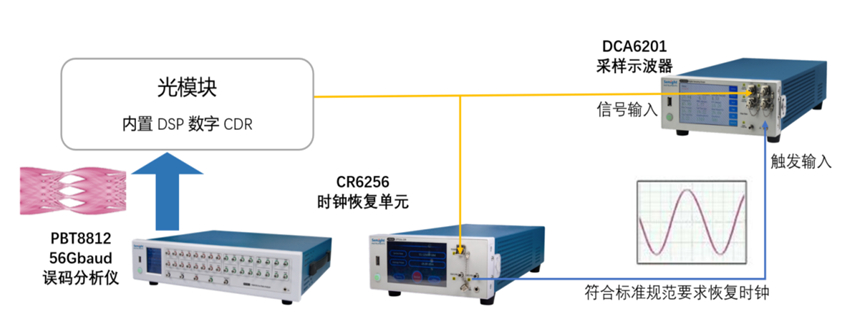

56Gbaud CR6256!400G/800G单多模光模块及接口的时钟提取

古希腊掌管224G 的神 | Samtec 224G PAM4 高速互连大合集!

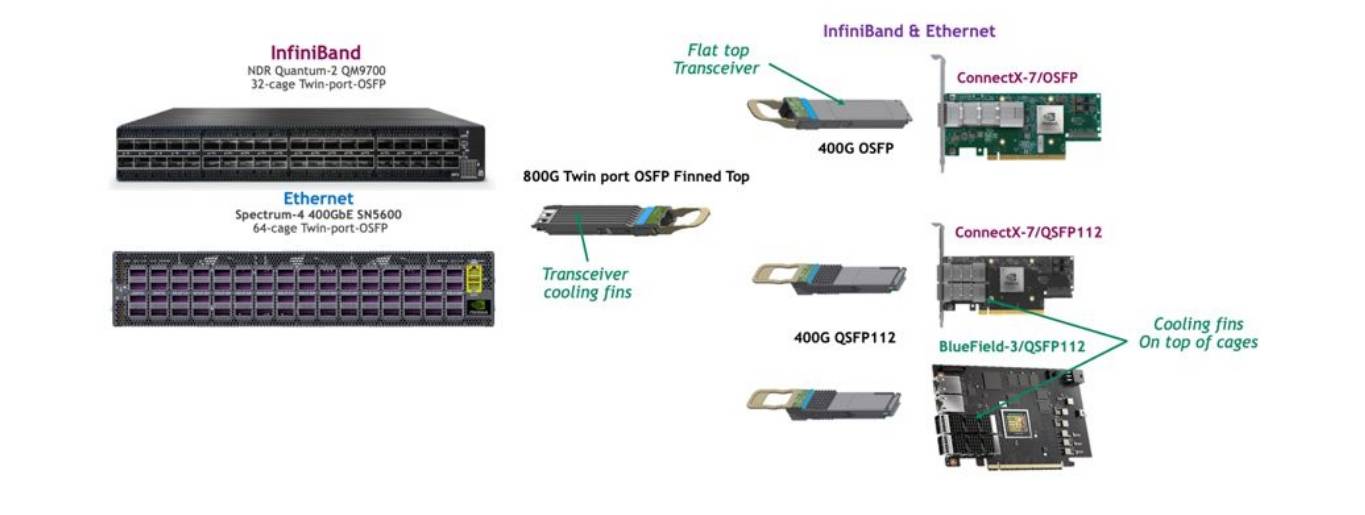

英伟达400G 100G-PAM4 OSFP和QSFP112光模块在交换机上的验证与优化

SG3225EEN在PAM4光模块和400G,QSFP-DD光模块中的应用

高速板材为什么贵?单看这一点你们就明白了!

AMD硅芯片设计中112G PAM4串扰优化分析

25G-NRZ/56G-PAM4高速链路的仿真测试的校准拟合方案

25G-NRZ/56G-PAM4高速链路的仿真测试的校准拟合方案

评论