最近小编去外面的世界走了一圈,和大家进行了多场面对面的技术交流会。粉丝们很热情,水平也很高,虽然时间匆忙,但是也获益良多;回来后决定重拾“荒废”一段时间的学业,结合不少朋友的问题和最近高速先生的文章主题继续讲讲PCB设计与加工误差的这些事。

如果让你叠一个8层板,最常规的会叠成下图左边这样:有两个内层走线,其中有一个走线层上下都参考地,属于比较好的走线层,另外一个需要有一面参考电源,很多人总是会觉得差一丢丢的感觉(问他们差在哪,他们又不一定说得出来,关于参考电源的差异,这里不展开讨论)。那如果发现2个内层不够,需要3个内层走线的话,你可能只能像下图右边这么叠,在同样层数的情况下,多一个内层就只能少一个地层,那就会出现两个平面层夹2个信号层,这就是我们所说的双带线结构,下图右边红色框框所示。

在我们日常的PCB设计中,对于双带线,我们除了要关心同层走线之间的串扰之外,还要关心相邻层走线的串扰。

下面是两对线宽为4.5mil,线间距为9mil的差分线,它们和参考平面共同组成了一组双带线的结构(下面红色和绿色的差分线,黄色是参考平面)。

一些基础的串扰理论告诉我们,如果双带线平行走线长度过长的话,串扰会比较严重,我们用这个双带线的模型做一下仿真,看看到底串扰能严重到什么程度哈。我们定义差分线到各自参考平面的距离为H,相邻层的距离为2H,平行走线长度为1000mil。

在上图的这种情况下,两对差分线的串扰(由于是内层走线,我们更关心近端串扰,下面的分析也都是指近端串扰)是这样的:我们可以看到,串扰是比较严重的,接近15dB了。

如果在垂直方向的距离2H固定的情况下,我们可以通过拉开它们的水平距离达到减小串扰的目的,例如可以拉开到下面的这两种情况。

从仿真结果上看,拉开到相切到一倍线宽的距离时对串扰就会有明显的改善效果,串扰可以从-15dB到非常好的-50dB。

但是拉开到一倍线宽线距对布线来说会很浪费空间,降低布线的密度。另外大家有没有有想过,按从下图左边完全重合到右边相切逐渐拉开的话,串扰会是怎样的一个变化过程呢?是不是从左到右越错开串扰越小呢?

实际上很多事情真的不能靠感觉来判断哈,我们通过仿真,串扰结果是这样的:

除了上面说的重合和相切的串扰外,如果细致分析下面三种情况,分别往右边拉开水平距离时,它们的串扰结果是这样的:

大家觉得上图的串扰结果从高到低分别是上图的从左到右,是不是越往右边拉开,串扰越小呢?

但是事情的真相是这样的:当走线移到接近互相错开的时候,这时的串扰是极小的,甚至接近拉开一倍线宽线距的设计。

至于原理,简单来说是这样:当攻击差分线和受害差分线互相错开到一定距离的时候,两根单端的攻击线对每根单端的受害线的串扰都有最大程度的抵消,因此总会在一个错开的位置有串扰的最低值,再向左向右的过程,抵消的比例都会逐渐减小,因此串扰又会大起来了,当然到拉开出相切以上的距离,就肯定是越来越小了。

上图几个情况的串扰值如下所示:

单从理想的设计层面,如果把两对差分线互相错开,大概错开到中间的位置,串扰的效果就会非常的好,然后也会很节省布线的空间,看起来真是一个很不错的设计。

编辑:hfy

-

PCB设计

+关注

关注

394文章

4711浏览量

86997

发布评论请先 登录

相关推荐

[讨论]PCB设计面临的新挑战

PCB设计后期处理概述

(免费资料+福利)多层高速pcb设计中那些不得不说的事

(免费资料分享)多层高速pcb设计中那些不得不说的事(包含DDR、眼图、刚柔板、传输线等等内容)

【系列直播免费分享】多层高速pcb设计中那些不得不说的事

(免费资料+福利)多层高速pcb设计中那些不得不说的事(DDR、眼图、刚柔板,传输线等等内容)

[(8小时+免费课程分享)多层高速pcb设计中那些不得不说的事(包含DDR、眼图、刚柔板、传输线等等内容)

(免费分享)多层高速pcb设计中那些不得不说的事(包含DDR、眼图、刚柔板、传输线等等内容)

谈谈PCB设计电子与机械之间的那些事

PCB设计有哪些误区PCB设计的十大误区上部分内有下部分链接

SMT贴片加工对PCB设计的要求

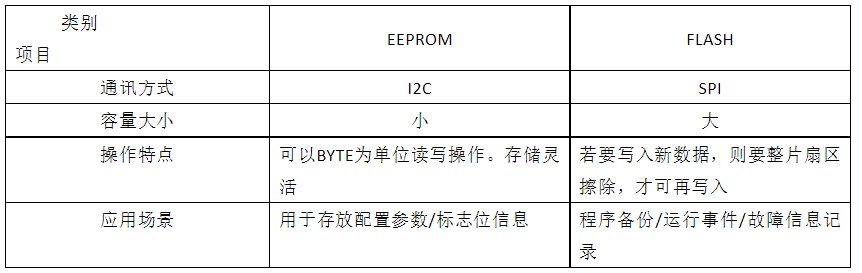

说说EEPROM和FLASH的那些事

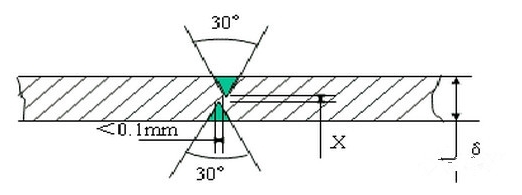

谈谈PCB设计与加工误差的那些事

谈谈PCB设计与加工误差的那些事

评论