作为硬件/PCB/SI工程师一个基础性的日常操作,从板材选型,PP选型,铜箔选型,然后分配厚度,对于设计叠层相信有经验的粉丝们都get得七七八八了。但是设计中的这一点差别你们都有考虑过吗???

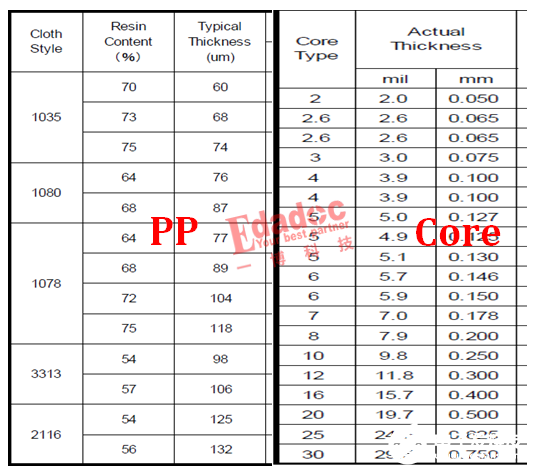

常规的叠层操作方法我们都已经懂了,无非就是看长度吃饭。长度决定我们要的板材级别,然后PP尽量选好的,也就是尽量不要选单张106或者1080(不要再问高速先生为什么了哈,我们会生气的)。然后选好PP/core的厚度之后就把对应阻抗的线宽/线距算出来,交给板厂确认一下就基本OK了。

但是呢,有一个很重要的点不知道你们在设计叠层,或者看别人的叠层时有没有发现。好吧,高速先生给你们举个例子说明下咯。

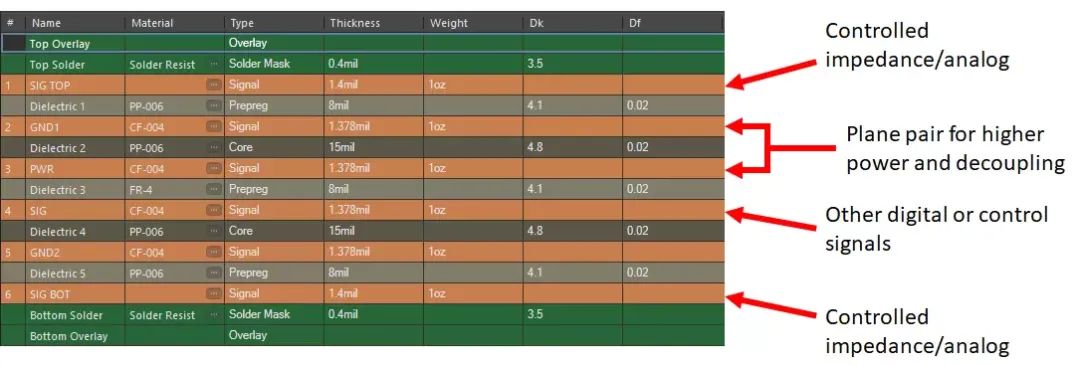

假设我们在做一个很厚的背板的叠层设计时,通过分配走线层数之后得到一个地-信号层-地的组合能分到15mil,就像下图所示:

打开你们的PP和CORE的line-up之后,问题来了,你们会怎么选择在上下两层去分配PP/core呢?

根据以上的参数会有很多种组合,例如3milPP-12mil Core,又或者5milPP-10mil Core,那么我们来选2种最极端的组合,如下所示:

这两种叠层有什么不一样吗?不就是用不一样的PP和CORE来凑够厚度吗?如果你们算阻抗的话,你就会发现它们最大的区别了。

时间关系我们已经大概帮你算出来了,这两者叠层的线宽线距是这样的:

说到了线宽不同,你们就会知道关于它的最大的秘密来了,那就是什么?你们大声的说出来!!!

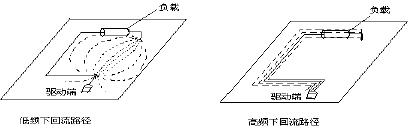

对,那就是损耗。如果同样是10inch的走线,4mil的线宽和6mil线宽的损耗在10GHz处其实可以差得很多。

对于走线很长或者裕量很紧张的情况,其实这个无形的差别就显得非常的重要了。大家想一想,要是走线走到了20inch时,然后速率在25Gbps,那这个差距更大了。

一般按照我们高速先生的风格,写到这里就基本上要结束了。但是这个剧情还会有反转,本来想留到答题的时候再进行分析,但是粉丝们可能知道我们高速先生一贯的套路,答题也就是回答下网友的问题,并没有周一正文那么经典,因此干脆就把反转的剧情提前剧透了。

大家有没有想过,6mil会比4mil线宽要宽(这不是fei话吗?)。我们知道板子的空间是一定的,如果一对差分线占用的2W+S多了,那么差分对与差分对的间距就近了,我们在保证两种情况下差分对间中心距一样的前提下再进行仿真,当然我们要看的就是两种情况下的串扰结果了。

剧情果然反转了,6mil线宽在串扰上是差的。细思一下当然也很正常,线宽宽了,空间用到这里去了,那么对间的间距自然就得近咯,因为空间是确定的,就看你是用到线宽还是间距那里咯。好,这篇文章到这里就真正结束了。

编辑:hfy

-

pcb

+关注

关注

4319文章

23105浏览量

398074 -

背板

+关注

关注

0文章

28浏览量

16492 -

叠层

+关注

关注

0文章

28浏览量

9856

发布评论请先 登录

相关推荐

6层PCB叠层设计指南

关于PCB技术中背板的叠层设计

关于PCB技术中背板的叠层设计

评论