了找出误码的根本原因,抖动分析是最好的起点,但是在某些情况下,电源轨分析可以帮助找出真正的根本原因。为了深入了解比特错误,我们在时域和频域都研究了抖动和电源轨噪声。比较TIE频谱中的PJ(周期性抖动)频率和电源纹波频谱中的杂散,是识别由PDN(配电网络)引起的信号完整性问题的快速而准确的方法。

SI和PI助长错误

数字错误是由抖动和噪声引起的。噪声是信号幅度变化的广义术语。抖动是相对于数据速率时钟的比特转换时序变化,即所谓的时间间隔误差。抖动是由相位噪声和幅度噪声到抖动的转换引起的。抖动噪声带来了串扰,EMI(电磁干扰)和随机噪声的问题。

信号完整性分析着眼于BER(误码率),着眼于发送器,参考时钟,通道和接收器的性能。电源完整性着眼于PDN提供恒定电压电源轨和低阻抗返回路径的能力。SI和PI具有广泛的相互依赖性。PDN会引起噪声和抖动。电路设计和组件(芯片封装,引脚,走线,过孔,连接器)会影响PDN的阻抗,进而影响供电质量。

从眼图开始调试SI问题

硬件调试可以从眼图分析开始。眼图由相对于时钟的重叠波形组成,图1。

图1:眼图,带遮罩测试,顶部,对应的波形,底部。

交叉点的水平宽度表示抖动,眼睛的顶部和底部的垂直宽度表示噪声。睁大眼睛应该对应于低BER。如果BER太高,下一步就是执行抖动分析。图2将抖动的分解图映射到其组件和子组件,图3显示了“抖动摘要”测量值,包括浴盆图,眼图,TIE频谱和直方图,抖动测量结果和波形。

图2:抖动分解为其各个组成部分。

图3:抖动摘要屏幕快照,从左上方顺时针方向:浴缸图,眼图,TIE频谱,抖动分析结果,波形,TIE直方图。

抖动的分解开始于将TIE分布分为其随机和确定性分量RJ(随机抖动)和DJ(确定性抖动)。DJ进一步分为与数据中的比特序列相关的抖动-DDJ(与数据有关的抖动)和与PJ(周期性抖动)等不相关的抖动。

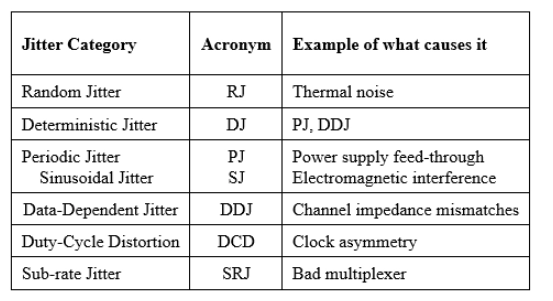

眼图上的广泛交叉可以指示RJ。看起来由许多几乎不同的线组成的眼睛可能表示DDJ,可能是由于信号路径中的阻抗不匹配所致。需要更详细的测量来确定可以指示硬件错误的抖动类型:TIE,RJ,DJ,DDJ,PJ,TJ(总抖动),EH(眼高),EW(眼宽),眼高和眼低的。表1列出了不同类型的抖动和一些原因。电源轨纹波是PJ有时甚至是RJ的常见原因。

表1:抖动测量以及常见原因示例。

表1:抖动测量以及常见原因示例。

抖动和配电网络

PDN的工作是维持恒定电压并为系统中的组件提供足够的电流。它会影响主动或被动每个元素的性能。PDN包括整个系统,不仅包括DC-DC转换器和内部芯片电源分配,还包括每个互连,走线,过孔,连接器,电容器,封装,引脚和球栅。

纹波对随机和周期性抖动的影响

电源轨噪声通常称为纹波,通常为几毫伏。要在GHz频率上准确测量电源轨上的mV噪声,就需要具有高DC阻抗的高带宽探头,该探头在高频下充当50Ω传输线。为此专门设计了电源导轨探头。

开关电源通过在低功耗导通和关断状态之间连续切换来调节电源轨和返回路径(又称“接地”)之间的电压。不幸的是,驱动开关元件的脉冲会引起“开关噪声”并引起PJ。

开关以固定频率发生,应将其记录在DC-DC转换器的数据手册中。如果图4左上方的纹波频谱和紧靠其下方的TIE频谱在开关频率或开关频率的谐波处都有杂散,那么我们就知道了源头并可以解决设计问题。请注意,图4中红色标记处出现大的重合杂散。TIE频谱右边的TIE直方图在一个频率上具有正弦抖动分布(马蹄形)PJ。

图4:频谱视图左上方的电源轨纹波,以及其下方的TIE频谱,以及信号和电源轨波形以及TIE直方图。

电源会引入随机噪声,从而导致RJ。电源轨随机噪声显示为图4左上方“频谱视图”图的本底噪声。RJ由TIE频谱的本底噪声计算得出。在此示例中,由于电源纹波引起的随机噪声非常低,RJ很小,约为0.84 ps。

PJ和地面弹跳

在逻辑转换期间,发送器和接收器从PDN获取或吸收电流。当多个信号同时在两个电平之间切换时,它们可以从电源导轨和/或接地板上沉积或去除大量电荷。短期引入电荷密度会改变导体两端共同接地的电压。所产生的电压变化称为接地反弹或等效的同时开关噪声(SSN)。

在继续之前,我们应该澄清两件事。首先,“接地”是指返回路径的所需公共参考电压,通常将其定义为0V。第二,“同时”是指组件在其上升/下降时间间隔内产生或吸收电荷。下降时间重叠。

SSN在时域中看起来是随机的,但在频域中却不是。数据信号由许多频率分量组成-基频或奈奎斯特频率,也许多达两个高次谐波,再加上连续相同位的次谐波。这些频率中的任何一个都可能发生同时切换。因此,SSN是具有许多低振幅杂散的周期性噪声,会引起PJ。

为了确认PJ是由SSN引起的,请将图5左上方的电源轨频谱与正下方的TIE频谱进行比较。在两个频谱中以相同频率出现的高振幅杂散表明SSN的PJ贡献很大。

图5:(a)电源轨纹波频谱和(b)TIE /抖动频谱。

概括

信号完整性和电源完整性是一个反馈回路。网络中的每个元素,每条走线,过孔,连接器,引脚,封装等都会影响PDN阻抗和每个通道的阻抗,并且每个有源组件都会改变电源轨和接地层的电压。

眼图可以告诉我们很多有关信号完整性的信息,但很少帮助我们识别特定问题。对TIE分布的分析将抖动分解为一些组件,这些组件提供了问题所在的线索。高RJ通常意味着时钟嘈杂,但也可能指示电源产生随机噪声。

PJ可能指示时钟故障,电源开关噪声或接地反弹/ SSN。将电源轨纹波频谱与TIE频谱进行比较可以分两步解决问题。TIE频谱中的杂散表示电源轨频谱中没有任何相应的杂散,表示时钟。两个频谱中相同频率的一个或两个杂散表示电源开关噪声;两个光谱共有的大量杂散表示SSN。在每种情况下,将抖动和功率分析结合起来可以解决其他困难的问题。

信号完整性和电源完整性通常被认为是不同的学科,但是我们已经发现,发现与高抖动相关的问题需要对两者都进行理解。

编辑:hfy

-

信号完整性

+关注

关注

68文章

1418浏览量

95829 -

PDN

+关注

关注

0文章

83浏览量

22822

发布评论请先 登录

相关推荐

数字产品中电源轨噪声如何影响系统中时钟抖动

电源轨的封装电感过大怎么办

电源轨是什么,电源轨不同列之间导通吗

OPA2188单电源时最大输出3.7V,不能轨至轨输出怎么解决?

OPA4350-DIE高速、单电源、轨到轨运算放大器数据表

OPA2834 50MHz、负电源轨输入、轨至轨输出、电压反馈放大器数据表

如何通过电源轨分析理解电源轨噪声与抖动

如何通过电源轨分析理解电源轨噪声与抖动

评论