今天要给大家分享的文章如下,这次的题目很容易读懂,就叫DDR4通道里,过孔的stub对信号质量的影响分析。

那主要肯定是讲过孔stub(残桩)对DDR4的影响咯。首先呢作者对DDR4的信号质量做了一些前提的判定和分析,例如要求通道的插损谐振频率点要大于5倍的时钟频率,按本文分析的3200Mbps来说的话,时钟是1.6GHz,因此要求的谐振频率点必须大于8GHz。

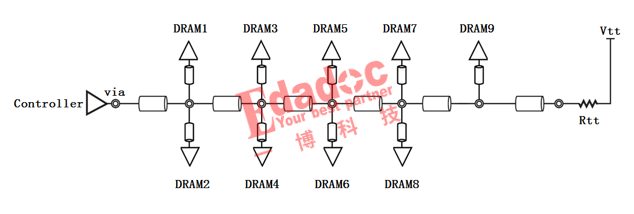

好,立马进入正题,看看作者是如何分情况对DDR4通道进行分析的。他们主要对3种不同的场景进行分析,一是颗粒版本的表层走线,那肯定就是没有过孔stub了;二是颗粒版本的内层走线,有过孔stub的情况;三是Dimm版本的内层走线,不仅有过孔stub,还包括了Dimm条连接器这个阻抗不匹配的点。下图就是三种不同case的示意图。

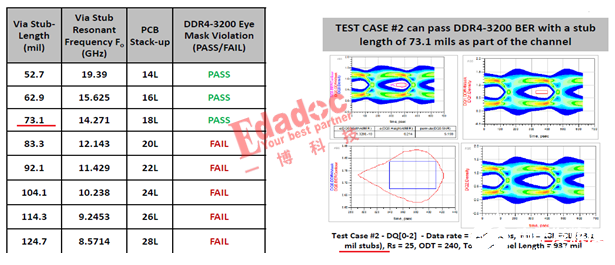

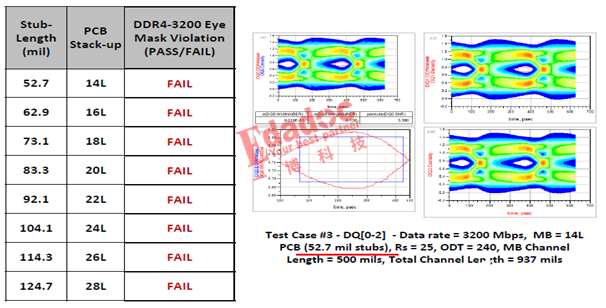

既然是详细的研究过孔stub对信号质量的影响程度,那肯定是需要不同的过孔stub长度的比较了。于是本文做了非常非常多的叠层进行分析,过孔stub从14层的52.7mil(内层走线都以L3层出线,分析不同叠层的最长过孔stub的情况)到28层的124.7mil。几乎涵盖了99%的应用需求。

另外,作者还给出了所使用的过孔的一些参数情况和进行3D仿真的模型。

好,我们一起来看分析的结果吧。

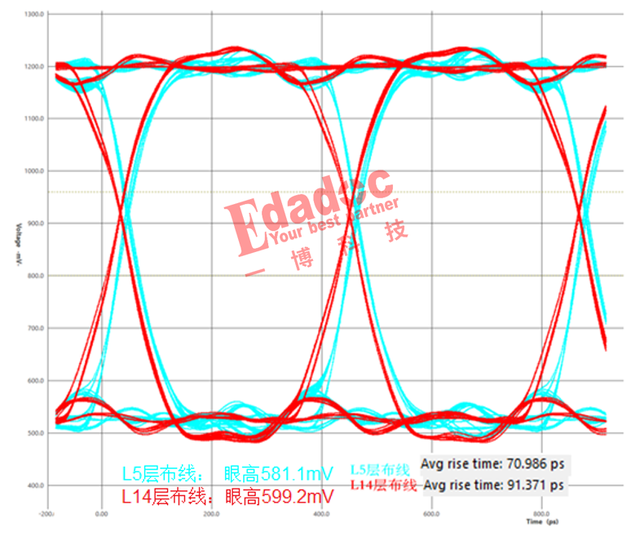

首先case1,表层走线,没有过孔stub的情况下,结果比较简单也比较明确,在3200Mbps的速率下信号质量比较好,在-16次方的严格误码率下,眼图仍有比较大的裕量。

那么进行case2的分析了。可以看到,过孔stub长度在73.1mil的时候是一个临界点,这个时候眼图刚好压在-16次方误码率的mask,再往下的话就不能满足该误码率的标准了。

那么case3呢,加上一个dimm条连接器之后的情况又会是如何呢?恩!是的,想到了会变差,但是,是不是没想到差成这样??

可以看到在Dimm条应用的情况下,50mil以上的stub都是有风险的,过不了-16次方误码率的标准。

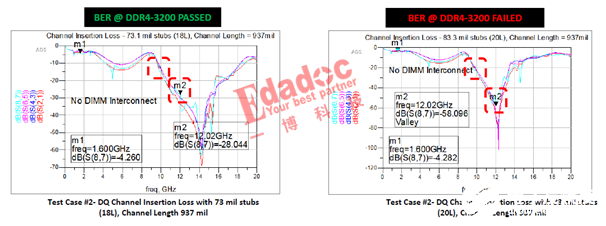

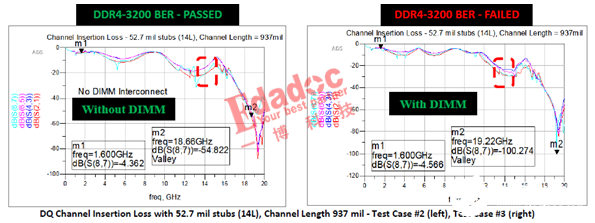

进行完眼图的分析后,我们再来看看频域的分析,插损情况的对比。

首先进行了case2的73mil临界点和83mil不过的两种情况的对比。可以看到虽然只是10mil的差别,但是从下图红色框标出的几个点的损耗情况都有比较大的差异,几乎有30dB的区别。

而对比53mil的过孔stub长度下颗粒版本和Dimm条应用的情况如下。可以看到Dimm条模式下也会有接近10dB的差异了。

最后,作者给出了在不同过孔stub情况下的成功率的预测,非常的直观明了。

编辑:hfy

-

DDR4

+关注

关注

12文章

351浏览量

43375 -

信号质量

+关注

关注

0文章

10浏览量

6988

发布评论请先 登录

PCB过孔STUB对DDRX地址信号的影响

DDR设计需要背钻吗

DDR4复位偏差要求是什么?

过孔STUB长,DDR信号“强”?

DDR4,什么是DDR4

DDR4技术有什么特点?如何采用ANSYS进行DDR4仿真?

DDR4协议

DDR4和DDR5规格之间的差异

浅谈Via stub在DDR4并行链路上的表现

0706线下活动 I DDR4/DDR5内存技术高速信号专题设计技术交流活动

DDR4通道中过孔 stub对信号质量的影响分析

DDR4通道中过孔 stub对信号质量的影响分析

评论